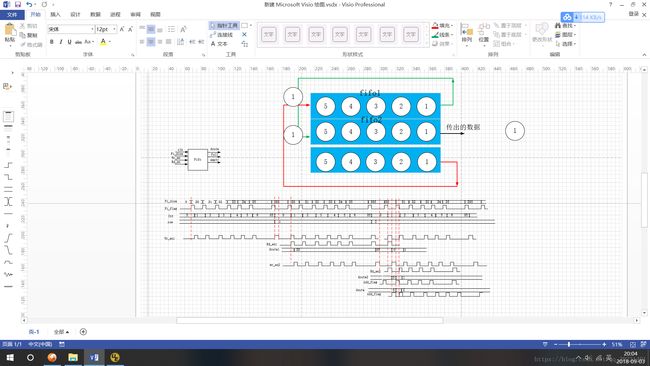

FPGA——双fifo的使用

利用双fifo实现3个数值相加。实现10排0-85 每三排的数实现竖直相加。

module fifo(

input wire clk ,

input wire rst_n ,

input wire[7:0] dina ,

input wire wr_en ,

output reg[7:0] douta ,

output reg flag ,

output wire full1 ,

output wire empty1 ,

output wire full2 ,

output wire empty2

);

reg[6:0] cnt_r;

reg rd_en1;

reg rd_en2;

reg wr_en1;

reg wr_en2;

reg[3:0] row;

wire[7:0] douta1;

wire[7:0] douta2;

parameter ROW_MAX=10;

parameter CNT_R_MAX=85;

always@(posedge clk or negedge rst_n)

if(rst_n == 0)

cnt_r <= 7’b0;

else if (cnt_r == CNT_R_MAX&&wr_en == 1)

cnt_r<= 7’b0;

else if(wr_en==1)

cnt_r <= cnt_r +7’b1;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

row <= 0;

else if( row == ROW_MAX)

row <= 0;

else if(cnt_r == CNT_R_MAX&&wr_en == 1)

row <= row + 1;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

wr_en1 <= 0;

else if(row>=0&&row<=ROW_MAX-2)

wr_en1 <= wr_en;

else

wr_en1 <= 0;

always@(posedge clk or negedge rst_n)

if(rst_n== 0)

rd_en1 <= 0;

else if(row>=1&&row<=ROW_MAX-1)

rd_en1 <= wr_en;

else

rd_en1 <= 0;

reg wr_en2_dly;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

wr_en2_dly <= 0;

else if(row>=1&&row

else

wr_en2_dly <= 0;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

wr_en2 <= 0;

else

wr_en2 <=wr_en2_dly;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

rd_en2 <= 0;

else if(row>=2&&row<=ROW_MAX-1)

rd_en2 <= wr_en;

else

rd_en2 <= 0;

reg add_flag;

always@(posedge clk or negedge rst_n)

if(rst_n== 0)

add_flag <= 0;

else if(row>=2)

add_flag <=rd_en2;

else

add_flag <= 0;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

douta <= 0;

else if(add_flag == 1)

douta <= douta1+douta2+dina;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

flag <= 0;

else

flag <=add_flag;

fifo_generator_v9_3 fifo_generator_v9_3_1_inst (

.clk(clk), // input clk

.rst(rst_n), // input rst

.din(dina), // input [7 : 0] din

.wr_en(wr_en1), // input wr_en

.rd_en(rd_en1), // input rd_en

.dout(douta1), // output [7 : 0] dout

.full(full1), // output full

.empty(empty1) // output empty

);

fifo_generator_v9_3 fifo_generator_v9_3_2_inst (

.clk(clk), // input clk

.rst(rst_n), // input rst

.din(douta1), // input [7 : 0] din

.wr_en(wr_en2), // input wr_en

.rd_en(rd_en2), // input rd_en

.dout(douta2), // output [7 : 0] dout

.full(full2), // output full

.empty(empty2) // output empty

);

endmodule