- 系统学习Python——并发模型和异步编程:进程、线程和GIL

分类目录:《系统学习Python》总目录在文章《并发模型和异步编程:基础知识》我们简单介绍了Python中的进程、线程和协程。本文就着重介绍Python中的进程、线程和GIL的关系。Python解释器的每个实例都是一个进程。使用multiprocessing或concurrent.futures库可以启动额外的Python进程。Python的subprocess库用于启动运行外部程序(不管使用何种

- C++11堆操作深度解析:std::is_heap与std::is_heap_until原理解析与实践

文章目录堆结构基础与函数接口堆的核心性质函数签名与核心接口std::is_heapstd::is_heap_until实现原理深度剖析std::is_heap的验证逻辑std::is_heap_until的定位策略算法优化细节代码实践与案例分析基础用法演示自定义比较器实现最小堆检查边缘情况处理性能分析与实际应用时间复杂度对比典型应用场景与手动实现的对比注意事项与最佳实践迭代器要求比较器设计C++标

- Flask框架入门:快速搭建轻量级Python网页应用

「已注销」

python-AIpython基础网站网络pythonflask后端

转载:Flask框架入门:快速搭建轻量级Python网页应用1.Flask基础Flask是一个使用Python编写的轻量级Web应用框架。它的设计目标是让Web开发变得快速简单,同时保持应用的灵活性。Flask依赖于两个外部库:Werkzeug和Jinja2,Werkzeug作为WSGI工具包处理Web服务的底层细节,Jinja2作为模板引擎渲染模板。安装Flask非常简单,可以使用pip安装命令

- C++ 11 Lambda表达式和min_element()与max_element()的使用_c++ lamda函数 min_element((1)

2401_84976182

程序员c语言c++学习

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上CC++开发知识点,真正体系化!由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新如果你需要这些资料,可以戳这里获取#include#include#includeusingnamespacestd;boolcmp(int

- 冒泡、选择、插入排序:三大基础排序算法深度解析(C语言实现)

xienda

算法排序算法数据结构

在算法学习道路上,排序算法是每位程序员必须掌握的基石。本文将深入解析冒泡排序、选择排序和插入排序这三种基础排序算法,通过C语言代码实现和对比分析,帮助读者彻底理解它们的差异与应用场景。算法原理与代码实现1.冒泡排序(BubbleSort)工作原理:通过重复比较相邻元素,将较大元素逐步"冒泡"到数组末尾。voidbubbleSort(intarr[],intn){ for(inti=0;iarr[

- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

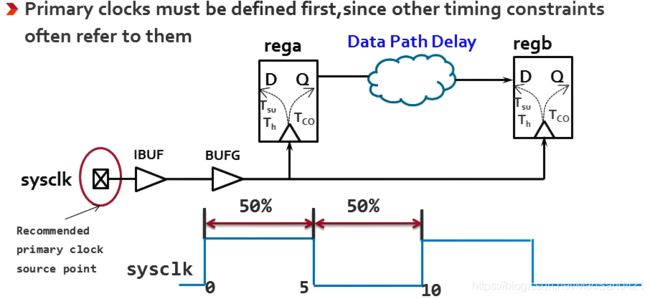

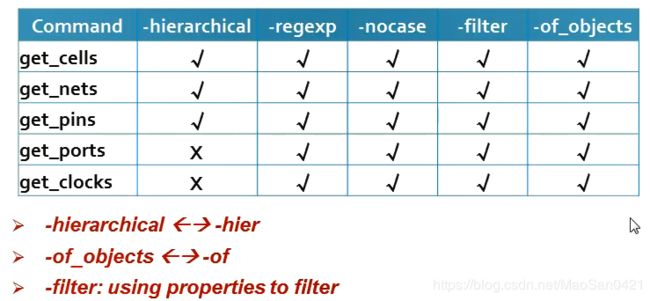

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- PyTorch & TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)

阿牛的药铺

算法移植部署pytorchtensorflowfpga开发

PyTorch&TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)引言:为什么算法移植工程师必须掌握框架基础?针对光学类产品算法FPGA移植岗位需求(如可见光/红外图像处理),深度学习框架是算法落地的"桥梁"——既要用PyTorch/TensorFlow验证算法可行性,又要将训练好的模型(如CNN、目标检测)转换为FPGA可部署的格式(ONNX、TFLite)。本文采用"

- Python之七彩花朵代码实现

PlutoZuo

Pythonpython开发语言

Python之七彩花朵代码实现文章目录Python之七彩花朵代码实现下面是一个简单的使用Python的七彩花朵。这个示例只是一个简单的版本,没有很多高级功能,但它可以作为一个起点,你可以在此基础上添加更多功能。importturtleastuimportrandomasraimportmathtu.setup(1.0,1.0)t=tu.Pen()t.ht()colors=['red','skybl

- (Python基础篇)了解和使用分支结构

EternityArt

基础篇python

目录一、引言二、Python分支结构的类型与语法(一)if语句(单分支)(二)if-else语句(双分支)(三)if-elif-else语句(多分支)三、分支结构的应用场景(一)提示用户输入用户名,然后再提示输入密码,如果用户名是“admin”并且密码是“88888”则提示正确,否则,如果用户名不是admin还提示用户用户名不存在,(二)提示用户输入用户名,然后再提示输入密码,如果用户名是“adm

- (Python基础篇)循环结构

EternityArt

基础篇python

一、什么是Python循环结构?循环结构是编程中重复执行代码块的机制。在Python中,循环允许你:1.迭代处理数据:遍历列表、字典、文件内容等。2.自动化重复任务:如批量处理数据、生成序列等。3.控制执行流程:根据条件决定是否继续或终止循环。二、为什么需要循环结构?假设你需要打印1到100的所有偶数:没有循环:需手动编写100行print()语句。print(0)print(2)print(4)

- (Python基础篇)字典的操作

EternityArt

基础篇python开发语言

一、引言在Python编程中,字典(Dictionary)是一种极具灵活性的数据结构,它通过“键-值对”(key-valuepair)的形式存储数据,如同现实生活中的字典——通过“词语(键)”快速查找“释义(值)”。相较于列表和元组的有序索引访问,字典的优势在于基于键的快速查找,这使得它在处理需要频繁通过唯一标识获取数据的场景中极为高效。掌握字典的操作,能让我们更高效地组织和管理复杂数据,是Pyt

- 基于架构的软件设计(Architecture-Based Software Design,ABSD)是一种以架构为核心的软件开发方法

ABSD方法与生命周期基于架构的软件设计(Architecture-BasedSoftwareDesign,ABSD)是一种以架构为核心的软件开发方法,强调在开发的各个阶段都要以架构为中心,确保系统的整体结构和质量属性得到有效管理。ABSD方法是一个自顶向下、递归细化的过程,软件系统的架构通过该方法得到细化,直到能产生软件构件和类。ABSD方法的三个基础功能的分解:使用基于模块的内聚和耦合技术,将

- Java大厂面试故事:谢飞机的互联网音视频场景技术面试全纪录(Spring Boot、MyBatis、Kafka、Redis、AI等)

来旺

Java场景面试宝典JavaSpringBootMyBatisKafkaRedis微服务AI

Java大厂面试故事:谢飞机的互联网音视频场景技术面试全纪录(SpringBoot、MyBatis、Kafka、Redis、AI等)互联网大厂技术面试不仅考察技术深度,更注重业务场景与系统设计能力。本篇以严肃面试官与“水货”程序员谢飞机的对话,带你体验音视频业务场景下的Java面试全过程,涵盖主流技术栈,并附详细答案解析,助你面试无忧。故事场景设定谢飞机是一名有趣但技术基础略显薄弱的程序员,这次应

- 利用技术分享提升个人影响力

AI天才研究院

计算AI人工智能与大数据AI大模型企业级应用开发实战javapythonjavascriptkotlingolang架构人工智能大厂程序员硅基计算碳基计算认知计算生物计算深度学习神经网络大数据AIGCAGILLM系统架构设计软件哲学Agent程序员实现财富自由

《利用技术分享提升个人影响力》关键词:技术分享、个人品牌、影响力、内容创作、互动反馈、持续成长摘要:本文将深入探讨技术分享在个人发展中的重要作用,通过详细分析技术分享的意义、平台选择、内容创作、互动反馈及个人影响力提升策略,帮助读者掌握利用技术分享提升个人影响力的实用方法。第一部分:引言与基础第1章:技术分享的意义与价值1.1.1技术分享的历史与发展技术分享作为一种知识传播的方式,其历史可以追溯到

- RocketMQ 基础教程-应用篇-死信队列

码炫课堂-码哥

rocketmq专题rocketmqjava

作者简介:大家好,我是smart哥,前中兴通讯、美团架构师,现某互联网公司CTO联系qq:184480602,加我进群,大家一起学习,一起进步,一起对抗互联网寒冬学习必须往深处挖,挖的越深,基础越扎实!阶段1、深入多线程阶段2、深入多线程设计模式阶段3、深入juc源码解析阶段4、深入jdk其余源码解析

- ssrf漏洞复现

ξ流ぁ星ぷ132

安全

目录基础环境查看phpinfo发现线索探测端口+gopher协议基础环境这里发现一些基础协议呗过滤掉了。但是有个提示的info,于是先看看查看phpinfo发现线索发现这台主机的地址了,于是猜测这个网段应该还有其他主机,试了一下172.21.0.1:80172.21.0.3:80果然如下(0.1是陷阱就不浪费时间了,)探测端口+gopher协议然后对这个172.21.0.3这个主机探测端口发现63

- NGS测序基础梳理01-文库构建(Library Preparation)

qq_21478261

#生物信息生物学

本文介绍Illumina测序平台文库构建(LibraryPreparation)步骤,文库结构。写作时间:2020.05。推荐阅读:10W字《Python可视化教程1.0》来了!一份由公众号「pythonic生物人」精心制作的PythonMatplotlib可视化系统教程,105页PDFhttps://mp.weixin.qq.com/s/QaSmucuVsS_DR-klfpE3-Q10W字《Rg

- NGS测序基础梳理02-簇生成(Cluster Generation)及flow cell介绍

qq_21478261

#生物信息生物信息学

本文图解Illumina测序平台,flowcell表面簇生成(ClusterGeneration)过程。写作时间:2020,有问题可留言或者我的公众号。本文将了解到什么?1flowcell2簇生成为何要进行簇生成?簇生成步骤1)文库与flowcell表面P5杂交与互补链合成2)双链变性3)桥式PCR扩增4)反链切除5)DNA链3'封闭参考资料:1flowcell为何要先介绍flowcell?因为簇

- JavaScript 基础09:Web APIs——日期对象、DOM节点

梦想当全栈

JavaScriptjavascript前端开发语言

JavaScript基础09:WebAPIs——日期对象、DOM节点进一步学习DOM相关知识,实现可交互的网页特效能够插入、删除和替换元素节点。能够依据元素节点关系查找节点。一、日期对象掌握Date日期对象的使用,动态获取当前计算机的时间。ECMAScript中内置了获取系统时间的对象Date,使用Date时与之前学习的内置对象console和Math不同,它需要借助new关键字才能使用。1.实例

- 《Java前端开发全栈指南:从Servlet到现代框架实战》

前言在当今Web开发领域,Java依然是后端开发的主力语言,而随着前后端分离架构的普及,Java开发者也需要掌握前端技术栈。本文将全面介绍JavaWeb前端开发的核心技术,包括传统Servlet/JSP体系、现代前端框架集成方案,以及全栈开发的最佳实践。通过本文,您将了解如何构建现代化的JavaWeb应用前端界面。一、JavaWeb前端技术演进1.1传统技术栈Servlet:JavaWeb基础,处

- javaSE面试题---语法基础、面向对象、常用类、集合、多线程、文件和IO

yang_xiao_wu_

java面试开发语言javasejava基础多线程文件和IO

目录语法基础1.jdkjrejvm区别2.基本数据类型3.引用数据类型4.自动类型转换、强制类型转换5.常见的运算符6.&和&&区别7.++--在前和在后的区别8.+=有什么作用9.switch..case中switch支持哪些数据类型10.break和continue区别11.while和dowhile区别12.如何生成一个取值范围在[min,max]之间的随机数13.数组的长度如何获取?数组下

- 【unity编辑器开发与拓展EditorGUILayoyt和GUILayoyt】

死也不注释

Unity编辑器开发与拓展笔记unity编辑器游戏引擎

EditorGUILayout与GUILayout的核心区别及使用场景详解一、对比表特性GUILayoutEditorGUILayout命名空间UnityEngineUnityEditor使用场景运行时UI+编辑器扩展仅限编辑器扩展控件风格基础游戏风格(无编辑器优化)原生Unity编辑器风格布局复杂度基础流式布局高级自动布局(带标签对齐/间距优化)序列化支持❌不支持✅直接支持SerializedP

- 【证明】对极几何:本质矩阵内在性质

Powerful_QI

slam线性代数矩阵

--这是目录--1.本质矩阵内在性质表述2.预备知识2.1线性代数基础2.1.1奇异值与特征值的关系2.1.2矩阵加减单位阵后特征值的变化2.2引理:一个常用的矩阵变换3.证明1.本质矩阵内在性质表述 本质矩阵(EssentialMatrix)EEE是一个3阶方阵,满足E=t∧RE=t^{\land}RE=t∧R其中RRR为旋转矩阵,ttt为平移量,t∧t^{\land}t∧运算定义如下(参考了

- Python技能手册 - 模块module

金色牛神

Pythonpythonwindows开发语言

系列Python常用技能手册-基础语法Python常用技能手册-模块modulePython常用技能手册-包package目录module模块指什么typing数据类型int整数float浮点数str字符串bool布尔值TypeVar类型变量functools高阶函数工具functools.partial()函数偏置functools.lru_cache()函数缓存sorted排序列表排序元组排序

- LLM中 最后一个词语的表征(隐藏状态)通常会融合前面所有词语的信息吗?

ZhangJiQun&MXP

教学2024大模型以及算力2021AIpython机器学习算法深度学习人工智能

LLM中最后一个词语的表征(隐藏状态)通常会融合前面所有词语的信息吗?在大语言模型(LLM)中,最后一个词语的表征(隐藏状态)通常会融合前面所有词语的信息,这是由LLM的核心架构(以Transformer为基础)决定的,具体可以从以下角度理解:1.核心机制:自注意力(Self-Attention)的作用现代LLM(如GPT系列、Qwen等)均基于Transformer架构,其核心是自注意力机制。在

- Ubuntu基础(Python虚拟环境和Vue)

aaiier

ubuntupythonlinux

Python虚拟环境sudoaptinstallpython3python3-venv进入项目目录cdXXX创建虚拟环境python3-mvenvvenv激活虚拟环境sourcevenv/bin/activate退出虚拟环境deactivateVue安装Node.js和npm#安装Node.js和npm(Ubuntu默认仓库可能版本较旧,适合入门)sudoaptinstallnodejsnpm#验

- Flutter基础(前端教程⑥-按钮切换)

aaiier

Flutterflutter前端状态模式

1.假设你已有的两个表单组件(示例)//手机号注册表单(示例)classPhoneRegisterFormextendsStatelessWidget{@overrideWidgetbuild(BuildContextcontext){returnColumn(children:[TextField(decoration:InputDecoration(labelText:'手机号')),Text

- JVM与Spring Boot核心解析

AIHacksCash

Java场景面试宝典JavaJVMSpringBoot

我是廖志伟,一名Java开发工程师、《Java项目实战——深入理解大型互联网企业通用技术》(基础篇)、(进阶篇)、(架构篇)清华大学出版社签约作家、Java领域优质创作者、CSDN博客专家、阿里云专家博主、51CTO专家博主、产品软文专业写手、技术文章评审老师、技术类问卷调查设计师、幕后大佬社区创始人、开源项目贡献者。拥有多年一线研发和团队管理经验,研究过主流框架的底层源码(Spring、Spri

- flutter知识点

ZhDan91

flutter

#时隔4年了#4年前用flutter开发海外项目和医疗项目。绘制界面的语法与html还是较类似的。把这些封印的记忆和技术回顾一下,最开始是开发Android出身的,所以开发起flutter来依旧是用的androidstudio开发工具。整理下用到的知识点:整理来源:flutter面试题——基础篇(1)-CSDN博客1、Dart是单线程的。在单线程中以消息循环来运行的。其中敖汉两个任务队列。一个是微

- Java中的Tomcat,开启Web应用腾飞【基础版】

目录一、Tomcat初登场:揭开神秘面纱(一)啥是Tomcat(二)为啥要有Tomcat二、Tomcat的安装与启动:开启第一步(一)下载Tomcat(二)启动Tomcat三、Tomcat的目录结构:探秘内部布局(一)核心目录介绍(二)目录间的协同工作四、部署JavaWeb应用到Tomcat:让应用上线(一)打包Web应用为WAR文件(二)部署WAR文件到Tomcat五、Tomcat的配置优化:让

- Spring的注解积累

yijiesuifeng

spring注解

用注解来向Spring容器注册Bean。

需要在applicationContext.xml中注册:

<context:component-scan base-package=”pagkage1[,pagkage2,…,pagkageN]”/>。

如:在base-package指明一个包

<context:component-sc

- 传感器

百合不是茶

android传感器

android传感器的作用主要就是来获取数据,根据得到的数据来触发某种事件

下面就以重力传感器为例;

1,在onCreate中获得传感器服务

private SensorManager sm;// 获得系统的服务

private Sensor sensor;// 创建传感器实例

@Override

protected void

- [光磁与探测]金吕玉衣的意义

comsci

这是一个古代人的秘密:现在告诉大家

信不信由你们:

穿上金律玉衣的人,如果处于灵魂出窍的状态,可以飞到宇宙中去看星星

这就是为什么古代

- 精简的反序打印某个数

沐刃青蛟

打印

以前看到一些让求反序打印某个数的程序。

比如:输入123,输出321。

记得以前是告诉你是几位数的,当时就抓耳挠腮,完全没有思路。

似乎最后是用到%和/方法解决的。

而今突然想到一个简短的方法,就可以实现任意位数的反序打印(但是如果是首位数或者尾位数为0时就没有打印出来了)

代码如下:

long num, num1=0;

- PHP:6种方法获取文件的扩展名

IT独行者

PHP扩展名

PHP:6种方法获取文件的扩展名

1、字符串查找和截取的方法

1

$extension

=

substr

(

strrchr

(

$file

,

'.'

), 1);

2、字符串查找和截取的方法二

1

$extension

=

substr

- 面试111

文强chu

面试

1事务隔离级别有那些 ,事务特性是什么(问到一次)

2 spring aop 如何管理事务的,如何实现的。动态代理如何实现,jdk怎么实现动态代理的,ioc是怎么实现的,spring是单例还是多例,有那些初始化bean的方式,各有什么区别(经常问)

3 struts默认提供了那些拦截器 (一次)

4 过滤器和拦截器的区别 (频率也挺高)

5 final,finally final

- XML的四种解析方式

小桔子

domjdomdom4jsax

在平时工作中,难免会遇到把 XML 作为数据存储格式。面对目前种类繁多的解决方案,哪个最适合我们呢?在这篇文章中,我对这四种主流方案做一个不完全评测,仅仅针对遍历 XML 这块来测试,因为遍历 XML 是工作中使用最多的(至少我认为)。 预 备 测试环境: AMD 毒龙1.4G OC 1.5G、256M DDR333、Windows2000 Server

- wordpress中常见的操作

aichenglong

中文注册wordpress移除菜单

1 wordpress中使用中文名注册解决办法

1)使用插件

2)修改wp源代码

进入到wp-include/formatting.php文件中找到

function sanitize_user( $username, $strict = false

- 小飞飞学管理-1

alafqq

管理

项目管理的下午题,其实就在提出问题(挑刺),分析问题,解决问题。

今天我随意看下10年上半年的第一题。主要就是项目经理的提拨和培养。

结合我自己经历写下心得

对于公司选拔和培养项目经理的制度有什么毛病呢?

1,公司考察,选拔项目经理,只关注技术能力,而很少或没有关注管理方面的经验,能力。

2,公司对项目经理缺乏必要的项目管理知识和技能方面的培训。

3,公司对项目经理的工作缺乏进行指

- IO输入输出部分探讨

百合不是茶

IO

//文件处理 在处理文件输入输出时要引入java.IO这个包;

/*

1,运用File类对文件目录和属性进行操作

2,理解流,理解输入输出流的概念

3,使用字节/符流对文件进行读/写操作

4,了解标准的I/O

5,了解对象序列化

*/

//1,运用File类对文件目录和属性进行操作

//在工程中线创建一个text.txt

- getElementById的用法

bijian1013

element

getElementById是通过Id来设置/返回HTML标签的属性及调用其事件与方法。用这个方法基本上可以控制页面所有标签,条件很简单,就是给每个标签分配一个ID号。

返回具有指定ID属性值的第一个对象的一个引用。

语法:

&n

- 励志经典语录

bijian1013

励志人生

经典语录1:

哈佛有一个著名的理论:人的差别在于业余时间,而一个人的命运决定于晚上8点到10点之间。每晚抽出2个小时的时间用来阅读、进修、思考或参加有意的演讲、讨论,你会发现,你的人生正在发生改变,坚持数年之后,成功会向你招手。不要每天抱着QQ/MSN/游戏/电影/肥皂剧……奋斗到12点都舍不得休息,看就看一些励志的影视或者文章,不要当作消遣;学会思考人生,学会感悟人生

- [MongoDB学习笔记三]MongoDB分片

bit1129

mongodb

MongoDB的副本集(Replica Set)一方面解决了数据的备份和数据的可靠性问题,另一方面也提升了数据的读写性能。MongoDB分片(Sharding)则解决了数据的扩容问题,MongoDB作为云计算时代的分布式数据库,大容量数据存储,高效并发的数据存取,自动容错等是MongoDB的关键指标。

本篇介绍MongoDB的切片(Sharding)

1.何时需要分片

&nbs

- 【Spark八十三】BlockManager在Spark中的使用场景

bit1129

manager

1. Broadcast变量的存储,在HttpBroadcast类中可以知道

2. RDD通过CacheManager存储RDD中的数据,CacheManager也是通过BlockManager进行存储的

3. ShuffleMapTask得到的结果数据,是通过FileShuffleBlockManager进行管理的,而FileShuffleBlockManager最终也是使用BlockMan

- yum方式部署zabbix

ronin47

yum方式部署zabbix

安装网络yum库#rpm -ivh http://repo.zabbix.com/zabbix/2.4/rhel/6/x86_64/zabbix-release-2.4-1.el6.noarch.rpm 通过yum装mysql和zabbix调用的插件还有agent代理#yum install zabbix-server-mysql zabbix-web-mysql mysql-

- Hibernate4和MySQL5.5自动创建表失败问题解决方法

byalias

J2EEHibernate4

今天初学Hibernate4,了解了使用Hibernate的过程。大体分为4个步骤:

①创建hibernate.cfg.xml文件

②创建持久化对象

③创建*.hbm.xml映射文件

④编写hibernate相应代码

在第四步中,进行了单元测试,测试预期结果是hibernate自动帮助在数据库中创建数据表,结果JUnit单元测试没有问题,在控制台打印了创建数据表的SQL语句,但在数据库中

- Netty源码学习-FrameDecoder

bylijinnan

javanetty

Netty 3.x的user guide里FrameDecoder的例子,有几个疑问:

1.文档说:FrameDecoder calls decode method with an internally maintained cumulative buffer whenever new data is received.

为什么每次有新数据到达时,都会调用decode方法?

2.Dec

- SQL行列转换方法

chicony

行列转换

create table tb(终端名称 varchar(10) , CEI分值 varchar(10) , 终端数量 int)

insert into tb values('三星' , '0-5' , 74)

insert into tb values('三星' , '10-15' , 83)

insert into tb values('苹果' , '0-5' , 93)

- 中文编码测试

ctrain

编码

循环打印转换编码

String[] codes = {

"iso-8859-1",

"utf-8",

"gbk",

"unicode"

};

for (int i = 0; i < codes.length; i++) {

for (int j

- hive 客户端查询报堆内存溢出解决方法

daizj

hive堆内存溢出

hive> select * from t_test where ds=20150323 limit 2;

OK

Exception in thread "main" java.lang.OutOfMemoryError: Java heap space

问题原因: hive堆内存默认为256M

这个问题的解决方法为:

修改/us

- 人有多大懒,才有多大闲 (评论『卓有成效的程序员』)

dcj3sjt126com

程序员

卓有成效的程序员给我的震撼很大,程序员作为特殊的群体,有的人可以这么懒, 懒到事情都交给机器去做 ,而有的人又可以那么勤奋,每天都孜孜不倦得做着重复单调的工作。

在看这本书之前,我属于勤奋的人,而看完这本书以后,我要努力变成懒惰的人。

不要在去庞大的开始菜单里面一项一项搜索自己的应用程序,也不要在自己的桌面上放置眼花缭乱的快捷图标

- Eclipse简单有用的配置

dcj3sjt126com

eclipse

1、显示行号 Window -- Prefences -- General -- Editors -- Text Editors -- show line numbers

2、代码提示字符 Window ->Perferences,并依次展开 Java -> Editor -> Content Assist,最下面一栏 auto-Activation

- 在tomcat上面安装solr4.8.0全过程

eksliang

Solrsolr4.0后的版本安装solr4.8.0安装

转载请出自出处:

http://eksliang.iteye.com/blog/2096478

首先solr是一个基于java的web的应用,所以安装solr之前必须先安装JDK和tomcat,我这里就先省略安装tomcat和jdk了

第一步:当然是下载去官网上下载最新的solr版本,下载地址

- Android APP通用型拒绝服务、漏洞分析报告

gg163

漏洞androidAPP分析

点评:记得曾经有段时间很多SRC平台被刷了大量APP本地拒绝服务漏洞,移动安全团队爱内测(ineice.com)发现了一个安卓客户端的通用型拒绝服务漏洞,来看看他们的详细分析吧。

0xr0ot和Xbalien交流所有可能导致应用拒绝服务的异常类型时,发现了一处通用的本地拒绝服务漏洞。该通用型本地拒绝服务可以造成大面积的app拒绝服务。

针对序列化对象而出现的拒绝服务主要

- HoverTree项目已经实现分层

hvt

编程.netWebC#ASP.ENT

HoverTree项目已经初步实现分层,源代码已经上传到 http://hovertree.codeplex.com请到SOURCE CODE查看。在本地用SQL Server 2008 数据库测试成功。数据库和表请参考:http://keleyi.com/a/bjae/ue6stb42.htmHoverTree是一个ASP.NET 开源项目,希望对你学习ASP.NET或者C#语言有帮助,如果你对

- Google Maps API v3: Remove Markers 移除标记

天梯梦

google maps api

Simply do the following:

I. Declare a global variable:

var markersArray = [];

II. Define a function:

function clearOverlays() {

for (var i = 0; i < markersArray.length; i++ )

- jQuery选择器总结

lq38366

jquery选择器

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

- 基础数据结构和算法六:Quick sort

sunwinner

AlgorithmQuicksort

Quick sort is probably used more widely than any other. It is popular because it is not difficult to implement, works well for a variety of different kinds of input data, and is substantially faster t

- 如何让Flash不遮挡HTML div元素的技巧_HTML/Xhtml_网页制作

刘星宇

htmlWeb

今天在写一个flash广告代码的时候,因为flash自带的链接,容易被当成弹出广告,所以做了一个div层放到flash上面,这样链接都是a触发的不会被拦截,但发现flash一直处于div层上面,原来flash需要加个参数才可以。

让flash置于DIV层之下的方法,让flash不挡住飘浮层或下拉菜单,让Flash不档住浮动对象或层的关键参数:wmode=opaque。

方法如下:

- Mybatis实用Mapper SQL汇总示例

wdmcygah

sqlmysqlmybatis实用

Mybatis作为一个非常好用的持久层框架,相关资料真的是少得可怜,所幸的是官方文档还算详细。本博文主要列举一些个人感觉比较常用的场景及相应的Mapper SQL写法,希望能够对大家有所帮助。

不少持久层框架对动态SQL的支持不足,在SQL需要动态拼接时非常苦恼,而Mybatis很好地解决了这个问题,算是框架的一大亮点。对于常见的场景,例如:批量插入/更新/删除,模糊查询,多条件查询,联表查询,