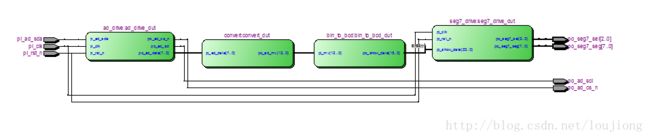

A/D转换并用数码管显示

2.顶层模块代码

module ad (pi_clk, pi_rst_n, pi_ad_sda, po_seg7_seg, po_seg7_sel,

po_ad_scl, po_ad_cs_n);

input pi_clk;// 50MHz

input pi_rst_n;

input pi_ad_sda;

output [7:0] po_seg7_seg;

output [2:0] po_seg7_sel;

output po_ad_scl;

output po_ad_cs_n;

wire [7:0] ad_data;

ad_drive ad_drive_dut(

.pi_clk (pi_clk),

.pi_rst_n (pi_rst_n),

.pi_ad_sda (pi_ad_sda),

.po_ad_scl (po_ad_scl),

.po_ad_cs_n (po_ad_cs_n),

.po_ad_data (ad_data),

.po_ad_data_flag ()

);

wire [12:0] ad_mv;

convert convert_dut(

.pi_ad_data (ad_data),

.po_ad_mv (ad_mv)

);

wire [15:0] show_data;

bin_to_bcd bin_to_bcd_dut(

.pi_mv (ad_mv),

.po_show_data (show_data)

);

seg7_drive seg7_drive_dut(

.pi_clk (pi_clk),

.pi_rst_n (pi_rst_n),

.pi_show_data ({8'h55,show_data}),

.po_seg7_sel (po_seg7_sel),

.po_seg7_seg (po_seg7_seg)

);

endmodule 3.A/D驱动模块

module ad_drive (pi_clk, pi_rst_n, pi_ad_sda, po_ad_scl, po_ad_cs_n,

po_ad_data, po_ad_data_flag);

input pi_clk;

input pi_rst_n;

input pi_ad_sda;

output reg po_ad_scl;

output reg po_ad_cs_n;

output reg [7:0] po_ad_data;

output po_ad_data_flag;

reg [7:0] temp;

reg [11:0] cnt;

always@(posedge pi_clk or negedge pi_rst_n)

begin

if (pi_rst_n==0)

cnt <= 0;

else

begin

if (cnt==1296)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

always@(posedge pi_clk or negedge pi_rst_n)

begin

if (pi_rst_n==0)

begin

po_ad_scl<=0;

po_ad_cs_n<=1;

end

else

begin

case (cnt)

0 : begin

po_ad_scl<=0;

po_ad_cs_n<=1;

end

1: begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

71 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[7]<=pi_ad_sda;

end

96 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

121 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[6]<=pi_ad_sda;

end

146 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

171 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[5]<=pi_ad_sda;

end

196 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

221 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[4]<=pi_ad_sda;

end

246 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

271 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[3]<=pi_ad_sda;

end

296 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

321 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[2]<=pi_ad_sda;

end

346 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

371 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[1]<=pi_ad_sda;

end

396 : begin

po_ad_scl<=0;

po_ad_cs_n<=0;

end

421 : begin

po_ad_scl<=1;

po_ad_cs_n<=0;

temp[0]<=pi_ad_sda;

end

446 : begin

po_ad_scl<=0;

po_ad_cs_n<=1;

end

447: begin

po_ad_data<=temp;

end

endcase

end

end

endmodule 4.数据转电压模块

module convert (pi_ad_data, po_ad_mv);

input [7:0] pi_ad_data;

output reg [12:0] po_ad_mv;

always@(*)

begin

po_ad_mv <= pi_ad_data*2500/256;

end

endmodule 5.二进制转bcd模块

module bin_to_bcd (pi_mv, po_show_data);

input [12:0] pi_mv;

output reg [15:0] po_show_data;

always@(*)

begin

po_show_data [3:0] <= pi_mv % 10;

po_show_data [7:4] <= (pi_mv/10) % 100;

po_show_data [11:8] <= (pi_mv/100) % 10;

po_show_data [15:12] <= pi_mv / 1000;

end

endmodule

5.数码管驱动模块

module seg7_drive(pi_clk, pi_rst_n, pi_show_data, po_seg7_sel, po_seg7_seg);

input pi_clk, pi_rst_n;

input [15:0] pi_show_data;

output reg [2:0] po_seg7_sel;

output reg [7:0] po_seg7_seg;

//reg [4:0] cnt;

reg [31:0] cnt_1ms;

reg pi_clk_1ms;

reg [3:0] temp;

parameter T=50_000;///1ms freq

always @ (posedge pi_clk or negedge pi_rst_n)

begin if(!pi_rst_n)

begin

cnt_1ms<=0;

pi_clk_1ms<=1;

end

else if(cnt_1ms==T/2-1’b1)

begin

cnt_1ms<=0;

pi_clk_1ms<=~pi_clk_1ms;

end

else begin

cnt_1ms<=cnt_1ms+1’b1;

pi_clk_1ms<=pi_clk_1ms;

end

end

always @ (posedge pi_clk_1ms or negedge pi_rst_n)

begin

if (!pi_rst_n)

po_seg7_sel <= 3’b000;

else if (po_seg7_sel < 3’d5)

po_seg7_sel <= po_seg7_sel +1’b1;

else

po_seg7_sel <= 0;

end

always @ (*)

begin

if (!pi_rst_n)

temp = 0;

else

case (po_seg7_sel)

3'd0: temp = 4'h0;

3'd1: temp = 4'h0;

3'd2: temp = pi_show_data[15:12];

3'd3: temp = pi_show_data[11:8];

3'd4: temp = pi_show_data[7:4];

3'd5: temp = pi_show_data[3:0];

default : temp = 4'h0;

endcase

end

always @ (*)

begin

if (!pi_rst_n)

begin

po_seg7_seg = 8’b1111_1111;

end

else

begin

case (temp)

0 : po_seg7_seg = 8’b1100_0000; //d0

1 : po_seg7_seg = 8’b1111_1001; //d1

2 : po_seg7_seg = 8’b1010_0100; //d2

3 : po_seg7_seg = 8’b1011_0000; //d3

4 : po_seg7_seg = 8’b1001_1001; //d4

5 : po_seg7_seg = 8’b1001_0010; //d5

6 : po_seg7_seg = 8’b1000_0010; //d6

7 : po_seg7_seg = 8’b1111_1000; //d7

8 : po_seg7_seg = 8’b1000_0000; //d8

9 : po_seg7_seg = 8’b1001_0000; //d9

10 : po_seg7_seg = 8’b1000_1000; //dA

11 : po_seg7_seg = 8’b1000_0011; //db

12 : po_seg7_seg = 8’b1100_0110; //dC

13 : po_seg7_seg = 8’b1010_0001; //dd

14 : po_seg7_seg = 8’b1000_0110; //dE

15 : po_seg7_seg = 8’b1000_1110; //dF

default : po_seg7_seg = 8’b1111_1111; //null

endcase

end

end

endmodule