**arm 时钟(CLOCK)和电源管理(POWER MANAGEMENT )

分类:

嵌入式

arm体系结构:arm920t

2013-07-15 19:55:10

一,概述:

时钟(clock)和电源管理(power management)的 关系:

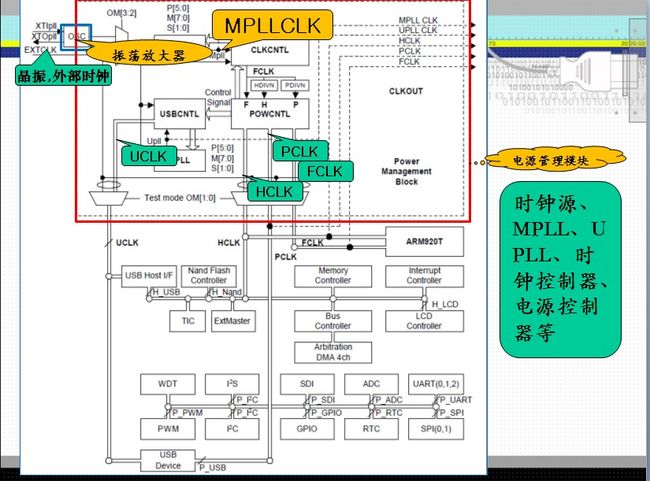

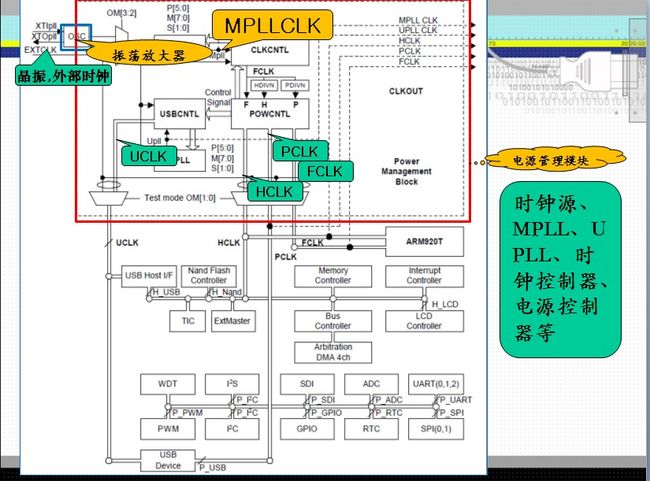

电源管理模块使用 软件来 控制系统时钟,以 降低 arm920t 中的功耗。这些方案与 PLL ,时钟控制逻辑(FCLK,

HCLK 和PCLK)和唤醒信号有关。

时钟和电源管理模块由 三部分组成: 时钟控制, USB控制和 电源控制。

1, 时钟控制逻辑

arm920t 中的 时钟控制逻辑 可以产生 必须的时钟信号 ,包括 CPU的FCLK , AHB总线外设的 HCLK 以及 APB 总线外设的 PCLK 。

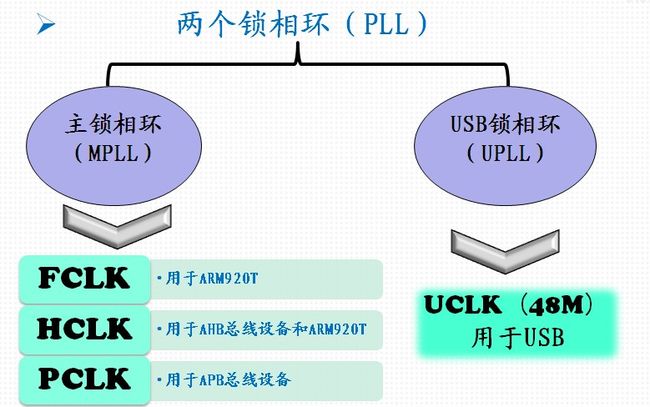

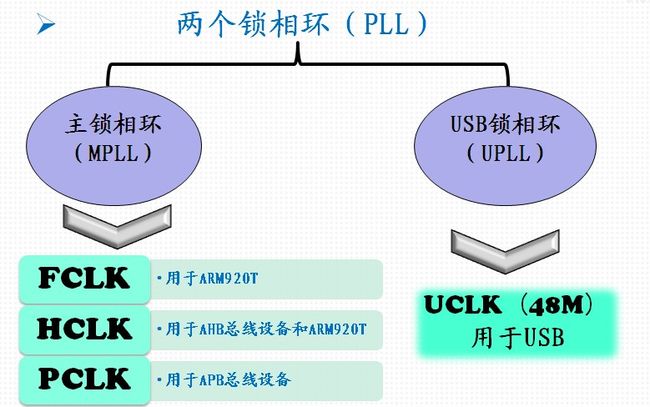

arm920t 包含 两 个锁相环(PLL ): 一个(MPLL) 提供给 FCLK、HCLK 和PCLK, 另一个(UPLL) 专用于USB模块( 48MHz )。

时钟控制逻辑可以不使用 PLL 来减慢时钟,并且可以由软件连接或断开各外设模块的时钟,以降低功耗。

2,USB时钟控制

USB 主机接口和 USB设备接口都需要 48MHz 的时钟。 arm920t 中,USB专用PLL (UPLL)生成48MHz给USB。

在配置 PLL(UPLL)之前不提供 UCLK。

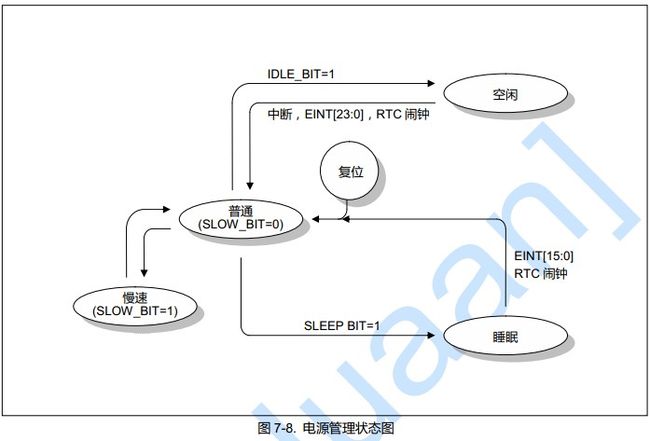

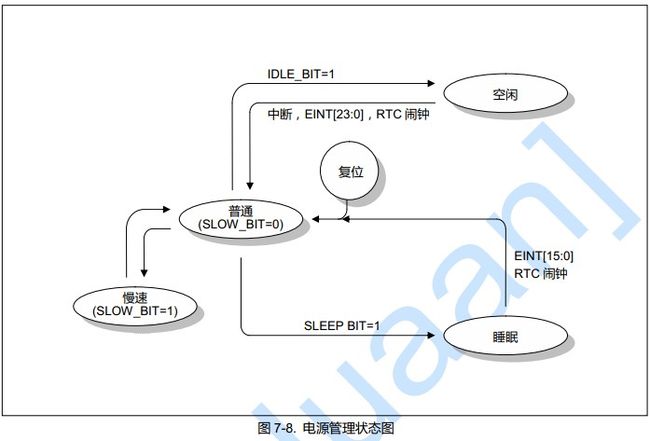

3, 电源控制逻辑

arm920t 包含了各种电源管理方案来保证对给定任务的最佳功耗。 arm920t 中的电源

管理模块可以激活成 四 种模式: 正常(NORMAL)模式 、 慢速(SLOW )模式 、 空闲(IDLE)模式 和 睡眠(SLEEP)模式 。

关系如下:

1,note:

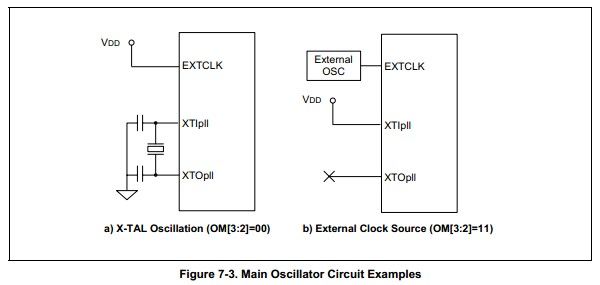

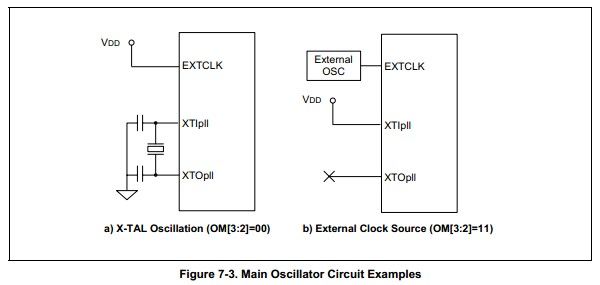

主时钟源来自一个 外部晶振(XTIpll)或外部时钟(EXTCLK )。时钟发生包含了一个连接到外部晶振的振荡器oscillator(震荡放大器Oscillation Amplifier, OSC),还含有 arm920t所必须的 两个用于 产生高频率时钟的 PLL(锁相环)。

2,note:

时钟与电源管理用到的arm920t 核的 引脚信号

3,note:

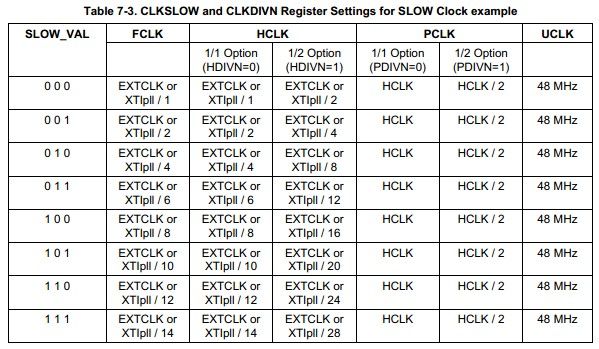

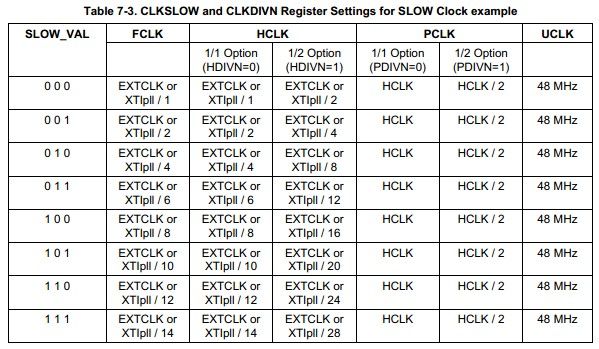

(1) 在NORMAL模式下,FCLK=Mpll;

(2) 在SLOW模式(刚上电或是复位)下,FCLK=(晶振或EXTCLK)/分频因子。

CPU默认的工作主频为12MHz或16.9344MHz,这里使用最多的是12M。

相关的寄存器:

二, 时钟控制逻辑

1,PLL,FCLK,HCLK,PCLK 的含义

arm920t中的 时钟控制逻辑可以产生 必须的时钟信号,包括 CPU的FCLK, AHB总线外设的 HCLK 以及 APB 总线外设的 PCLK。

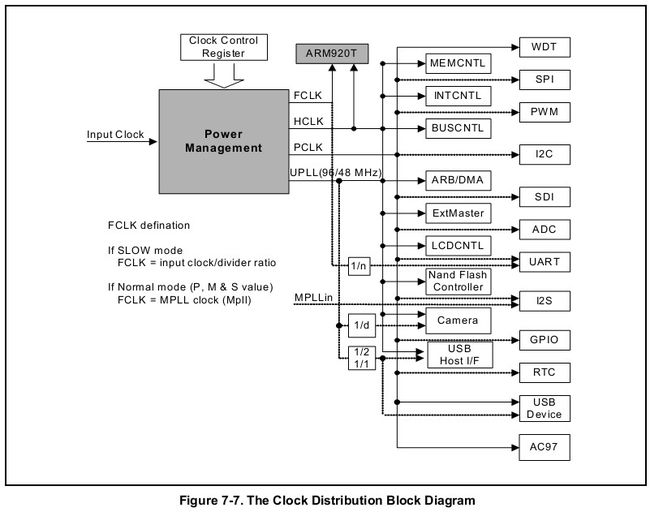

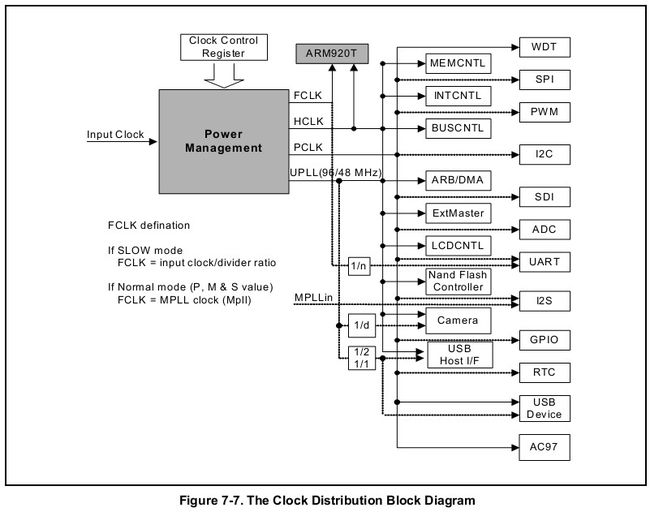

FCLK 是提供给 ARM920T 的时钟。

HCLK 是提供给用于ARM920T,存储器控制器,中断控制器,LCD 控制器,D MA和USB主机模块的 AHB总线的时钟。

PCLK 是提供给用于外设如 WDT,IIS,I2C ,PWM 定时器,MMC/SD接口,ADC,UART,GPIO,RTC和SPI 的APB 总线的时钟。

arm920t 包含 两 个锁相环(PLL ): 一个(MPLL) 提供给 FCLK、HCLK 和PCLK, 一个(UPLL) 专用于USB模块( 48MHz )。

时钟控制逻辑可以不使用 PLL 来减慢时钟,并且可以由软件连接或断开各外设模块的时钟,以降低功耗。

含有两个锁相环MPLL、UPLL产生系统所需要的不同频率的时钟

MPLL:

为CPU产生FCLK时钟

为AHB产生HCLK时钟

为APB产生PCLK时钟

UPLL:

为USB (Host and Device)产生UCLK (48MHz)

2,PLL 与 FCLK 的关系

(1)在NORMAL(启用PLL)模式下,FCLK=Mpll;

(2)在SLOW模式(刚上电或是复位,没有启用PLL)下,FCLK=(晶振或EXTCLK)/分频因子。

CPU默认的工作主频为12MHz或16.9344MHz,这里使用最多的是12M。

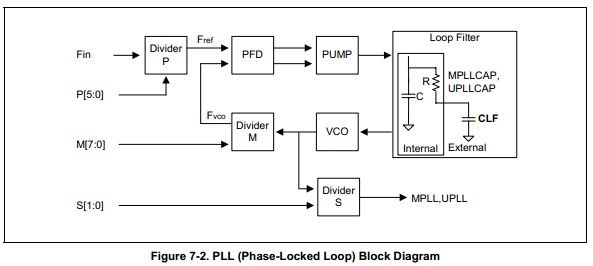

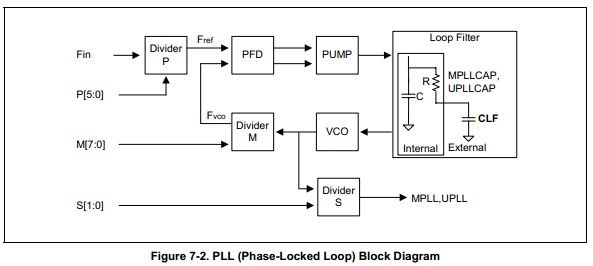

锁相环输出频率( Mpll 和Upll计算方法不相同 )

Mpll =(2*m*Fin) / (p*2^S)

Upll =(m * Fin) / (p * 2^S)

Fin指CPU外围接的晶振本身的频率,通常为12MHz。

主振荡电路:

通过 OM[3:2] arm920t核的管脚选择 时钟源:

注意:

1. 虽然MPLL在 复位后就 开始,MPLL输出(Mpll) 并没有作为系统时钟,直到软件 写入有效值来设置 MPLLCON寄存器。

在设置此值 之前,是将 外部晶振或外部时钟源提供的时钟 直接作为系统时钟。即使用户不想改变 MPLLCON寄存器的

默认值,用户也应当写入与之相同的值到 MPLLCON 寄存器寄存器中。

常用模式为:OM[3:2] = 00

2. OM[3:2]是用于当 OM[1:0]为11时决定一个测试模式

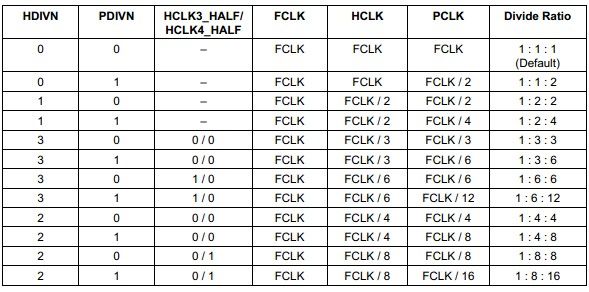

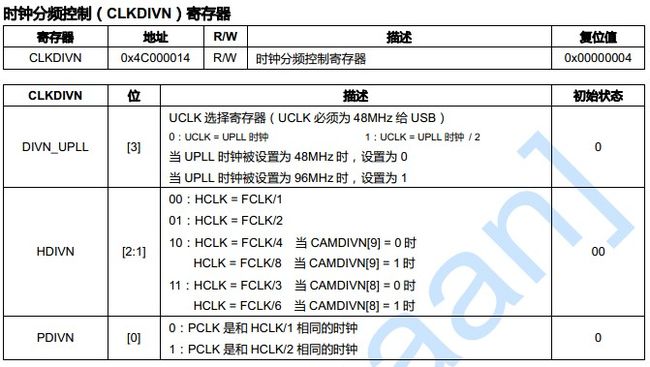

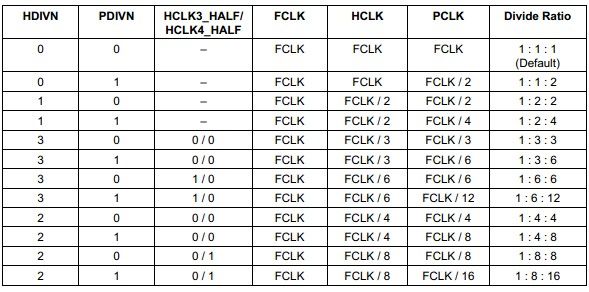

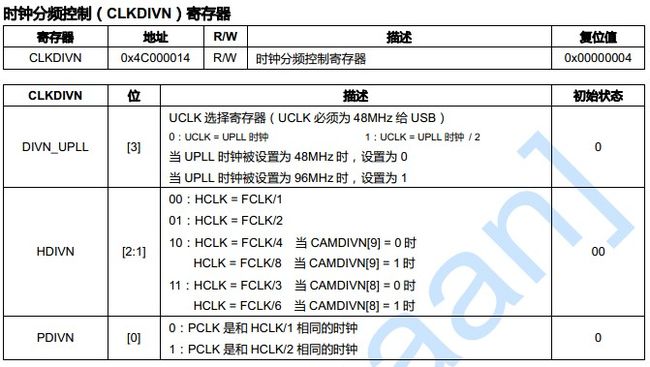

3,FCLK,HCLK,PCLK 相互之间的关系

HDIVN,PDIVN:

HCLK3_HALF ,HCLK4_HALF :

三,USB时钟控制

USB 主机接口和 USB设备接口都需要 48MHz的时钟。 arm920t中,USB专用PLL (UPLL)生成48MHz给USB。

在配置 PLL(UPLL)之前不提供 UCLK。

电源控制逻辑

arm920t包含了各种电源管理方案来保证对给定任务的最佳功耗。 arm920t中的电源

管理模块可以激活成 四种模式: 正常(NORMAL)模式、 慢速(SLOW )模式、 空闲(IDLE)模式和 睡眠(SLEEP)模式 。

普通(NORMAL)模式:

1, 锁相环(PLL)工作

2, 为CPU和所有片内外设提供时钟

3, 此模式系统功耗最大

4,它允许用户用软件控制外设的运行。例如如果一个定时器不是必须的,

用户可以断开连接到定时器的时钟(CLKCON寄存器),以降低功耗。

慢速(SLOW )模式:

1,锁相环不工作

2, CPU等直接使用原始时钟、或原始时钟的分频工作,此模式工作时钟频率低而使功耗低,并且锁相环不工作也使功耗降低

3,在此模式中,功耗只取决于外部时钟的频率。排除了因 PLL 而产生的功耗。

注意:PLL只可以在 慢速(SLOW)模式 下被关闭,如果在其他模式下关闭PLL,MCD并不确保 关闭PLL 操作正常。

4, 模式转换

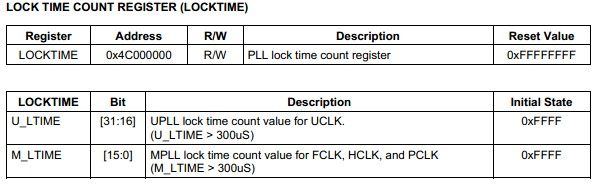

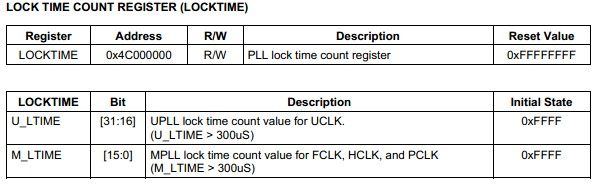

(1), MPLL启动后需要等待一段时间(LockTime),MPLL输出才会稳定。

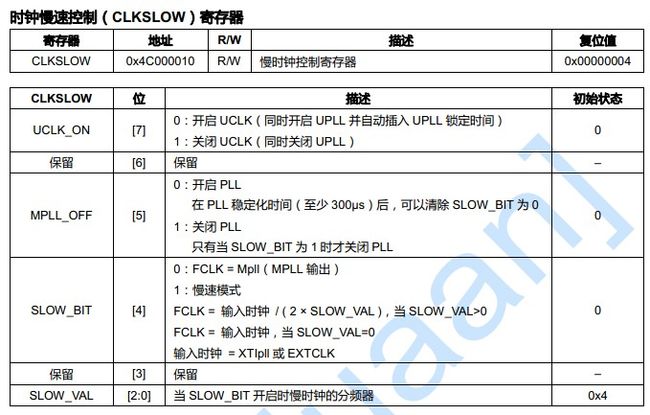

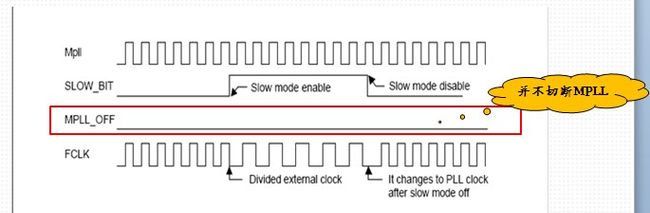

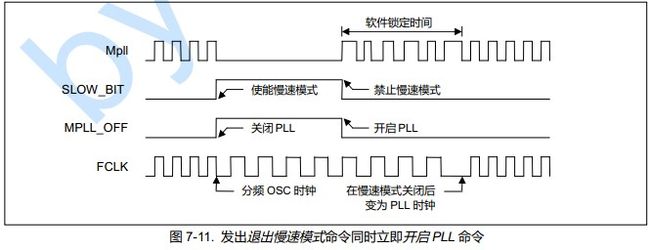

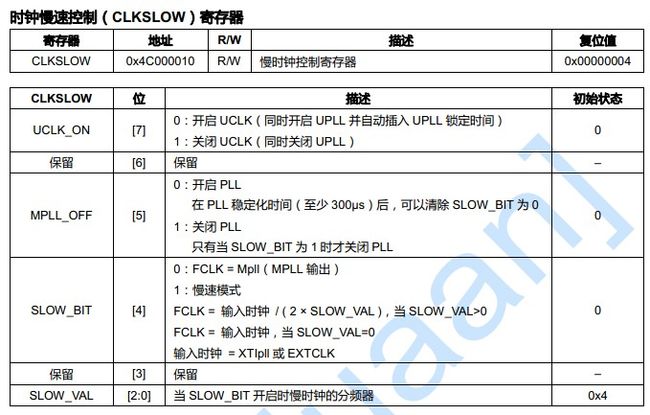

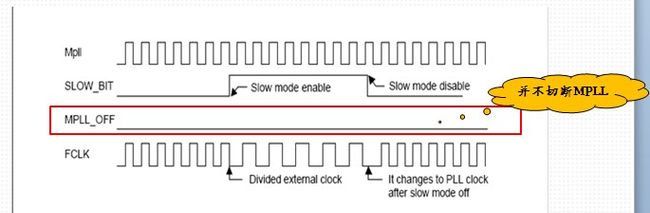

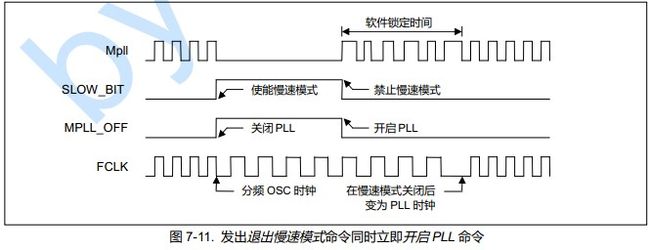

(2) 普通(NORMAL)模式 转换为 慢速(SLOW )模式

把 时钟慢速控制(CLKSLOW)寄存器 中的 bit[4] SLOW_BIT=1 即可。

(3) 慢速(SLOW )模式 转换为 普通(NORMAL)模式

@1@ MPLL 输出稳定 前(在 锁定时间(Lock Time)之前)

如果用户在 PLL 锁定时间后通过同时禁止 CLKSLOW 寄存器中的 SLOW_BIT和 MPLL_OFF位来实现

从慢速模式切换到普通模式,只在 PLL 锁定时间后才会改变频率。

@2@ MPLL 输出稳定 后 (在 锁定时间(Lock Time)之后)

如果用户在PLL 锁定时间后通过禁止 CLKSLOW 寄存器中的 SLOW_BIT来实现从慢速模式切换到普通模式,

只在禁止慢速模式后才会改变频率。

空闲(IDLE)模式:

1,停止为CPU提供时钟,CPU不工作(其外设均工作)

2, 退出方法:任何中断请求可唤醒CPU工作,退出空闲模式

3,这个模块只断开了CPU内核的时钟(FCLK),但它提供时钟给所有其它外设。

空闲模式产生了因 CPU内核而产生的功耗减少的结果。 任何中断请求给 CPU都可以使其从空闲模式中唤醒。

4,如何 进入 空闲(IDLE)模式

把 时钟生成控制寄存器( CLKCON) 的 bit[2] IDLE BIT 设置为 1,进入空闲模式。此位不会自动清零 。

睡眠(SLEEP)模式:

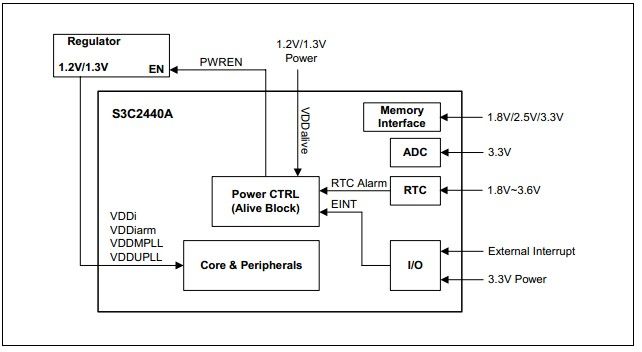

1,时钟模块断电,除了唤醒电路之外所有部分均不供电.

2,系统需分成两部分供电。此模式 功耗最低

3,退出方法:用中断唤醒必须设置外中断

(1)外部中断EINT0---15

(2)实时钟报警中断

4,这个模块与内部供电是分离的。因此在此模式中发生了没有因 CPU和除唤醒逻辑以外 的

内部逻辑的功耗。要激活睡眠模式需要 两个独立的供电电源。两个电源之 一提供电源给唤醒逻辑。

另一个提供电源给包括 CPU在内的其它内部逻辑,而且应当能够控制供电的开和关。在睡眠模式中,

第二个为 CPU和内部逻辑供电电源将被关闭。可以由 EINT[15:0] 或RTC闹铃中断产生从睡眠模式中唤醒。

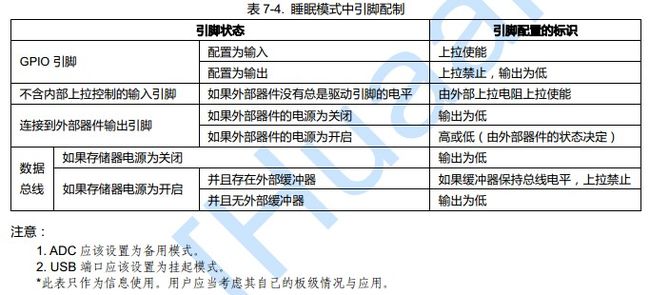

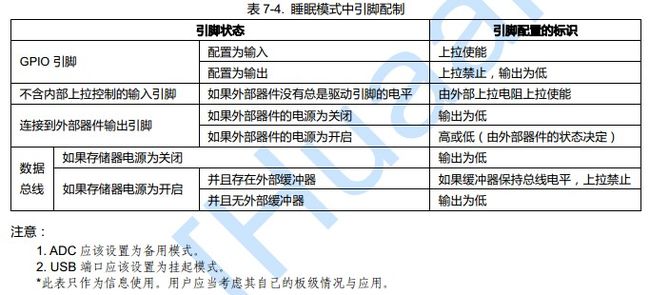

5,进入 睡眠(SLEEP)模式

1. 为睡眠模式合理设置GPIO配置。

2. 屏蔽INTMSK 寄存器中所有中断。

3. 合理配置包括 RTC闹钟在内的唤醒源。(不需要屏蔽唤醒源在EINTMASK中的对应位,

目的是使得 SRCPND或EINTPEND的对应位能置位。然而引发了唤醒源并且屏蔽了EINTMASK的对应位,

唤醒也将发生但SRCPND或EINTPEND的对应位将不会被置位。)

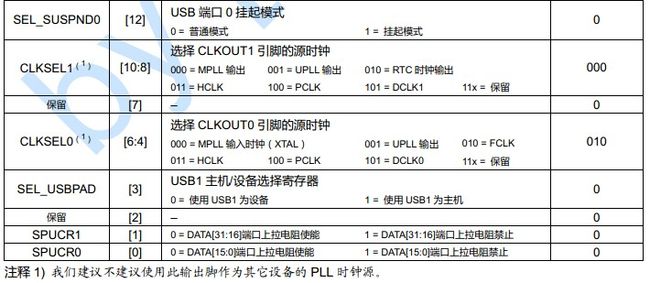

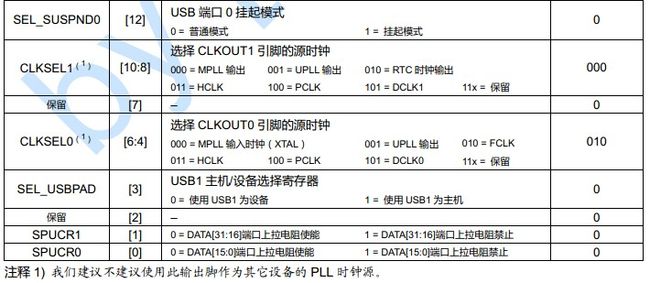

4. 设置USB端口为挂起模式(MISCCR[13:12]=11b)。

5. 保存一些有特殊含义的值到 GSTATUS[4:3]寄存器。这些寄存器在睡眠模式期间是被保护的。

6. 为数据总线 D[31:0]的上拉电阻配置MISCCR[1:0] 。如果有的外部总线保持器,例如 74LVCH162245,

关闭上拉电阻。如果没有开启上拉电阻。另外存储器相关引脚设置为两种类型,另一个是非活动状态。

7. 清除LCDCON1.ENVID位来停止 LCD 。

8. 读取rREFRESH 和rCLKCON寄存器以填充 TLB 。

9. 设置REFRESH[22]=1b使得 SDRAM 进入自刷新模式。

10. 等待直到 SDRAM 自刷新有效。

11. 设置MISCCR[19:17]=111b 使得 SDRAM 信号(SCLK0,SCLK1和SCKE )在睡眠模式期间受到保护。

12. 设置CLKCON寄存器中的睡眠模式位。

6,从 睡眠(SLEEP)模式 中唤醒

1. 如果引发了唤醒源之一将发出内部复位信号。它将与触发了外部 nRESET 引脚的情况相同。

此复位持续时间由内部 16位控制逻辑和由 tRST = (65535 / XTAL_频率)计算得到的复位触发时间而决定。

2. 检查GSTATUS2[2]以了解是否是上电使得从睡眠模式中唤醒。

3. 设置MISCCR [19:17]=000b 释放 SDRAM 信号保护。

4. 配置SDRAM 存储器控制器。

5. 等待直到 SDRAM 自刷新被释放。通常 SDRAM 需要刷新所有 SDRAM 行的周期。

6. GSTATUS[3:4]中的信息可以用于用户自己的目的,因为在睡眠模式期间 GSTATUS[3:4]中的值是被保护的。

7. 对于EINT[3:0],检查SRCPND寄存器。

对于EINT[15:4] ,检查 EINTPEND而不是 SRCPND(SRCPND将不会被置位尽管 EINTPEND的某些位会被置位)。

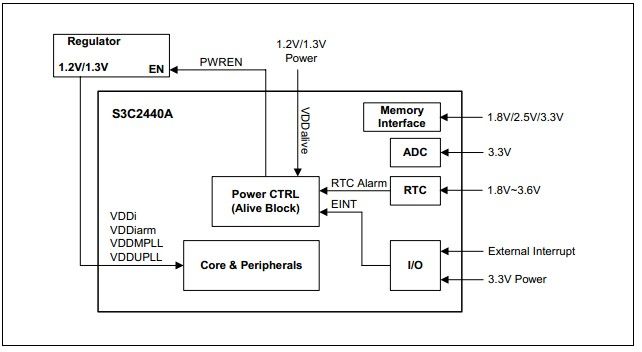

7,睡眠(SLEEP)模式的 电源控制

@1@ 睡眠模式中,通过 控制 PWREN 引脚,把 VDDi,VDDiarm,VDDMPLL 和VDDUPLL 都关闭。

@2@ 如果激活(高点平)了 PWREN 信号,VDDi和VDDiarm将由一个外部电压调节器提供。

如果 PWREN 引脚是非激活的(低电平),则VDDi和VDDiarm会被关闭。

注释:

即使可能关闭了 VDDi,VDDia rm,VDDMPLL 和VDDUPLL,也应当提供给其它电源引脚

8, 睡眠(SLEEP)模式的唤醒条件

@1@ 电平信号或者边沿信号出现在EINTn输入引脚且被确认。

@2@ EINTn输入引脚被配置成外部中断。

@3@ nBATT-FLT位为高电平。

注意: 一旦唤醒后,相应的EINTn引脚将不再用于唤醒,即此引脚又可以重新作为一个外部中断源使用。

9,睡眠模式和数据总线的上拉电阻

睡眠模式中可以选定 数据总线(D[31:0]或D[15:0])为高阻态或输出低电平的状态。

数据总线可以设置为开启上拉电阻的高阻态或为睡眠模式降低功耗而设置为关闭上拉电阻的输出低电平。

D[31:0]引脚的上拉电阻由 GPIO 控制寄存器(MISCCR )控制。然而如果还有一个外部总线保持器,

如74LVCH162245在数据总线上,用户可以选择二者之一的状态:一个是关闭上拉电阻的输出低电平,

另一个是关闭上拉电阻的高阻态,都为低功耗。

10,睡眠模式和输出端口状态

输出端口应当在关闭电源模式中设置为一个合理的逻辑电平使得电流消耗最小。如果输出端口引脚没有接负载则首选高电平。

如果输出为低电平,内部寄生电阻将消耗电流;如果输出为高电平,将不会消耗电流。

作为输出端口,如果输出状态为高电平将减少电流的消耗。 睡眠模式中推荐将输出端口设置为输出高电平。

11,电池故障信号( nBATT_FLT)

nBATT_FLT引脚有如下两个功能。

(1)当CPU不处于睡眠模式时 nBATT_FLT引脚将通过设置 BATT_FUNC( MISCCR[22:20])为10x’b 来引起中断请求。

nBATT_FLT的中断类型为为低电平时触发。

(2)当CPU处于睡眠模式时 nBATT_FLT的发出将通过设置 BATT_FUNC( MISCCR[22:20])为11x’b来禁止从睡眠模式的唤醒。

因此任何唤醒源都将被屏蔽。 如果设置了 nBATT_FLT,是为了保护电池电量过低的系统故障。

杂项控制寄存器(MISCELLANEOUS CONTROL REGISTER, MISCCR )

12, ADC掉电

ADC 在 ADCCON寄存器中包含了一个额外的掉电位 bit[2]STDBM。

如果arm920t进入睡眠模式,则ADC应当进入其自己的掉电模式。

一,概述:

时钟(clock)和电源管理(power management)的 关系:

电源管理模块使用 软件来 控制系统时钟,以 降低 arm920t 中的功耗。这些方案与 PLL ,时钟控制逻辑(FCLK,

HCLK 和PCLK)和唤醒信号有关。

时钟和电源管理模块由 三部分组成: 时钟控制, USB控制和 电源控制。

1, 时钟控制逻辑

arm920t 中的 时钟控制逻辑 可以产生 必须的时钟信号 ,包括 CPU的FCLK , AHB总线外设的 HCLK 以及 APB 总线外设的 PCLK 。

arm920t 包含 两 个锁相环(PLL ): 一个(MPLL) 提供给 FCLK、HCLK 和PCLK, 另一个(UPLL) 专用于USB模块( 48MHz )。

时钟控制逻辑可以不使用 PLL 来减慢时钟,并且可以由软件连接或断开各外设模块的时钟,以降低功耗。

2,USB时钟控制

USB 主机接口和 USB设备接口都需要 48MHz 的时钟。 arm920t 中,USB专用PLL (UPLL)生成48MHz给USB。

在配置 PLL(UPLL)之前不提供 UCLK。

3, 电源控制逻辑

arm920t 包含了各种电源管理方案来保证对给定任务的最佳功耗。 arm920t 中的电源

管理模块可以激活成 四 种模式: 正常(NORMAL)模式 、 慢速(SLOW )模式 、 空闲(IDLE)模式 和 睡眠(SLEEP)模式 。

关系如下:

1,note:

主时钟源来自一个 外部晶振(XTIpll)或外部时钟(EXTCLK )。时钟发生包含了一个连接到外部晶振的振荡器oscillator(震荡放大器Oscillation Amplifier, OSC),还含有 arm920t所必须的 两个用于 产生高频率时钟的 PLL(锁相环)。

2,note:

时钟与电源管理用到的arm920t 核的 引脚信号

注意: nRSTOUT,PWREN,OM[3:2],CLKOUT[1:0]

3,note:

(1) 在NORMAL模式下,FCLK=Mpll;

(2) 在SLOW模式(刚上电或是复位)下,FCLK=(晶振或EXTCLK)/分频因子。

CPU默认的工作主频为12MHz或16.9344MHz,这里使用最多的是12M。

相关的寄存器:

二, 时钟控制逻辑

1,PLL,FCLK,HCLK,PCLK 的含义

arm920t中的 时钟控制逻辑可以产生 必须的时钟信号,包括 CPU的FCLK, AHB总线外设的 HCLK 以及 APB 总线外设的 PCLK。

FCLK 是提供给 ARM920T 的时钟。

HCLK 是提供给用于ARM920T,存储器控制器,中断控制器,LCD 控制器,D MA和USB主机模块的 AHB总线的时钟。

PCLK 是提供给用于外设如 WDT,IIS,I2C ,PWM 定时器,MMC/SD接口,ADC,UART,GPIO,RTC和SPI 的APB 总线的时钟。

arm920t 包含 两 个锁相环(PLL ): 一个(MPLL) 提供给 FCLK、HCLK 和PCLK, 一个(UPLL) 专用于USB模块( 48MHz )。

时钟控制逻辑可以不使用 PLL 来减慢时钟,并且可以由软件连接或断开各外设模块的时钟,以降低功耗。

含有两个锁相环MPLL、UPLL产生系统所需要的不同频率的时钟

MPLL:

为CPU产生FCLK时钟

为AHB产生HCLK时钟

为APB产生PCLK时钟

UPLL:

为USB (Host and Device)产生UCLK (48MHz)

2,PLL 与 FCLK 的关系

(1)在NORMAL(启用PLL)模式下,FCLK=Mpll;

(2)在SLOW模式(刚上电或是复位,没有启用PLL)下,FCLK=(晶振或EXTCLK)/分频因子。

CPU默认的工作主频为12MHz或16.9344MHz,这里使用最多的是12M。

锁相环输出频率( Mpll 和Upll计算方法不相同 )

Mpll =(2*m*Fin) / (p*2^S)

Upll =(m * Fin) / (p * 2^S)

Fin指CPU外围接的晶振本身的频率,通常为12MHz。

m = MDIV+8,

p = PDIV+2,

注意 : 当你设置 MPLL 和UPLL 的值时,你必须首先设置 UPLL 值再设置 MPLL 值。(大约需要 7 个NOP的间隔)

主振荡电路:

通过 OM[3:2] arm920t核的管脚选择 时钟源:

注意:

1. 虽然MPLL在 复位后就 开始,MPLL输出(Mpll) 并没有作为系统时钟,直到软件 写入有效值来设置 MPLLCON寄存器。

在设置此值 之前,是将 外部晶振或外部时钟源提供的时钟 直接作为系统时钟。即使用户不想改变 MPLLCON寄存器的

默认值,用户也应当写入与之相同的值到 MPLLCON 寄存器寄存器中。

常用模式为:OM[3:2] = 00

2. OM[3:2]是用于当 OM[1:0]为11时决定一个测试模式

3,FCLK,HCLK,PCLK 相互之间的关系

HDIVN,PDIVN:

HCLK3_HALF ,HCLK4_HALF :

三,USB时钟控制

USB 主机接口和 USB设备接口都需要 48MHz的时钟。 arm920t中,USB专用PLL (UPLL)生成48MHz给USB。

在配置 PLL(UPLL)之前不提供 UCLK。

电源控制逻辑

arm920t包含了各种电源管理方案来保证对给定任务的最佳功耗。 arm920t中的电源

管理模块可以激活成 四种模式: 正常(NORMAL)模式、 慢速(SLOW )模式、 空闲(IDLE)模式和 睡眠(SLEEP)模式 。

普通(NORMAL)模式:

1, 锁相环(PLL)工作

2, 为CPU和所有片内外设提供时钟

3, 此模式系统功耗最大

4,它允许用户用软件控制外设的运行。例如如果一个定时器不是必须的,

用户可以断开连接到定时器的时钟(CLKCON寄存器),以降低功耗。

慢速(SLOW )模式:

1,锁相环不工作

2, CPU等直接使用原始时钟、或原始时钟的分频工作,此模式工作时钟频率低而使功耗低,并且锁相环不工作也使功耗降低

3,在此模式中,功耗只取决于外部时钟的频率。排除了因 PLL 而产生的功耗。

注意:PLL只可以在 慢速(SLOW)模式 下被关闭,如果在其他模式下关闭PLL,MCD并不确保 关闭PLL 操作正常。

4, 模式转换

(1), MPLL启动后需要等待一段时间(LockTime),MPLL输出才会稳定。

(2) 普通(NORMAL)模式 转换为 慢速(SLOW )模式

把 时钟慢速控制(CLKSLOW)寄存器 中的 bit[4] SLOW_BIT=1 即可。

(3) 慢速(SLOW )模式 转换为 普通(NORMAL)模式

@1@ MPLL 输出稳定 前(在 锁定时间(Lock Time)之前)

如果用户在 PLL 锁定时间后通过同时禁止 CLKSLOW 寄存器中的 SLOW_BIT和 MPLL_OFF位来实现

从慢速模式切换到普通模式,只在 PLL 锁定时间后才会改变频率。

@2@ MPLL 输出稳定 后 (在 锁定时间(Lock Time)之后)

如果用户在PLL 锁定时间后通过禁止 CLKSLOW 寄存器中的 SLOW_BIT来实现从慢速模式切换到普通模式,

只在禁止慢速模式后才会改变频率。

空闲(IDLE)模式:

1,停止为CPU提供时钟,CPU不工作(其外设均工作)

2, 退出方法:任何中断请求可唤醒CPU工作,退出空闲模式

3,这个模块只断开了CPU内核的时钟(FCLK),但它提供时钟给所有其它外设。

空闲模式产生了因 CPU内核而产生的功耗减少的结果。 任何中断请求给 CPU都可以使其从空闲模式中唤醒。

4,如何 进入 空闲(IDLE)模式

把 时钟生成控制寄存器( CLKCON) 的 bit[2] IDLE BIT 设置为 1,进入空闲模式。此位不会自动清零 。

睡眠(SLEEP)模式:

1,时钟模块断电,除了唤醒电路之外所有部分均不供电.

2,系统需分成两部分供电。此模式 功耗最低

3,退出方法:用中断唤醒必须设置外中断

(1)外部中断EINT0---15

(2)实时钟报警中断

4,这个模块与内部供电是分离的。因此在此模式中发生了没有因 CPU和除唤醒逻辑以外 的

内部逻辑的功耗。要激活睡眠模式需要 两个独立的供电电源。两个电源之 一提供电源给唤醒逻辑。

另一个提供电源给包括 CPU在内的其它内部逻辑,而且应当能够控制供电的开和关。在睡眠模式中,

第二个为 CPU和内部逻辑供电电源将被关闭。可以由 EINT[15:0] 或RTC闹铃中断产生从睡眠模式中唤醒。

5,进入 睡眠(SLEEP)模式

1. 为睡眠模式合理设置GPIO配置。

2. 屏蔽INTMSK 寄存器中所有中断。

3. 合理配置包括 RTC闹钟在内的唤醒源。(不需要屏蔽唤醒源在EINTMASK中的对应位,

目的是使得 SRCPND或EINTPEND的对应位能置位。然而引发了唤醒源并且屏蔽了EINTMASK的对应位,

唤醒也将发生但SRCPND或EINTPEND的对应位将不会被置位。)

4. 设置USB端口为挂起模式(MISCCR[13:12]=11b)。

5. 保存一些有特殊含义的值到 GSTATUS[4:3]寄存器。这些寄存器在睡眠模式期间是被保护的。

6. 为数据总线 D[31:0]的上拉电阻配置MISCCR[1:0] 。如果有的外部总线保持器,例如 74LVCH162245,

关闭上拉电阻。如果没有开启上拉电阻。另外存储器相关引脚设置为两种类型,另一个是非活动状态。

7. 清除LCDCON1.ENVID位来停止 LCD 。

8. 读取rREFRESH 和rCLKCON寄存器以填充 TLB 。

9. 设置REFRESH[22]=1b使得 SDRAM 进入自刷新模式。

10. 等待直到 SDRAM 自刷新有效。

11. 设置MISCCR[19:17]=111b 使得 SDRAM 信号(SCLK0,SCLK1和SCKE )在睡眠模式期间受到保护。

12. 设置CLKCON寄存器中的睡眠模式位。

6,从 睡眠(SLEEP)模式 中唤醒

1. 如果引发了唤醒源之一将发出内部复位信号。它将与触发了外部 nRESET 引脚的情况相同。

此复位持续时间由内部 16位控制逻辑和由 tRST = (65535 / XTAL_频率)计算得到的复位触发时间而决定。

2. 检查GSTATUS2[2]以了解是否是上电使得从睡眠模式中唤醒。

3. 设置MISCCR [19:17]=000b 释放 SDRAM 信号保护。

4. 配置SDRAM 存储器控制器。

5. 等待直到 SDRAM 自刷新被释放。通常 SDRAM 需要刷新所有 SDRAM 行的周期。

6. GSTATUS[3:4]中的信息可以用于用户自己的目的,因为在睡眠模式期间 GSTATUS[3:4]中的值是被保护的。

7. 对于EINT[3:0],检查SRCPND寄存器。

对于EINT[15:4] ,检查 EINTPEND而不是 SRCPND(SRCPND将不会被置位尽管 EINTPEND的某些位会被置位)。

7,睡眠(SLEEP)模式的 电源控制

@1@ 睡眠模式中,通过 控制 PWREN 引脚,把 VDDi,VDDiarm,VDDMPLL 和VDDUPLL 都关闭。

@2@ 如果激活(高点平)了 PWREN 信号,VDDi和VDDiarm将由一个外部电压调节器提供。

如果 PWREN 引脚是非激活的(低电平),则VDDi和VDDiarm会被关闭。

注释:

即使可能关闭了 VDDi,VDDia rm,VDDMPLL 和VDDUPLL,也应当提供给其它电源引脚

8, 睡眠(SLEEP)模式的唤醒条件

@1@ 电平信号或者边沿信号出现在EINTn输入引脚且被确认。

@2@ EINTn输入引脚被配置成外部中断。

@3@ nBATT-FLT位为高电平。

注意: 一旦唤醒后,相应的EINTn引脚将不再用于唤醒,即此引脚又可以重新作为一个外部中断源使用。

9,睡眠模式和数据总线的上拉电阻

睡眠模式中可以选定 数据总线(D[31:0]或D[15:0])为高阻态或输出低电平的状态。

数据总线可以设置为开启上拉电阻的高阻态或为睡眠模式降低功耗而设置为关闭上拉电阻的输出低电平。

D[31:0]引脚的上拉电阻由 GPIO 控制寄存器(MISCCR )控制。然而如果还有一个外部总线保持器,

如74LVCH162245在数据总线上,用户可以选择二者之一的状态:一个是关闭上拉电阻的输出低电平,

另一个是关闭上拉电阻的高阻态,都为低功耗。

10,睡眠模式和输出端口状态

输出端口应当在关闭电源模式中设置为一个合理的逻辑电平使得电流消耗最小。如果输出端口引脚没有接负载则首选高电平。

如果输出为低电平,内部寄生电阻将消耗电流;如果输出为高电平,将不会消耗电流。

作为输出端口,如果输出状态为高电平将减少电流的消耗。 睡眠模式中推荐将输出端口设置为输出高电平。

11,电池故障信号( nBATT_FLT)

nBATT_FLT引脚有如下两个功能。

(1)当CPU不处于睡眠模式时 nBATT_FLT引脚将通过设置 BATT_FUNC( MISCCR[22:20])为10x’b 来引起中断请求。

nBATT_FLT的中断类型为为低电平时触发。

(2)当CPU处于睡眠模式时 nBATT_FLT的发出将通过设置 BATT_FUNC( MISCCR[22:20])为11x’b来禁止从睡眠模式的唤醒。

因此任何唤醒源都将被屏蔽。 如果设置了 nBATT_FLT,是为了保护电池电量过低的系统故障。

杂项控制寄存器(MISCELLANEOUS CONTROL REGISTER, MISCCR )

12, ADC掉电

ADC 在 ADCCON寄存器中包含了一个额外的掉电位 bit[2]STDBM。

如果arm920t进入睡眠模式,则ADC应当进入其自己的掉电模式。