硬件学习系列——设计之中——1信号完整性相关再学习

信号的时域和频域:

信号完整性的研究主要从 信号的时域和频域去研究。

其中:傅里叶变化 : 将信号从时域变换为频域

傅里叶逆变换:将信号从频域变换为时域

常用的傅里叶变换:傅里叶积分 离散傅里叶变换

时域 直观 时间和信号波形 但难以发现和解决问题。

频域 容易定位 解决问题 但其无明显指标咳参考

信号带宽:

把一个信号所包含谐波的最高频率与最低频率之差,即该信号所拥有的频率范围,定义为该信号的带宽。因此可以说,信号的频率变化范围越大,信号的带宽就越宽。

3dB带宽 :3dB带宽通常指功率谱密度的最高点下降到1/2时界定的频率范围。

信号的串扰:

由信号线之间的互感和互容耦合引起:

需理解信号回流的情况:

低频时,电流沿电阻最小路径回流;

高频时,电流沿电感最小路径回流。

高频情况下,回流电路沿着信号路径下方的参考平面层流回信号源,即便存在更短的回流路径。

如下图所示:

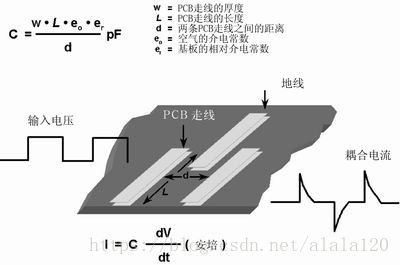

1、图1、互容耦合 : 两条彼此靠近的线之间产生寄生电容 (加大间距 减少平行布线 中加地线)

A线电压变化(dV/dt) 在邻近B线产生耦合电流,如邻近线阻抗高,则该电流转化为电压。

2、图2、互感耦合:两条彼此靠近的线会产生寄生电感(类似于变压器的互感)

A线电流变化(dI/dt) 会在A线上产生电压变化,并由于互感存在,在邻近的B线上产生成比例电流

PCB设计中很容易形成可能产生问题的两种基本寄生元件:寄生电容和寄生电感。设计电路板时,放置两条彼此靠近的走线就会产生寄生电容。可以这样做:在不同的两层,将一条走线放置在另一条走线的上方;或者在同一层,将一条走线放置在另一条走线的旁边,如图1所示。在这两种走线配置中,一条走线上电压随时间的变化(dV/dt)可能在另一条走线上产生电流。如果另一条走线是高阻抗的,电场产生的电流将转化为电压。

快速电压瞬变最常发生在模拟信号设计的数字侧。如果发生快速电压瞬变的走线靠近高阻抗模拟走线,这种误差将严重影响模拟电路的精度。在这种环境中,模拟电路有两个不利的方面:其噪声容限比数字电路低得多;高阻抗走线比较常见。

电路板中寄生电感产生的原理与寄生电容形成的原理类似。也是布两条走线,在不同的两层,将一条走线放置在另一条走线的上方;或者在同一层,将一条走线放置在另一条的旁边,如图2所示。在这两种走线配置中,一条走线上电流随时间的变化(dI/dt),由于这条走线的感抗,会在同一条走线上产生电压;并由于互感的存在,会在另一条走线上产生成比例的电流。如果在第一条走线上的电压变化足够大,干扰可能会降低数字电路的电压容限而产生误差。并不只是在数字电路中才会发生这种现象,但这种现象在数字电路中比较常见,因为数字电路中存在较大的瞬时开关电流。

为消除电磁干扰源的潜在噪声,最好将“安静”的模拟线路和噪声I/O端口分开。要设法实现低阻抗的电源和地网络,应尽量减小数字电路导线的感抗,尽量降低模拟电路的电容耦合。

减少串扰:

1、增大走线间距;

2、尽量减少平行布线长度;

3、做好匹配端接,减小串扰噪声的反射;

4、响铃的信号层,走线彼此正交;

5、在内层布线,以消除远端串扰;

6、在满足时序要求的前提下,增大信号的上升时间;

7、个别特殊信号(低频模拟信号 易受干扰信号)可使用保护地线。

8、高速数字信号,谨慎使用保护地线。

9、阻抗控制情况下,使用小介电常数的板材。

10、使信号线有一个良好的返回路径,降低返回路径的感抗,从而降低信号的波动,减弱信号对外的干扰强度。

信号完整性中的时序设计

对数据进行采样的过程中应尽可能的远离信号变化的边沿,信号的边沿往往是信号频谱最高,最容易受干扰的地方。 因此有建立时间和保持时间的概念。

如图所示:当数据信号DATA发生变化后,需要等待至少Tsu的建立时间才能被采样,采样之后,相对于采样点,数据需要保持至少Th时间才能建立。如果数据的建立时间和保持时间满足不了,就无法实现对数据的有效接收。

信号的时序设计,应确保有足够的 建立时间 和 保持时间 ,确保数据正常采集。

源同步系统 时钟来自于 Master;和 共同时钟系统 时钟来自于外部共同时钟

共同时钟系统对系统运行的最高频率的时钟有限制。

主要讨论和使用源同步系统,如SDRAM DDRX中用的多。

在轻负载的情况下,如单负载的情况下,驱动端的上升沿和接收端的上升沿相差不大;

但如果在重负载的情况下(如多负载),接收端的上升沿明显变换,这时进行时序分析的时候要特别注意。

源同步时钟系统,数据和源同步时钟信号是同步传输的,在设计中保证这两个信号的飞行时间完全一致,这样只要发送端的时序正确,则在接收端也能得到完全正确的时序。

PCB走线中的蛇形走线,即是为了满足采样的时钟信号和数据信号之间的时序控制要求。尽量使 信号能够在数据信号的中央部分读取。