51单片机学习笔记——基于C与汇编(1)

即便疫情如此还是逃避不了开学啊!最近开始学习8051系列单片机的基本原理与应用,不过作为一个学计算机的本科菜鸟,感觉写博客也力不从心,因而选择结合(盗版,嘿嘿)我一个学硬件的朋友的文章,组成一个系列。写博客是个学习的好手段,大家一起进步吧!能力所限,如果文中有所不妥,恳请指正!

该系列文章基于8051系列单片机,Keil4/Keil2,并主要使用C和汇编实现例程,汇编部分由我的大佬朋友(盗版对象)完成。本文参考了该文的内容:

https://blog.csdn.net/qq_43327300/article/details/104698377

首先我们来介绍动手前我们需要先了解的预备知识。

0、MCS-51系列单片机简介

MCS-51系列单片机最早由intel公司推出(对,就是那个intel),当时包括51和52子系列,51子系列中包含了8051这一经典产品,我们现在往往使用8051代称MCS-51系列。

为了区分各个型号,MCS-51系列有着明确的命名规则:

现在去购买相关开发板一般会买到STC89C52等型号,笔者手上的开发板用的是STC89C516也是一个较为常见的衍生型号,由于这些单片机指令系统基本一致,因而在学习中区别不大。

接下来本篇主要是基于较为典型的8051单片机对MCS-51系列单片机进行介绍进行介绍。

1、MCS-51系列单片机硬件结构

1.1 内部结构

单片机的硬件组成有

1、1个8bit的CPU

2、1个片内振荡器和时钟电路

3、程序存储器,4KB的掩膜ROM,用于存放程序、原始数据和表格

4、数据存储器

5、64KB总线扩展控制器(也就是常说的外RAM)

6、4个8位并行I/O口(P0、P1、P2、P3)

7、一个全双工串行接口

8、2个十六位的定时/计数器

9、5个中断源

程序存储器与数据存储器是分开的,符合哈佛结构。

1.2 外部引脚功能

8051总共有40个外部引脚,其中并行I/O口占了4x8=32个

1、电源引脚

VCC:芯片电源,+5V

VSS:接地

2、时钟引脚

XTAL1、XTAL2:晶体振荡电路反相输入端和输出端

![]()

接下来讲个比较,相当重要的内容——8051的时序

细节大家看书吧,我这里留个例题大家也好结合教材理解

1T机器周期=6T状态周期S=12T时钟(振荡)周期P

例:设应用单片机晶振频率为12MHz,问机器周期为多少?

解:由已知得,晶振频率为12MHZ,周期为频率的倒数

故,1/T=12MHz => T=1/12M (s)

机器周期=12x1/12M=1/1M(s)=1us

同理晶振频率为24MHz,机器周期为0.5us

3、控制引脚

RST/VPD:复位信号输入端/备用电源输入端

EA/VPP:内外ROM选择端/片内EPROM编程电源

ALE/PROG:地址锁存允许/片内EPROM编程脉冲

PSEN:外部ROM读选通信号

2、MCS-51系列单片机存储空间配置和功能

2.1存储器的类型

ROM:用于存储程序,断电后信息保留

RAM:用于存储数据,断电后信息消失,分片内片外

2.2存储单元和存储单元地址

存储器是由大量寄存器组成的,其中每一个寄存器称为一个存储单元。它可存放一个二进制代码。一个代码由若干位(bit)组成,8051单片机中算术单元是八位,即一个字节(Byte),存储器的大小也可称为存储器的容量,以字节(B)为单位,8051单片机内部有4KB的程序存储器,也就是说8051单片机的内部程序存储器可以存放4x1024个Byte

2.3存储单元的读、写操作

(1)存储器的读操作

读操作,不会破坏该单元原来的内容,只相当于数据的复制

(2)存储器的写操作

写操作,要改变或刷新该单元原来的内容,相当于原来的内容被覆盖了

2.4 MCS-51系列单片机存储空间配置

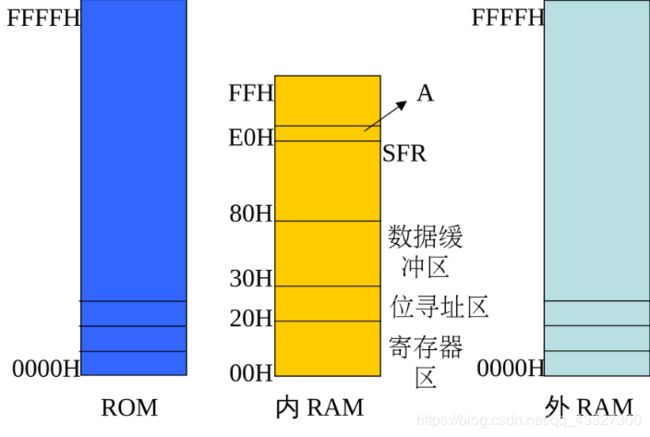

8051的存储器组织结构可以分为三个不同的存储空间

-

64KB的程序存储器(ROM),包括片内ROM和片外ROM

-

64KB的外部数据存储器(外RAM)

-

256B的内部数据存储器(内RAM)(包括特殊功能寄存器)

(1)8051的程序存储器(ROM)

地址范围:0000H~FFFFH,共计64KB

低段4KB:0000H~0FFFH

8051和8751在片内,8031在片外。高段60KB:1000H~FFFFH。在片外。

读写ROM用MOVC指令,控制信号是PSEN和EA。

(2)8051的数据存储器(RAM)

数据存储器分为外RAM和内RAM

外RAM地址范围:0000H~FFFFH共64K

内RAM地址范围:00H~FFH共256B,分为两个部分:

-

内部存储器空间,地址为00H~7FH(低128B)

-

特殊功能寄存器,地址为80H~FFH(高128B)

访问片外RAM用MOVX指令,访问片内RAM用MOV指令

2.5 8051片内数据存储空间(低128B)

![]()

(1)工作寄存区(00H~1FH)

作用:有专用于工作寄存器操作的指令,读写速度一般比内RAM要快,指令字节比一般直接寻址指令短,还具有间接寻址功能 (只有R0、R1可以)

工作寄存器 区分为四个区:0、1、2、3区。每区有八个寄存器:R0~R7

(2)位寻址区(20H~2FH)

作用:不但有字节地址,而且每一字节地址还有位地址,可以进行位操作

(3)数据缓冲区(30H~7FH)

作用:用于存放各种数据和中间结果,起到数据缓冲作用。堆栈一般开辟在这个区域

00H~7FH是一般用户能操作的区

2.6特殊功能寄存器(高128B)

21个特殊功能寄存器,其中字节地址末尾是0H或8H的寄存器每一位都有位地址,可以进行位操作

特殊功能寄存器SFR

占用地址字节:80H~FFH

位寻址器:其字节地址可被8整除,也即上面讲的0H、8H结尾

专用寄存器:

A、B、PSW、DPTR、SP

I/O接口寄存器:

P0、P1、P2、P3、SBUF、TMOD、TCON、SCON…

(1)累加器Acc

最常用的寄存器,所有的运算类指令都要使用它。累加器在指令中助记符位A,自身带有全零标志Z,若A=0则Z=1;若A != 0则Z = 0。该标志常用于程序分支转移的判断条件

(2)B寄存器

80C51中,在做乘除法时必须使用B寄存器,不做乘除法时,可作为一般寄存器使用

(3)程序状态字PSW

![]()

(4)堆栈指针SP

以后用到再来完善

(5)数据指针DPTR

分成DPL(低8位)和DPH(高8位)两个寄存器,用来存放16位地址值。

2.7并行I/O口

四个8位的双向并行端口:P0、P1、P2、P3

P0、P1、P2、P3口对应四个数据锁存器:P0、P1、P2、P3,对应内部RAM地址为80H、90H、A0H、B0H,访问I/O端口可以位寻址,当单片机复位时,P0~P3锁存器内容均为1

为了介绍方便我们以P1、P2、P3、P0的顺序进行介绍。

(1)P1口

P1口只有简单的双向I/O功能,是各口中功能最简单的一个。

在实现输出状态时我们可以参考下图:

内部总线向D触发器输入0时,V1受到高电平导通,vcc接地,因而对外输出0,同理在总线向D触发器输入1时,V1受到低电平截止,P1口从而输出高电平。

P1口在接受数据时我们可参考下图:

我们希望P1口接受数据时首先得让场效应管截止,因而需要先行输出一个高电平,使D触发器输入端为高电平,从而使高低电平的信号成功到达总线。

因而在输入数据前首先得输出一次高电平!

(2)P2口

![]()

首先我们可以用P2口实现P1口的功能:

当CPU发出控制信号1时,使多路开关MUX导向内部地址线,使P2口作为高8位地址线使用。

P2口的驱动能力为四个LSTTL门电路

(3)P3口

![]()

P3在具有我们之前介绍的P1所有的功能(如下图所示)还有第二功能。

当P3口的第二功能都保持高电平时,P3口作为通用I/O口使用,功能与P1相同

![]()

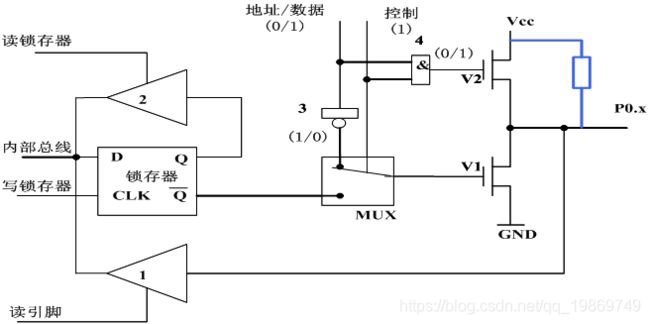

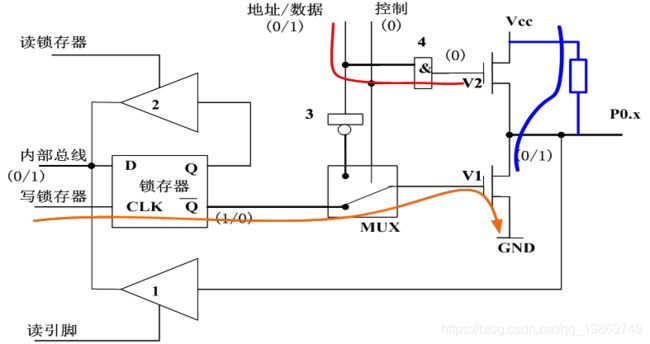

(4)P0口

P0是一个三态双向口,可作为地址/数据分时复用口,也可作为通用I/O接口也就是P1口的功能。

当控制信号为低电平时可做通用I/O口使用。

由于其缺乏上拉电阻,需外接一个上拉电阻才能输出高电平。

当控制信号为高电平时,P0口作为地址/数据分时复用总线。

3、MCS-51系列单片机的复位方式

(1)复位条件

复位(RST)引脚(9脚)上加一个持续时间为两个机器周期的高电平

若单片机时钟频率为 12MHz,则机器周期为 1us,那么则需要持续 2us以上的时间。

(2)复位后内部寄存器状态

![]()