xilinx select io IDDR 说明

简介

此文介绍了在I/O drivers 之后的logic。 7系FPGA包含了一些I/O logic resources。 这些resources包括了:

• Combinatorial input/output

• 3-state output control

• Registered input/output

• Registered 3-state output control

• Double-Data-Rate (DDR) input/output

• DDR output 3-state control

• IDELAY provides users control of an adjustable, fine-resolution delay taps

• ODELAY provides users control of an adjustable, fine-resolution delay taps

• SAME_EDGE output DDR mode

• SAME_EDGE and SAME_EDGE_PIPELINED input DDR mode

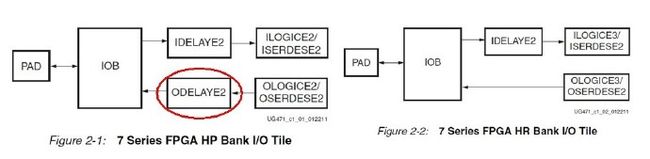

下面是两个Bank的 I/O tile 的对比。 在IOB(Input/Output Buffer)中包括了SeletctIO input,output,和3-state drivers。 两个Bank的的差异就在于HP bank 多一个单独的 ODELAYE2。

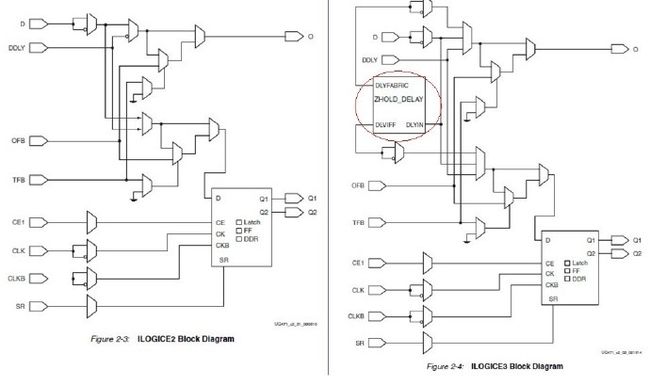

ILOGIC block 在IOB的旁边。 ILOGIC block 包含了一些同步元素来捕获data(好像从IOB进入FPGA一样)。

在HP bank中使用ILOGICE2,在HR bank中使用ILOGICE3。 除了特定的情况, ILOGICE2,ILOGICE3在功能和端口上是一样的。 两个ILOGICE只有一点不同:

HR bank中的是ILOGICE3,而且有一个ZHOLD(Zero Hold Delay Element)

HP bank中的是ILOGICE2,而且没有这个ZHOLD元件。

在图中可以如下表示:

ILOGICE2和ILOGICE3 两个不属于原语,所以他们不能被实例化。 不过他们在place和route之后包括了可以被实例化的元件,例如IFD(Input Flip-Flop) 或者IDDR(input DDR)。

ILOGIC可以支持以下操作:

• Edge-triggered D-type flip-flop

• IDDR mode (OPPOSITE_EDGE or SAME_EDGE or SAME_EDGE_PIPELINED).

• Level sensitive latch

• Asynchronous/combinatorial

ILOGIC block registers有一个通用clock enable signal(CE1) 默认为HIGH有效。若是不连接,此clock enable pin在任何storage元件都是默认为有效状态。

ILOGIC block registers有一个通用的同步或者非同步set和reset(SR signal) 。 此set/reset input pin或者SR, 促使storage 元件进入SRVAL定语指定的状态。reset 条件比set 条件的优先级高。

SRVAL定语可以在ILOGIC block为每个storage元件单独设置,但是不能为每个storage元件的set/reset单独设置同步或者非同步(SRTYPE)。

下面介绍一些IDDR的操作模式

combinatorial input path

此combinatorial input path 用来创建input driver到FPGA logic的直接连接。以下状况时,此path自动被软件使用:

1. 在FPGA logic中,有一个直接(unregistered)连接从input data 到logic resources。

2. pach i/o register/ latches into IOBs software map 命令设置为OFF

Input DDR Overview (IDDR)

在7系列设备的ILOGIC block中有专属的registers来实现input double-data-rate(DDR) registers。这些特性可以通过实例化IDDR 原语实现。

所有进入到I/O tile 的clocks都是完全多路复用的,即在ILOGIC和OLOGIC之间没有clock sharing。 IDDR原语支持如下的操作模式:

• OPPOSITE_EDGE mode

• SAME_EDGE mode

• SAME_EDGE_PIPELINED mode

在Virtex-6架构中,SAME_EDGE和SAME_EDGE_PIPELINED模式是一样的。这些模式允许设计者在ILOGIC block中把falling edge的data传输到rising edge domain里,节省CLB和clock resources,而且提高了性能。这些模式用DDR_CLK_EDGE定语可以实现。下面介绍详细介绍这些模式。

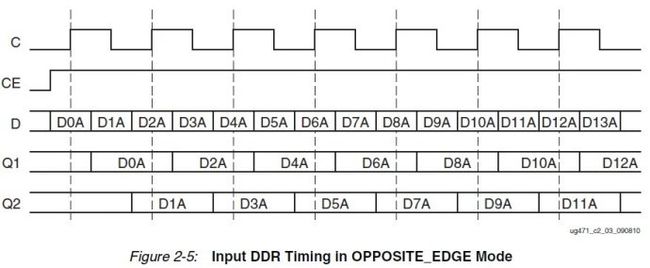

OPPOSITE_EDGE 模式

一个传统的DDR solution或者叫OPPOSITE_EDGE模式,通过在ILOGIC block中的一个single input完成的。输出Q1在clock的上升沿,Q2在clock的下降沿时,data输出到FPGA里。这个结构和Virtex-6 FPGA类似。下图显示了使用OPPOSITE_EDGE模式时,input DDR的时序图。

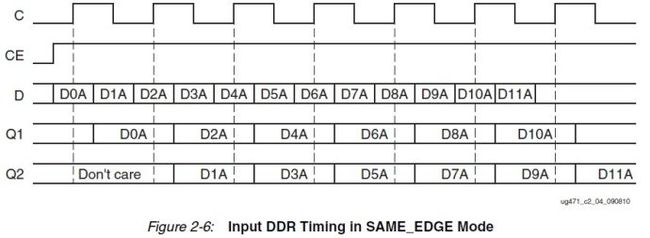

SAME_EDGE 模式

在SAME_EDGE模式中,data是在同样的clock edge中被送入FPGA logic中的。结构与Virtex-6 FPGA类似。

下图显示了使用SAME_EDGE模式的input DDR的时序图。在时序图中,输出对Q1和Q2不再是(0)和(1)。在第一对输出对视Q1(0)和Q2(don't care), 下一个cycle随之而来的则是输出对(1)和(2)。

SAME_EDGE_PIPELINED 模式

在SAME_EDGE_PIPELINED模式中,data也是在同样的clock edge中被送入FPGA logic中的。

和SAME_EDGE模式不同的是,data pair 不在一个clock cycle中分开。但是一个额外的clock latency要求被加入来除去SAME_EDGE模式中的分开效果。下图显示了使用SAME_EDGE_PIPELINE模式的input data 时序图。输出对Q1和Q2在同一时间被送入FPGA logic中。

下面介绍一下input DDR Resources(IDDR)

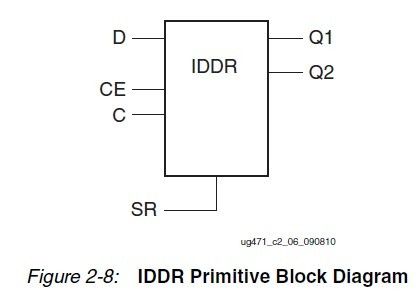

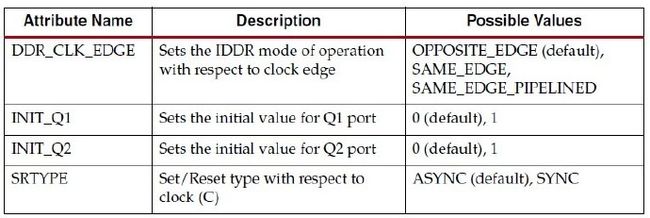

下图显示了IDDR原语的结构图。Set和Reset在同一时刻不能被支持。表1是IDDR的端口信号,表2描述了IDDR原语的各种定语和默认值。

表1:

// IDDR: Input Double Data Rate Input Register with Set, Reset

// and Clock Enable.

// 7 Series

// Xilinx HDL Libraries Guide, version 13.4

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

// End of IDDR_inst instantiation