PCI-E基础知识学习

PCIE特点:

(1)2种路由方式:基于地址的路由方式、基于ID(BDFR)的路由方式

(2)2种数据发送方式:Posted方式和No-Posted方式;

(3)多种总线事务:配置读写、内存读写、IO读写、消息

一、PCIe IP初始化

主要完成工作:链路训练及初始化、PCIe IP初始化

1、链路训练

(1)基本概念

1)PCIe链路结构:

一个Lane由收发2个方向组成,每个方向的硬件电路为差分电路。

2)实现功能:初始化PCIe设备的物理层、发送接收模块和相关的链路状态信息,链路训练结束后,PCIe链路两边的设备可以进行正常的数据交换,从而为PCIe总线拓扑结构扫描及PCIe设备配置空间初始化提供保证。

3)链路训练使用LTSSM(Link Training and Status State Machine)实现,位于PCIe总线的物理层之中。

4)链路训练过程由硬件逻辑完成,无需系统软件参与;

(2)训练过程

在PCIe链路可以正常工作之前,需要对PCIE链路进行链路训练,在这个过程中,就会用LTSSM状态机。LTSSM状态机涵盖了11个状态,包括Detect, Polling, Configuration, Recovery, L0, L0s, L1, L2, Hot Reset, Loopback, Disable。这11个状态之间转换的逻辑,如下图,

这11个状态大致可以分为4大类:

(1)PCIe链路训练相关。正常的PCIe链路训练状态转换流程依次是,Detect->Polling->Configuration->L0。L0是PCIe链路可以正常工作的电源状态。

各状态的作用:

1)Detect状态:用于检测PCIe链路上是否有PCIe设备存在,如果存在,一共使用了多少可用的Lane资源;

2)Polling状态:通过发送TS1、TS2序列来确定Bit Lock, Symbol Lock以及解决Lane极性反转的问题。Bit Lock锁定发送频率;Symbol Lock区分10-bit Symbol方法。

3)Configuration状态:协商Link Number和Lane Number;

4)L0状态:PCIe链路正常工作状态。这个状态可以传输TLP,DLLP等报文。

(2)PCIe链路重新训练相关。这个状态也称为Recovery。Recovery是一个非常重要的链路状态,进入这个状态的因素也很多,比如电源状态的变化,PCIe链路速率的变化等。

(3)电源状态相关。PCIe总线的电源状态主要有两部分的内容。

其一是基于软件控制的PCI-PM电源管理机制,是系统软件通过修改寄存器中的电源管理字段,使PCIe设备进入D状态:D0,D1,D2,D3.

其二是基于硬件控制的ASPM(=Active State Power Management)电源管理机制,是基于硬件自主控制的链路电源管理机制,只有在PCIe设备处于D0状态是才可以启动ASPM机制,另外,与ASPM有关的链路状态有L0s,L1(包括L1.1和L1.2)。

(4)其他相关。比如Hot Reset, Link Disable, Loopback等。

二、PCIe总线的拓扑结构

1、总线组成与拓扑

(1)拓扑结构组成

1)RC(Root Complex)

功能:主要作用是完成存储器域到PCI总线域的地址转换;

组成: 如果将RC中的RCRB、内置的PCI设备和Event Collector去除,该RC的主要功能与PCI总线中的HOST主桥类似。

2)Switch

(A)主要作用:链路扩展。因为PCIe总线使用端到端的连接方式,一条PCIe链路只能连接一个设备,当一个PCIe链路需要挂接多个EP时,需要使用Switch进行链路扩展。

(B)特性

A)每一个PCIe链路占用一个PCI总线号。

B)Switch内部由多个虚拟PCI桥组成,每个端口(上游、下游)对应一个虚拟PCI桥。一个Switch内部就有多少个虚拟PCI桥,就有多少个PCI桥配置空间。

C)在Switch内部还具有一条虚拟的PCI总线,用于连接各个虚拟PCI桥,系统软件在初始化Switch时,需要为这条虚拟PCI总线编号。

Switch的组成结构如图所示。

Switch需要解决的问题:

A)Switch需要处理PCIe总线传输过程中的QoS问题。PCIe总线的QoS要求PCIe总线区别对待优先权不同的数据报文,而且无论PCIe总线的某一个链路多么拥塞,优先级高的报文,如等时报文(Isochronous Packet)都可以获得额定的数据带宽。而且PCIe总线需要保证优先级较高的报文优先到达。

解决这个问题的办法是PCIe总线采用虚拟多通路VC技术,并在这些数据报文设定一个TC(Traffic Class)标签,该标签由3位组成,将数据报文根据优先权分为8类,这8类数据报文可以根据需要选择不同的VC进行传递。

-----------------------------------------------------------------------------------------

VC与TC、端口仲裁

在PCIe总线中,每一条数据链路上最多可以支持8个独立的VC。每个VC可以设置独立的缓冲,用来接收和发送数据报文。在PCIe体系结构中,TC和VC紧密相连,TC与VC之间的关系是“多对一”。

TC可以由软件设置,系统软件可以选择某类TC由哪个VC进行传递。其中一个VC可以传递TC不相同的数据报文,而TC相同的数据报文在指定一个VC传递之后,不能再使用其他VC。在许多处理器系统中,Switch和RC仅支持一个VC,而x86处理器系统和PLX的Switch中可以支持两个VC。

-----------------------------------------------------------------------------------------

B)流量控制机制防止拥塞。

3)EP

类似于PCI Agent设备;

2、总线扫描

具体见《5 PCIe总线扫描》,链路训练完成后,开始总线扫描,初始化相应PCIe的设备配置空间参数。

(1)主要功能

(A)PCIe总线BUS\DEV\FUNC编号;

(B)PCIe总线上挂载的PCIE设备使用的PCIe总线地址空间的分配;

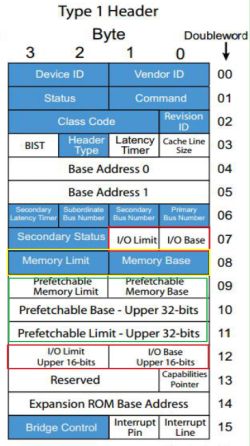

(C)拓扑结构中所有PCIe设备(RC\Switch(virtual pci bridge)\EP)配置空间的初始化(基本配置空间、扩展配置空间);在处理器系统上电之后,需要进行PCI总线系统的枚举,为PCI总线分配总线号,并设置Switch、PCIe桥片或者EP的配置寄存器,如Limit寄存器组、Base寄存器组、BAR寄存器、Subordinate Bus Number、Secondary Bus Number和Primary Bus Number等一系列配置寄存器。Subordinate Bus Number、Secondary Bus Number和Primary Bus Number寄存器在Type 01h配置寄存器中,用来描述PCI-to-PCI桥片的上游及下游总线号。

在PCIe的拓扑结构中,每一个PCIe设备(EP\Virtual PCI桥\PCI设备)均由一个唯一的身份ID,即bus:device:func,这是系统软件在初始化时使用DFS算法扫描配置的。从bus:device:func为0:0:0开始,每过一个桥都要更新一下已经有的设备的这三个号,一般的交换机的端口视为一个虚拟桥。要区别每一个桥下面是否挂有EP设备,有些交换机的端口是作特殊用途的。 在枚举过程中,需要分配设置交换的memory accesss和mem base limit寄存器,以分配PCIE空间的地址。将枚举结果存放到一个结构体链表中,方便查询使用。

(2)扫描原理

PCI设备的扫描是基于深度优先搜索算法(DFS:Depth First Search)。下级分支最多的PCI桥将最先完成其子设备的扫描。

PCI Host主桥(RC)扫描Bus 0上的设备(在一个处理器系统中,一般将与HOST主桥(RC)直接相连的PCI总线被命名为PCI Bus 0),系统首先会忽略Bus 0上的EP设备,然后发现Bridge 1后,将Bridge1 下面的PCI Bus定为 Bus 1,系统将初始化Bridge 1的配置空间,并将该桥的Primary Bus Number 和 Secondary Bus Number寄存器分别设置成0和1,以表明Bridge1 的上游总线是0,下游总线是1,由于还无法确定Bridge1下挂载设备的具体情况,系统先暂时将Subordinate Bus Number设为0xFF。然后系统继续扫描Bus 0上的设备,以此类推。最后完成PCIE总线拓扑结构的中相关PCIe设备的初始化。

三、PCIe设备的配置空间

1、PCIe配置空间的分配

(1)配置空间的分配

PCIe总线规定,在一个PCI总线域空间中,最多只能有256条PCI总线,因此在一个TLP中,Bus Number由8位组成;而在每一条总线中最多包含32个设备,因此TLP中的Device Number由5位组成;而每一个设备中最多包含8个功能,因此一个TLP的Function Number由3位组成。

注意:

PCIe链路采用端到端的通信方式,每一个链路只能挂接一个设备,因此在多数情况下,使用3位描述Device Number是多余的,因此PCIe总线提出了ARI格式,PCIe总线引入ARI格式的依据是在一个PCIe链路上仅可能存在一个PCIe设备,因而其Device号一定为0。在多数PCIe设备中,Requester ID和Completion ID包含的Device号是没有意义的。使用ARI格式时,一个PCIe设备最多可以支持256个Function,而传统的PCIe设备最多只能支持8个Function。

因此,由Bus:Device:Function(BDF)构成了每个Function(子设备)的唯一的"身份证号".

配置空间是针对function而言的,每个function都有其配置空间,每个Function(子设备)都有一个大小为4KB的配置空间。

可以计算,所有PCIE设备(包括Host主桥、虚拟PCI桥、EP)一共需要256(Bus)*32(Dev)*8(Func)*4KB=64*1024*4KB=256MB的内存空间。

其中,Host Bridge对应的是256MB Memory Block的起始地址(PCIEXBAR),其他Bridge、Dev按照顺序往后排序。

在系统上电的过程中会扫描整个PCI Bus,然后将所有的BDF的配置读到Host内存中。在Host内存中有一个256MB的Memory Block, 专门用来存放所有PCIe设备的配置空间。

(2)PCIe设备配置空间的结构

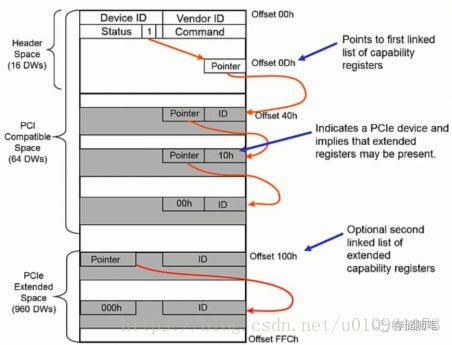

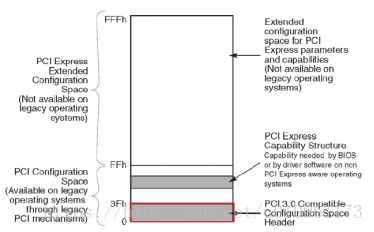

由上图可知,PCIe配置空间有两部分组成:传统PCI配置空间、PCIe扩展配置空间;

PCI配置空间的大小是256个字节,即0x00~0xFF,而PCIe的配置空间为4KB,即0x00~0xFFF。其中,PCIe扩展配置空间是通过原来PCI配置空间中的Capability Pointer的寄存器块来完成的。

原来PCI配置空间中的Capability Pointer的寄存器保存了第一个Capability的位置,而第一个Capability又指定下一个Capability,构成了一串Capability,具体如下图所示:

各个不同的Capability的作用不同,且不同的设备有不同的Capability。

(3)PCIE Capability结构

在PCI/PCIe系统中,总共定义了14种Capability ID(如下图),在我们平时使用过程中,主要关注4个就可以了:01,05,10,11.

1)Capability ID=01

Power Management Capability Structure定义如下:

2)Capability ID=05

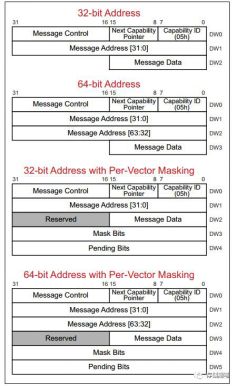

MSI Capability Structure定义如下:

在PCIe总线中,MSI中断机制使用Memory Write TLP向处理提交中断请求。PCIe设备提交MSI中断请求时,需要向MSI Capability结构中的Message Address的地址写入Message Data数据。根据Address的长度(32位或者64位)以及是否Mask中断向量,MSI Capability结构分为四类如下图:

3)Capability ID=10

PCIe Capability Structure定义如下:

4)Capability ID=11

MSI-X Capability Structure定义如下:

MSI-X与MSI的机制基本相同,不过,MSI中断机制最多支持32个中断请求,并且要求中断向量连续。而MSI-X中断机制可以支持2048个中断请求,并且不要求中断向量连续。与MSI Capability寄存器相比,MSI-X Capability寄存器使用了一个数组存放Message Address字段和Message Data字段,而不是将这两个字段放入Capability寄存器中,这个数组称为MSI-X Table。所以,MSI-X Capability寄存器比MSI Capability寄存器要小,具体格式如下图,

2、PCIe配置空间Header详解

PCIe设备4KB 配置空间主要有3部分构成:

• Byte 0 - 63(0x3F): 代表的是PCI配置Header;

• Byte 128(0X80) - 255: 代表的是PCI Capability Structures,这部分会记录对应Function所具备的技能;

• Byte 256 - 4095: 这3840B代表是PCIe扩展配置空间。

注:重点提一下前0~255B的内容,PCIe扩展空间不再展开阐述。

PCIe配置Header具有两种格式:Type0和Type1。

Type0主要用于访问PCI Agent \EndPoint的配置空间;

Type1主要用于访问Switch\Bridge的配置空间;

(1)Type0类型的配置Header

Type0主要用于访问PCI Agent \EndPoint的配置空间;

简单介绍其中的几个寄存器的意义:

1)Vendor ID,Device ID:标记了一个设备的生产厂商和具体的设备,比如Intel的设备Vendor ID通常是0x8086,Device ID就需要厂家自定义了,总之能够识别到具体是哪个设备就可以了。

2)Status:设备状态字,具体每个BIT的意义见下图:

3)Command:设备状态字:

4)RevisionID:记载PCI设备的版本号

5)Class Code:记载PCI设备的分类。包含:Base Class Code\Sub Class Code\Interface 3个字段,

Base Class Code:将PCI设备分类为显卡、网卡、PCI桥等设备;

Sub Class Code:对相应设备进一步细分;

Interface:定义编程接口

6)Base Address Registers:表明PCIe设备空间在系统空间中的映射位置;映射方式有两种,分别是IO映射和Memory映射,处理器系统资源分为IO资源和MM资源两种,因此PCI/PCIe空间地址对应也有两种。

(2)Type1类型的配置Header

Type1主要用于访问Switch\Bridge的配置空间;

1)Vendor ID,Device ID,Status,Command等寄存器同Type0。

2)BAR计算得到的系统空间是该桥下挂的所有设备的系统空间的总和。

3)Subordinate Bus Number、Secondary Bus Number和Primary Bus Number,这些寄存器共同确定了该桥上行和下行的所有Bus号。

4)Base\Limit寄存器:包括存储器Base\Limit寄存器、IO Base\Limit寄存器、预取存储器Base\Limit寄存器。这两个寄存器代表“该桥所管理的PCI子树”存储器或IO的基地址和长度;

3、PCIe配置空间的访问

(1)背景知识拓展

CPU对于外设的访问,一般会有两种方式:内存映射方式、IO映射方式;

1)内存映射方式

这种方式下,外设寄存器和系统内存统一编址,于是对外设寄存器的访问和内存访问一样,不需要额外的指令。

2)IO映射方式

这种方式下,外设和系统内存分属不同的体系,所以访问外设需要另外的指令。X86体系的CPU就是用的I/O映射方式,外设寄存器访问指令为IN和OUT。和内存访问地址空间不同的是:I/O访问指令的地址空间只有从0~65535。

为了解决I/O访问端口不足的问题,PCI规范设计时就为每个设备定义了一个256字节的PCI配置空间。将PCI设备中需要用到的一些基本寄存器都集中存放在该区域。而所有的PCI设备中配置空间的访问只使用I/O地址0CF8H~0CFFH来访问。

(2)PCIe配置空间的访问方式

PCIe配置空间的访问有两种方式: I/O端口访问方式、ECAM方式。

1)I/O端口配置方式(CAM方式)

X86处理器定义了两个I/O端口寄存器,分别为CONFIG_ADDRESS寄存器(端口号:0xCF8h)和CONFIG_DATA寄存器(端口号:0xCFCh);

X86处理器使用CONFIG_ADDRESS寄存器、CONFIG_DATA寄存器访问PCIe设备的配置空间0x00-0xFF,

CONFIG_ADDRESS寄存器的结构如下:

CONFIG_ADDRESS寄存器存放PCI设备的ID号;CONFIG_DATA寄存器存放进行配置读写的数据。

当X86处理器对CONFIG_ADDRESS寄存器进行I/O读写访问,且CONFIG_ADDRESS寄存器的Enable位为1时,Host主桥将这个IO读写访问转换为PCI配置读写总线事务,然后发送到PCI总线上,PCI总线根据CONFIG_ADDRESS寄存器中的ID号,将PCI配置读写请求发送到指定PCI设备的配置寄存器中。

当X86处理器对CONFIG_DATA寄存器进行读写操作时,Host主桥将决定向PCI总线发送Type 00h配置请求还是Type 01h配置请求。具体过程如下:

处理器首先将目标PCI设备的ID号保存在CONFIG_ADDRESS寄存器中,之后,Host主桥根据该寄存器的Bus Number字段,决定是产生Type 00h配置请求还是Type 01h配置请求。当Bus Number字段为0时,产生Type 00h配置请求;当Bus Number字段大于0时,产生Type 01h配置请求。

2)ECAM方式

基本概念:PCIE设备配置空间的基地址保存在PCIEXBAR寄存器中,大小为256MB,当CPU对这段PCIe的配置空间进行读写访问时,RC会将这个存储器的读写请求转换为PCI配置读写总线周期,然后发送到相应PCIe的设备中。PCIe总线规范将这种“对PCIe设备配置空间”的读写访问方式称为“ECAM机制”。

基本原理:将处理器系统中所有PCIe设备的配置空间映射到一段地址连续的存储器域的地址空间中。CPU可以对这段存储器地址空间进行直接访问,从而访问PCIe设备的配置空间。

特点:

(A)ECAM机制是一种直接寻址的方式

(B)在X86处理器系统中,只有ECAM机制才可以访问PCIe设备的扩展配置空间。

(C)缺陷:地址空间的使用效率低。因为一条PCI总线上,PCIe设备不会使用所有的设备号,而且每一个PCIe设备也不会使用所有的Function号,这样,就会有很多的空间没有利用

实现:

(A)根据PCIe设备的Bus、Device、Fun、Register得到地址偏移值(offset);

(B)计算要访问的地址值,Address = PCIEXBAR + offset;PCIEXBAR不同的平台会不同

(C)RC将PCI总线域的Address映射到存储器域的Address;

(D)CPU访问存储器域的Address

四、PCIe设备的数据传输

0、PCI总线的数据访问方式

(1)概述

每个PCIe设备(PCI Agent设备/EP设备)均有自己的数据空间用于存放用户传输的数据。这些数据空间的基地址和大小存放在PCI Agent/EP配置空间的BAR寄存器中。

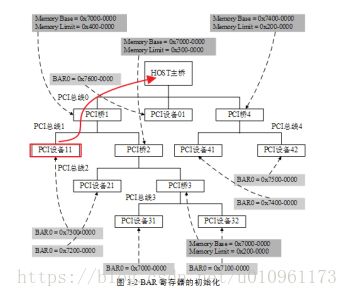

在PCI Agent设备进行数据传送之前,系统软件需要初始化PCI Agent设备的BAR0~5寄存器和PCI桥的Base、Limit寄存器。系统软件使用DFS算法对PCI总线进行遍历时,完成这些寄存器的初始化,即分配这些设备在PCI总线域的地址空间。当这些寄存器初始化完毕后,PCI设备可以使用PCI总线地址进行数据传递。

注意:PCI Agent设备的BAR0~5寄存器和PCI桥的Base寄存器保存的地址都是PCI总线地址。而这些地址在处理器系统的存储器域中具有映像,如果一个PCI设备的BAR空间在存储器域中没有映像,处理器将不能访问该PCI设备的BAR空间。

处理器通过HOST主桥(RC中的虚拟组件)将PCI总线域与存储器域隔离。

存储器域与PCI总线域之间的映射

不同的处理器系统采用不同的机制实现存储器域和PCI总线域的转换。如PowerPC处理器使用Outbound寄存器组实现存储器域到PCI总线域间的转换,并使用Inbound寄存器组实现PCI总线域到存储器域间的转换。

而x86处理器没有这种地址空间域的转换机制,因此从PCI设备的角度上看,PCI设备可以直接访问存储器地址;从处理器的角度上看,处理器可以直接访问PCI总线地址空间。但是读者需要注意,在x86处理器的HOST主桥中仍然有存储器域与PCI总线域这个概念。只是在x86处理器的HOST主桥中,存储器域的存储器地址与PCI总线地址相等,这种“简单相等”也是一种映射关系。

(2)访问原理

PCI设备的数据传递使用地址译码方式,当一个存储器读写总线事务到达PCI总线时,在这条总线上的所有PCI设备将进行地址译码,如果当前总线事务使用的地址在某个PCI设备的BAR空间中时,该PCI设备将使能DEVSEL#信号,认领这个总线事务。

如果PCI总线上的所有设备都不能通过地址译码,认领这个总线事务时,这条总线的“负向译码”设备将认领这个总线事务,如果在这条PCI总线上没有“负向译码”设备,该总线事务的发起者将使用Master Abort总线周期结束当前PCI总线事务。

1)处理器访问PCI Agent设备的BAR空间

当处理器访问PCI设备的地址空间时,需要首先访问该设备在存储器域中的地址空间,并通过HOST主桥将这个存储器域的地址空间转换为PCI总线域的地址空间之后,再使用PCI总线事务将数据发送到指定的PCI设备中。

2)PCI Agent设备使用DMA机制读写主存储器的数据

PCI设备访问存储器域的地址空间,即进行DMA操作时,也是首先访问该存储器地址空间所对应的PCI总线地址空间,之后通过HOST主桥将这个PCI总线地址空间转换为存储器地址空间,再由DDR控制器对存储器进行读写访问。

(3)PCI总线数据访问实例

1)地址空间规划

假设:

(1)存储器域的0xF000-0000~0xF7FF-FFFF(共128MB)物理地址空间与PCI总线的地址空间的0x7000-0000~0x77FF-FFFF存在映射关系;

(2)“PCI总线地址空间”为0x8000-0000~0xFFFF-FFFF与存储器域的地址范围为0x0000-0000~0x7FFF-FFFF之间存在映射关系;

当处理器访问存储器域的A1时,HOST主桥将会认领这个对存储器域A1的访问,并将这个访问转换为PCI总线域对B1空间的访问。

当PCI设备使用DMA机制,访问存储器域B2空间时,处理器系统同样需要将对B2存储器域访问反向映射到对PCI总线域A2空间。

2)PCI设备配置空间的初始化

主要是:BAR寄存器,Base、Limit寄存器初始化

系统初始化完成后,PCI Agent设备的BAR及PCI桥中Base\Limit寄存器的如下图所示。图中假定PCI Agent设备只用了BAR0寄存器,大小为16MB(0x1000000)

3)数据访问过程

(A)处理器到PCI设备数据传送

处理器向PCI设备11进行存储器写的数据传送过程为例,我们假设处理器使用存储器写指令,访问0xF300-0008这个存储器地址,其步骤如下。

(1) 存储器域将0xF300-0008这个地址发向HOST主桥,0xF000-0000~0xF7FF-FFFF这段地址已经由HOST主桥映射到PCI总线域地址空间,所以HOST主桥认为这是一个对PCI设备的访问。因此HOST主桥将首先接管这个存储器写请求。

(2) HOST主桥将存储器域的地址0xF300-0008转换为PCI总线域的地址0x7300-0008,并通过总线仲裁获得PCI总线0的使用权,启动PCI存储器写周期,并将这个存储器写总线事务发送到PCI总线0上。值得注意的是,这个存储器读写总线事务使用的地址为0x7300-0008,而不是0xF300-0008。

(3) PCI总线0的PCI桥1发现0x7300-0008在自己管理的地址范围内,于是接管这个存储器写请求,并通过总线仲裁逻辑获得PCI总线1的使用权,并将这个请求转发到PCI总线1上。

(4) PCI总线1的PCI设备11发现0x7300-0008在自己的BAR0寄存器中命中,于是接收这个PCI写请求,并完成存储器写总线事务。

(B)PCI设备DMA操作

PCI设备11向存储器进行DMA写的数据传送过程。假定PCI设备11需要将一组数据,发送到0x1000-0000~0x1000-FFFF这段存储器域的地址空间中。

DMA写具体的操作流程如下。

(1) 首先PCI设备11通过总线仲裁逻辑获得PCI总线1的使用权,之后将存储器写总线事务发送到PCI总线1上。值得注意的是,这个存储器写总线事务的目的地址是PCI总线域的地址空间0x9000-0000~0x9000-FFFF,这个地址是主存储器在PCI总线域的地址映像。

(2) PCI总线1上的设备将进行地址译码,确定这个写请求是不是发送到自己的BAR空间,在PCI总线1上的设备除了PCI设备11之外,还有PCI桥2和PCI桥1。

(3) 首先PCI桥1、2和PCI设备11对这个地址同时进行正向译码。PCI桥1发现这个PCI地址并不在自己管理的PCI总线地址范围之内,因为PCI桥片1所管理的PCI总线地址空间为0x7000-0000~0x73FF-FFFF。此时PCI桥1将接收这个存储器写总线事务,因为PCI桥1所管理的PCI总线地址范围并不包含当前存储器写总线事务的地址,所以其下所有PCI设备都不可能接收这个存储器写总线事务。

(4) PCI桥1发现自己并不能处理当前这个存储器写总线事务,则将这个存储器写总线事务转发到上游总线。PCI桥1首先通过总线仲裁逻辑获得PCI总线0的使用权后,然后将这个总线事务转发到PCI总线0。

(5) HOST主桥发现0x9000-0000~0x9000-FFFF这段PCI总线地址空间与存储器域的存储器地址空间0x1000-0000~0x1000-FFFF对应,于是将这段PCI总线地址空间转换成为存储器域的存储器地址空间,并完成对这段存储器的写操作。

(6) 存储器控制器将从HOST主桥接收数据,并将其写入到主存储器。

PCI设备间的数据传递与PCI设备到存储器的数据传送大体类似。

1、PCIe设备的总线事务

(1)背景知识

首先需要明确的一点是:

不同的总线事务--------->不同的TLP---------->不同的路由方式----------->数据转发方式的不同

由于不同的总线事务导致不同的TLP包类型,对于不同的TLP包,采用的路由方式也不一样。下面进行分别讲述。

包含存储器读写总线事务、IO读写总线事务、配置读写总线事务;

PCI总线中的事务是直接操作硬件,产生总线周期实现数据传递;

PCIe总线使用使用分层结构,由事务层完成相应总线事务的转换,根据不同的事务产生不同的TLP报文。

(2)总线事务类型

PCIe总线继承了PCI/PCI-X总线的大多数总线事务,如存储器读写(Memory Read/Write)、I/O读写、配置读写总线事务,并增加了Message总线事务和原子操作等总线事务。

扩展:PCIe中有两大类总线事务:Non-Posted和Posted:

1)Non-Posted: 需要completion返回响应包;

在PCIe总线中,Non-Posted总线事务分两部分进行,首先是发送端向接收端提交总线读写请求,之后接收端再向发送端发送完成(Completion)报文。PCIe总线使用Split传送方式处理所有Non-Posted总线事务,存储器读、I/O读写和配置读写这些Non-Posted总线事务都使用Split传送方式。

2)Posted: 不需要completion返回响应包.

PCIe的事务层还支持流量控制(Flow control)和虚通路管理(Virtual Channel Management)等一系列特性,而PCI总线并不支持这些新的特性。

2、TLP类型

(1)TLP头部通用部分解析

(2)TLP类型

在PCIe总线中,存储器读写请求、IO读写请求和配置读写请求由以下几类报文组成;

(1) 存储器读请求TLP和读完成TLP

当PCIe主设备,RC或者EP,访问目标设备的存储器空间时,使用Non-Posted总线事务向目标设备发出存储器读请求TLP,目标设备收到这个存储器读请求TLP后,使用存储器读完成TLP,主动向主设备传递数据。当主设备收到目标设备的存储器读完成TLP后,将完成一次存储器读操作。

(2) 存储器写请求TLP

在PCIe总线中,存储器写使用Posted总线事务。PCIe主设备仅使用存储器写请求TLP即可完成存储器写操作,主设备不需要目标设备的回应报文。

(3) 原子操作请求和完成报文

原子操作由PCIe V2.1总线规范引入,一个完整的原子操作包括原子操作请求和原子操作完成报文组成。原子操作的使用方法与其他Non-Posted总线事务类似,首先PCIe主设备向目标设备发送原子操作请求,之后目标设备向主设备发送原子操作完成报文,结束一次原子操作。有关原子操作的详细说明见第5.3.5节。

(4) I/O读写请求TLP和读写完成TLP

在PCIe总线中,I/O读写操作使用Non-Posted总线事务,I/O读写TLP都需要完成报文做为回应。只是在I/O写请求的完成报文中不需要“带数据”,而仅含有I/O写请求是否成功的状态信息。

(5) 配置读写请求TLP和配置读写完成TLP

主要作用:读写PCIe总线的EP、Switch及PCIe桥片的配置寄存器,以完成PCIe总线的配置。

传输方式:Non-Posted,配置读写请求TLP都需要配置读写完成作为应答,从而完成一个完成的配置读写操作。

路由方式:基于ID路由

特性:只能由RC发出

(6) 消息报文

与PCI总线相比,PCIe总线增加了消息请求事务。PCIe总线使用基于报文的数据传送模式,所有总线事务都是通过报文实现的,PCIe总线取消了一些在PCI总线中存在的边带信号。在PCIe总线中,一些由PCI总线的边带信号完成的工作,如中断请求和电源管理等,在PCIe总线中由消息请求报文实现。

3、PCIe总线路由方式

TLP路由指的是通过Switch或PCIe桥片采用哪条路径,最终到达EP或RC的方法,

PCIe总线一共有三种路由方法:

基于地址的路由方法、基于ID的路由方法、隐式路由方法

(1)基于地址的路由方法

1)特性

A.适用对象:存储器读写和I/O读写请求TLP;

B.原理:使用TLP头中的Address字段进行路由选择,最终到达目的地;

C.PCIe使用的地址路由方式与PCI使用的地址路由方式类似,只是PCIe设备使用TLP进行数据传送,而PCI设备使用总线周期进行数据传送;

2)原理详解

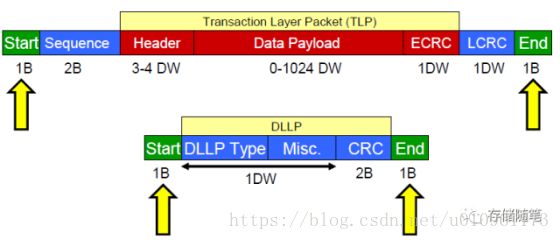

先来看一下TLP数据包的整体格式

然后看一下TLP的头部格式

使用地址路由方式使用的TLP头格式如图所示,这类TLP中包含目的设备的地址。

当这种TLP经过Switch时,Switch将根据TLP头中的目的地址将报文传递到合适的Egress端口上。

关于如何传递?下面具体讲解

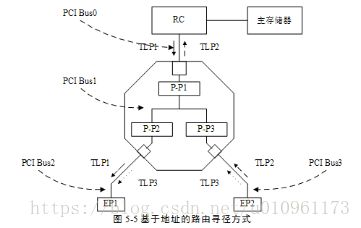

每个虚拟PCI桥的配置空间中使用了3组寄存器空间描述PCI下游子树的使用情况。这3组分别为I/O空间、存储器空间和可预取的存储器空间,分别用Base和Limit两类寄存器描述,其中Base寄存器表示可访问空间的基地址,Limit寄存器表示可访问空间的大小。TLP使用基于地址的路由时,一定要通过查询这组寄存器之后,再决定传送路径。如下图所示。

在虚拟PCI桥的配置寄存器空间中,包含该PCI桥能够接收的物理地址范围。PCIe总线通过这个物理地址范围实现基于地址的路由。

当系统软件初始化PCI总线时,将合理地设置PCI桥的寄存器,之后当TLP通过这些Switch时将根据这些寄存器选择合适的路径。

问题:TLP的发起方如何知道要访问空间的地址?也就是说每个EP是如何识别的?

猜想:

A.从软件的角度来考虑,用什么代表1个PCI Agent设备?一段内存空间

B.

3)实例

TLP1--TLP3均为IO读写请求或存储器读写请求TLP类型。

A TLP1的传送过程

TLP1为RC访问EP空间

(A)RC中形成TLP

TLP1目的地址在EP1的BAR空间

TLP中的目的地址是如何得到的?

当处理器访问EP的BAR空间时,需要使用该类TLP。BAR保存的是该设备在PCI总线域中地址,这个数据报文在通过RC时需要进行地址转换。

(B)TLP1通过PCI Bus0发向Switch,并通过Switch的Upstream端口到达P-P1桥片;

(C)P-P1桥片根据配置寄存器中的Limit和Base寄存器决定是否接收TLP1;

如果Switch不接收TLP1,则将该TLP作为不支持的请求(Unsupported Request)处理,此时如果TLP1需要回应报文,Switch将发出完成报文,该报文的状态为UR(Unsupported Request);

如果Switch接收TLP1,则表示TLP1所访问的地址在该Switch下游端口所连接的EP或者Switch中,此时Switch将TLP1从PCI Bus0推至PCI Bus1中,即穿越P-P1桥片;

(D)TLP1到达PCI Bus1后将同时查找P-P2和P-P3桥片配置寄存器中的Limit和Base寄存器,决定是P-P2还是P-P3桥片接收TLP1;

(E)P-P2桥片接收TLP1,并将TLP1推至PCI Bus2,而PCI Bus2上的EP1将接收TLP1,完成整个地址路由。

B TLP2的传送过程

TLP2为EP访问处理器系统的主存储器;

(A)TLP2将请求发至P-P3桥片,在P-P3桥片配置寄存器的Limit和Base寄存器中不会包含TLP2所访问的地址,此时P-P3桥片将TLP2推至PCI Bus1。

(B) 当TLP2到达PCI Bus1时,检查在PCI Bus1总线上的P-P2桥片是否可以接收此TLP,如果不能接收则TLP2通过P-P1桥片传递到PCI Bus0,即到达RC。

(C)对于x86处理器而言,MCH也会完成PCI域地址空间到存储器域地址空间的转换,然后访问处理器中相应的存储器空间。

C TLP3的传送过程

TLP3的传递方式与TLP2的传递方式有些类似,当TLP3传递到PCI Bus1时,P-P2桥片将接收TLP3,并将TLP3传递到PCI Bus2上的EP1中。

TLP3在PCI总线域上进行数据传递,因此不需要进行PCI总线域到存储器域的地址转换。

(2)基于ID的路由方法

1)特性

A.适用对象:配置读写TLP报文、Cpl和CplD报文、“Vendor_Defined Messages”报文

B.基本原理:使用PCI总线号(Bus Number)进行路由选择。使用Bus Number、Device Number和Function Number进行路由寻址。每一个PCIe设备使用唯一的PCI设备号,但是每一个设备仍然可以有多个子设备(Function)。

C.在Switch或者多端口RC的虚拟PCI桥配置空间中(每个Port对应一个虚拟PCI桥),包含如何使用PCI总线号进行路由选径的信息。

2)原理详解

先看一下“基于ID路由的TLP头”格式

如下图所示,

当PCIe主设备(RC\EP)发出“基于ID的TLP”后,Switch端口对应的虚拟PCI桥会根据配置空间中的Bus Number、Device Number和Function Number与TLP中的Bus Number、Device Number和Function Number进行对比,如图所示,

如果该TLP的Bus Number在虚拟PCI桥片的Secondary Bus Number和Subordinate Bus Number寄存器之间,则该虚拟PCI桥片将此TLP直接转发到下一跳的PCI Bus上。

当一个TLP从EP2传送到EP1或者RC时,首先检查P-P3桥片的配置空间,P-P3桥片发现该TLP不是发向自己时,将该TLP推至上游总线,即PCI Bus 1。如果PCI Bus1上P-P1桥片没有认领该TLP,该TLP将继续向P-P2桥片传递,并由这个桥片将TLP转发给合适的EP;如果P-P1桥片认领该TLP,该TLP将继续向上游总线传递,直至RC。

3)实例

包括配置读写TLP报文、Cpl和CplD报文

(A)配置读写TLP报文

配置读写请求TLP由RC发起,用来访问PCIe设备的配置空间。配置请求报文使用基于ID的路由方式。PCIe总线也支持两种配置请求报文,分别为Type 00h和Type 01h配置请求。

A)TLP报文头格式

第4-7字节与存储器请求TLP类似。

第8-11字节的Bus、Device和Function Number中存放该TLP访问的目标设备的相应的号码,而Ext Register和Reigister Number存放寄存器号。

配置请求报文的其他字段必须为以下值。

TC[2:0]必须为0,I/O请求报文的传送类型(TC)只能为0。

TH位为保留位;Attr2位为保留,而Attr[1:0]必须为“00b”,这表示I/O请求报文使用PCI总线的强序数据传送模式;AT[1:0]必须为“0b00”,表示不进行地址转换。

Length[9:0]为“0b00 0000 0001”,表示配置读写请求最大Payload为1DW。

Last DW BE字段为“0b0000”。而First DW BE字段根据配置读写请求的大小设置。

B)拓扑实例

C)访问步骤

RC在发送配置读写TLP之前,如何确定发送TLP的类型?

(a)Type 00h读写请求TLP

这种TLP主要用于配置与PCIe Bus总线直接相连的EP设备的空间。PCIe总线的Type 00h类型配置请求TLP不能够穿越桥片。

步骤:

a)RC使用Type 00h配置请求TLP访问在PCI Bus0总线上的所有设备;

b)PCI Bus0上的所有设备,包括虚拟PCIE桥片都要监听PCI Bus 0上的配置请求。由于只有Switch挂接在PCI Bus0上,因此Switch的上游端口将接收RC发出的Type 00h配置请求TLP;

c)Switch将向RC发出完成报文,结束配置请求。

(b)Type 01h读写请求TLP

这种TLP主要用于配置与PCIe Bus总线相连的Switch空间。

a)RC使用Type 01h配置请求TLP访问在PCI Bus0总线上的所有设备;

b)Switch中的虚拟P-P1桥检查该TLP的Bus Number是否为1。

c)如果TLP的Bus Number为1表示该TLP的访问目标在PCI Bus 1总线上,此时虚拟P-P1桥将这个Type 01h类型的TLP转换为Type 00h类型的TLP,然后推至PCI Bus 1总线,并访问其下的设备。

d)如果该TLP的Bus Number在虚拟P-P1桥片的Secondary Bus Number和Subordinate Bus Number寄存器之间,则虚拟P-P1桥片将该Type 01h类型的TLP直接转发到PCI Bus 1上,并不改变该TLP的类型;

e)Type 01类型的TLP将继续检查P-P2和P-P3桥片的配置空间,决定由P-P2还是P-P3接收该TLP。如果TLP的PCI Bus Number为2时,P-P2桥片将接收该TLP,并将该Type 01h类型TLP转换为Type 00h类型的TLP,然后推至PCI Bus 2总线,并访问其下的设备。

f)EP1处理该TLP,完成后,发送完成报文(完成报文的发送见下);

(B)完成报文

包含的TLP类型:存储器读完成TLP、I/O读写完成TLP、配置读\写请求TLP、配置读\写完成TLP、原子操作请求TLP以及ATS机制相关的一些报文。

TLP头格式

(3)隐式路由方法

1)特性

适用对象:消息请求报文。

PCIe总线规定了以下几类消息报文:

a.INTx中断消息报文(INTx Interrupt Signaling)。

b.电源管理消息报文(Power Management)。

c.错误消息报文(Error Signaling)。

d.锁定事务消息报文(Locked Transaction Support)。

e.插槽电源限制消息报文(Slot Power Limit Support)。

f.Vendor-Defined Messages。

基本原理:使用Msg和MsgD报文的Route字段进行路由;

2)原理详解

先看一下TLP格式头

| Route[2:0] |

描述 |

| 000 |

路由到RC |

| 001 |

使用地址路由 |

| 010 |

使用ID路由 |

| 011 |

来自RC的广播报文 |

| 100 |

本地消息,在接收端结束(Legacy中断消息使用这种报文格式,传递来自PCI总线的中断报文) |

| 101 |

用于PCIe电源管理(PME_TO_Ack报文使用) |

| 110~111 |

保留 |

由上表所示,使用隐式路由方式的TLP,其Route字段为“000”,“011”,“100”或者“101”。

(A)EP

当一个报文使用隐式路由向EP发送时,EP将对Route字段进行检查,如果这个报文是“来自RC的广播报文”,或者是“本地报文”,EP将接收此报文。

(B)Switch

如果Switch收到一条使用隐式路由的TLP时,将根据报文Route字段的不同而分别处理。

A.如果Switch的上游端口接收了一条来自RC的广播消息,则将该报文发向所有的下游端口;

B.如果Switch接收了一条来自下游端口发向RC的消息报文时,Switch将此报文直接转发到上游端口,直至RC;

C.如果Switch接收了一条使用隐式路由方式的本地消息报文,则Switch接收并终结此报文,不再上传或下推。

(C)RC

如果RC收到一个使用隐式路由的TLP时,将根据报文Route字段而分别处理这些TLP。

A.如果该Route字段为0b000和0b101,RC将接收该TLP,并作相应的处理;

B.如果为0b100,RC将接收该TLP,并结束该TLP报文的传递。

3)实例