VHDL语言入门整理

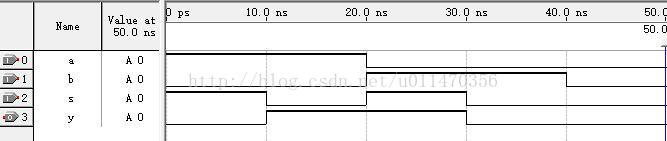

1.2选1多路选择器

Library ieee;

Use ieee.std_logic_1164.all;

Entity L1 is

Port

(

a,b,s:in std_logic;

y:out std_logic

);

End L1;

Architecture one of L1 is

Begin

Process(a,b,s)begin

If(s='0')then

y<=a;

Else

y<=b;

End if;

End process;

End one;

仿真结果:

2.4选1多路选择器

library ieee;

use ieee.std_logic_1164.all;

entity L2 is

port

(

a,b,c,d,s0,s1 : in std_logic;

y : out std_logic

);

end L2;

architecture two of L2 is

signal s : std_logic_vector(1 downto 0);

begin

s <= s1 & s0;

process(s1,s0) begin

case(s) is

when "00"=>y<=a;

when "01"=>y<=b;

when "10"=>y<=c;

when "11"=>y<=d;

when others=>null;

end case;

end process;

end two;

仿真结果:

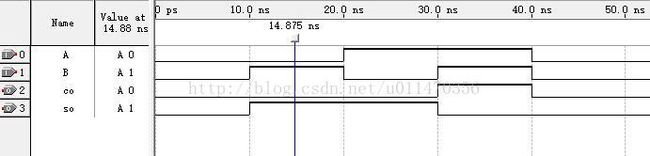

3.半加器

VHDL语言描述:

library ieee;

use ieee.std_logic_1164.all;

entity L3 is

port(

A,B:in std_logic;

so,co:out std_logic

);

end L3;

architecture three of L3 is

begin

so<=A xor B;

co<=A and B;

end three;

仿真结果:

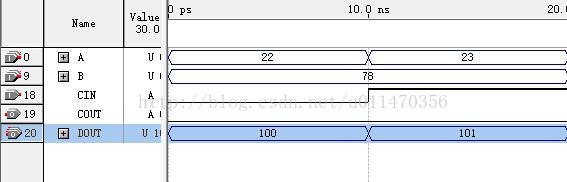

4.8位加法器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity L6 is

port(

A,B:in std_logic_vector(7 downto 0);

CIN:in std_logic;

COUT:out std_logic;

DOUT:out std_logic_vector(7 downto 0)

);

end L6;

architecture abc of L6 is

signal DATA:std_logic_vector(8 downto 0);

begin

DATA<=('0'&A)+('0'&B)+("00000000"&CIN);

COUT<=DATA(8);

DOUT<=DATA(7 downto 0);

end abc;

仿真结果:

5.D触发器的vhdl描述

library ieee;

use ieee.std_logic_1164.all;

entity L7 is

port

(

clk,D:in std_logic;

Q:out std_logic

);

end L7;

architecture abc of L7 is

signal Q1:std_logic;

begin

process(clk,Q1) begin

if clk'event and clk='1'

then Q1<=D;

end if;

end process;

Q<=Q1;

end abc;

仿真结果:

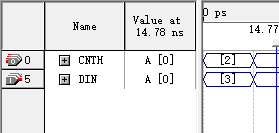

6.统计向量中1的个数

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity L7 is

port

(

DIN:in std_logic_vector(7 downto 0);

CNTH:out std_logic_vector(3 downto 0)

);

end L7;

architecture abc of L7 is

begin

process(DIN)

variable Q:std_logic_vector(3 downto 0);

begin

Q:="0000";

for n in 0 to 7 loop

if(DIN(n)='1') then

Q:=Q+1;

end if;

end loop;

CNTH<=Q;

end process;

end abc;

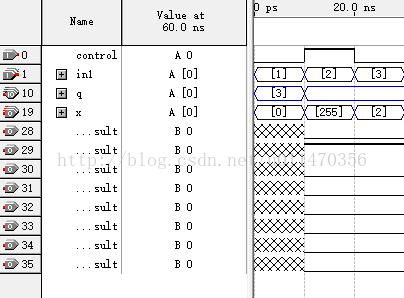

7.双向端口

library ieee;

use ieee.std_logic_1164.all;

entity L7 is

port

(

control :in std_logic;

in1:in std_logic_vector(7 downto 0);

q:inout std_logic_vector(7 downto 0);

x:out std_logic_vector(7 downto 0)

);

end L7;

architecture abc of L7 is

begin

process(control,q,in1)begin

if(control='0')then

x<=q;

else

q<=in1;

x<="11111111";

end if;

end process;

end abc;

仿真结果: