维特比译码器(Viterbi Decoder)硬件架构(二)--卷积码解码算法

1.网格图(Trellis Diagram)

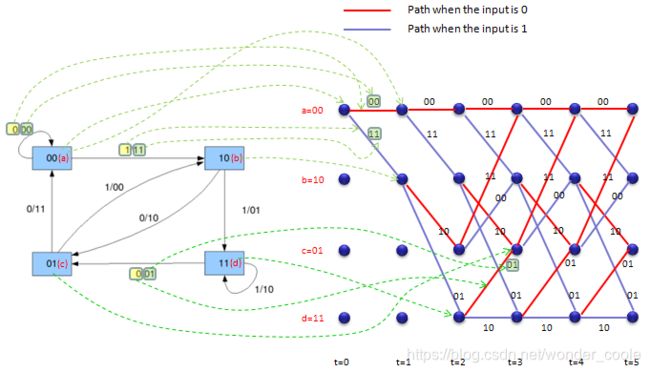

网格图(Trellis Diagram)是卷积解码用到的概念,是理解解码过程的基础。网格图是由按时间顺序排列的状态结点矩阵, 每一列代表当前时刻的所有状态,最左侧第一列代表初始状态(t=0),第二列代表第一个输入进入编码器后的转移状态。红色路径表示输入是0时的转移路径,蓝色表示输入为1时的转移路径。如下图所示,

- t=1时刻,只有两个从初始状态过来的转移路径,只存在2个可能的状态;

- t=2时刻,从t=1向t=2转移存在四个路径,此刻存在四种可能状态。

- t=3时刻,从t=2过来的转移路径有8条。

- 以此类推形成整个网格图(Trellis Diagram)

2.用网格图表示编码过程

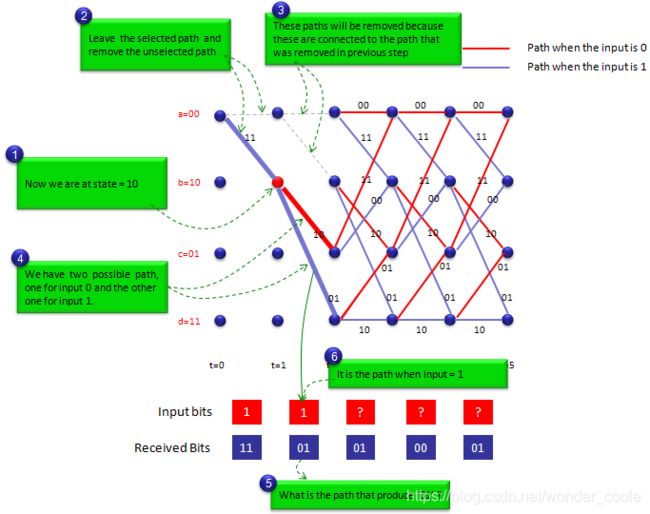

如下图所示,编码器初始状态为 state=‘00’,

- t=1,输入bit为1,走蓝色加粗线段所示的转移路径,转移后的状态为state= ‘10’, 编码输出为 ‘11’。

- t=2,输入bit为1,转移路径在上图中用蓝色加粗线段表示,转移后的状态为state= ‘11’ , 编码输出为 ‘01’。

- t=3,输入bit为1,转移路径在上图中用红色粗线表示,转移后的状态为state=‘11’ , 编码输出为 ‘01’。

- t=4,输入bit为0,转移路径在上图中用蓝色粗线表示,转移后的状态为state= ‘11’ , 编码输出为 ‘00’。

- 以此类推,可以形成编码过程的状态转移路径,也称幸存路径。

3. 解码过程

3.1 理想状态下的解码

卷积码的编码过程与网格图中的一条路径对应,即接收端接收到的序列的编码过程与网格图中的路径一一对应。当序列长度为L时,网格中有2L条不同的路径和编码器的2L种输入序列对应。在网格图中,每个状态转移的过程中都会输出编码码字。译码器建立和编码器相同的网格图, 据此查询可得到解码码流。

理想状况下,假设在传输过程中没有错误发生,在接收端,根据已经存在的网格图很容易解码得到原始比特流。

以tail-bits卷积码为例,假如接收端收到的比特流为’1101010001’, 先按2 bit宽度分组:11 01 01 00 01,解码过程如下:

- 从t=0的初始状态开始,tail-bits编码器的初始状态为’00’

- 查询输出为11时的转移路径,如下图粗线标志,此时编码器输入bit为1才能走该转移路径,因此可得到解码的第一bit:1

- t=1时,状态为‘10’,根据接收到的第二组‘01’,查询从该状态出发的两条转移路径

- 只有输入为0时,才能得到‘01’的输出,因此可得到此刻的转移路径,把其他无关路径删除。因此解码得到第二比特为0.

5. 以此类推,可在网格图上得到完整的状态转移路径及所有解码数据:11011.

现实中不会存在这种理想状态,信号经过复杂信道后均会引入不同程度错误,因此在接收端不会真正使用这种解码算法。

3.2 Viterbi译码算法原理

Viterbi算法 是CDMA之父,高通公司的创始人之一Andrew J. Viterbi在1967年提出的,它是基于卷积码网格图的最大似然译码算法。

最大似然译码 的一种基本想法是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列做为发送序列。如果发送L组信息比特对于(n,k) 卷积码来说,网格图上可能发送的序列有2kL 个,译码器需存储这些序列并进行比较,以找到码距最小的那个序列。

当传信率和信息组数L 较大时,使得译码器难以实现。Viterbi算法则对上述最大似然解码做了简化,成为了一种实用化的最大似然译码算法。它不是在网格图上一次性比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段有最大似然可能的码段,从而达到整个码序列是一个有最大似然值的序列。译码过程类似于动态规划的过程。

3.3 Viterbi译码中的几个概念

- 分支度量(BM, Branch Metric),对于网格中每个路径,分支度量表示其对应的输出码字与接收到的码字之间的差距。

- 路径度量(PM,Path Metric) 网格中每个状态节点而言,对应所有到达该节点所走过的最有可能路径的分支度量值的累计结果。

Viterbi译码过程的关键是,译码器可以使用分支度量和先前计算的状态路径度量递推地计算当前状态的路径度量. - 硬判决(Hard decision) 是指接收端根据其判决门限对接收到的信号波形直接进行判决后输出0或1,也就供给译码器作为译码用的每个码元只取0或1两个值,以序列之间的汉明距离作为度量进行译码。适用于二进制对称信道(BSC).

- 软判决(Soft decision) 是指接受端对采样点直接输出模拟量,进行多电平量化(不是简单的0、1两电平量化)形成多比特的数字量,然后送往译码器,即编码信道的输出是没有经过判决的“软信息”。软判决译码器以

欧几里德距离作为度量进行译码,软判决译码算法的路径度量采用“软距离”而不是汉明距离,最常采用的是欧几里德距离,也就是接收波形与可能的发送波形之间的几何距离,是一种适合于离散无记忆信道(DMC)的译码方法。 - 目前,通用的量化电平为8电平(3 bit量化)和16电平(4 bit量化),再高的话,只能增加译码器复杂度,几乎没有性能的提高。

- 除了度量的计算以外,软判决算法与硬判决算法在结构和过程上完全相同。一般而言,由于硬判决译码的判决过程损失了信道信息,软判决译码比硬判决译码性能上要好约2 dB。

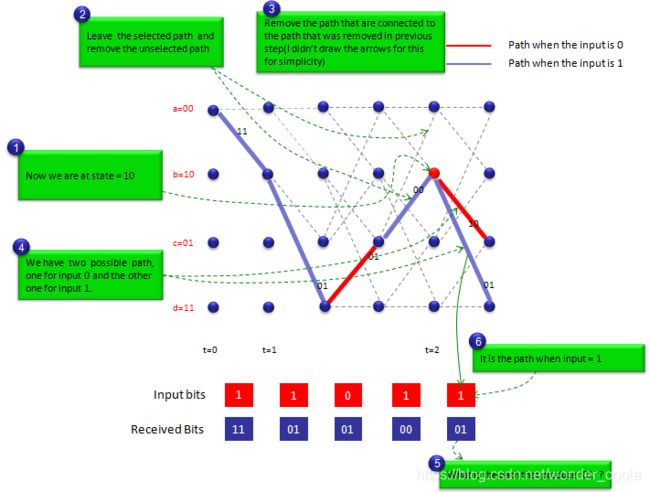

3.4 Viterbi译码过程

在当前时间t,对每个状态进行:

- 计算分支度量BM:即计算进入该状态的两个路径的分支度量(BM),即接收到的码元与两个路径对应的输出码元之间的汉明距离(硬判决)或欧几里得距离(软判决)。

- 计算路径度量PM:把两个路径的BM同各自对应的t-1时刻状态所存储的状态度量进行求和,得到t时刻的两个路径度量PM。

- 选取幸存路径: 比较两个路径度量PM,选取并保留最小的作为t时刻的状态度量,同时保留与之对应的路径作为形成路径。如两个相等,则任选其一作为幸存路径。

- 回溯(Traceback): 从各个状态的形成路径中选取出状态度量最小的一条,顺次向前进行回溯,并输出译码结果。

第2步第3步简称加比选(ACS), 是译码的核心步骤。

3.4 Viterbi译码所需的存储

- 每个状态需要记录当前累计的路径度量PM(可成状态度量),所以(n, k, L) 卷积码的译码需要2L 个寄存器记录状态度量。

- 如果回溯深度为N, 则每个时刻需要记录每个状态的幸存路径,

则需要深度为N,宽度为2Lbit的存储器存储幸存路径。

参考文献

- Encoding/Decoding - Presentation of Convolutional Code

- 翻译 | 卷积码的维特比(Viterbi)译码

- 软判决与硬判决的区别

本博客所有文章均同步发表于www.mx1980.cn/blog