计算机组成原理常见题(四)

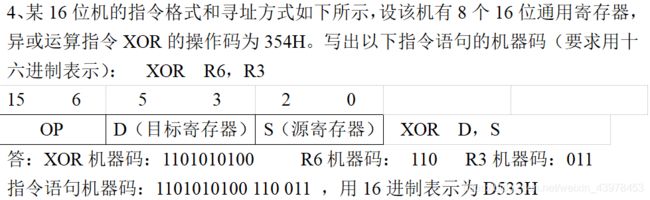

1.若某数采用IEEE 754单精度浮点数格式表示为 4510 0000H,则其值是( B )。

A、(+1.125)10×210 B(+1.125)10×211 C(+0.125)10×211 D、(+0.125)10×210

明确:IEEE754标准中32位定点机=数符1位+阶码(移码表示)8位+尾码(原码表示)23位,且默认尾数小数点前为1

2.假定计算机采用字节编址,小端方式,float型变量x的地址为FFFF C000H,x=1234 5678H,则在内存单元FFFF C001H中存放的内容是( C )。A.1234H B.34H C.56H D.5678H

什么是大小端:

1、大端模式

所谓的大端模式,是指数据的高字节,保存在内存的低地址中,而数据的低字节,保存在内存的高地址中,这样的存储模式有点儿类似于把数据当作字符串顺序处理:地址由小向大增加,而数据从高位往低位放;

例子:

0000430: e684 6c4e 0100 1800 53ef 0100 0100 0000

0000440: b484 6c4e 004e ed00 0000 0000 0100 0000

在大端模式下,前16位应该这样读: e6 84 6c 4e ( 假设int占4个字节)

记忆方法: 地址的增长顺序与值的增长顺序相反.

2、小端模式

所谓的小端模式,是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

例子:

0000430: e684 6c4e 0100 1800 53ef 0100 0100 0000

0000440: b484 6c4e 004e ed00 0000 0000 0100 0000

在小端模式下,前16位应该这样读: 4e 6c 84 e6( 假设int占4个字节)

记忆方法: 地址的增长顺序与值的增长顺序相同.

所以:本题中,FFFF C001H存放的是56H

3.5、考虑以下C语言代码:short si=-8196;int i=si;执行上述程序段后,i的机器数表示为( D )。A. 00009FFCH B. 0000DFFCH C. FFFF9FFCH D. FFFFDFFCH

十进制:-8196

二进制:1010 0000 0000 0100

反 码: 1101 1111 1111 1011

补码: 1101 1111 1111 1100

十六进制:DFFC 转换成int后,在前面补上两字节的1: FFFF DFFCH

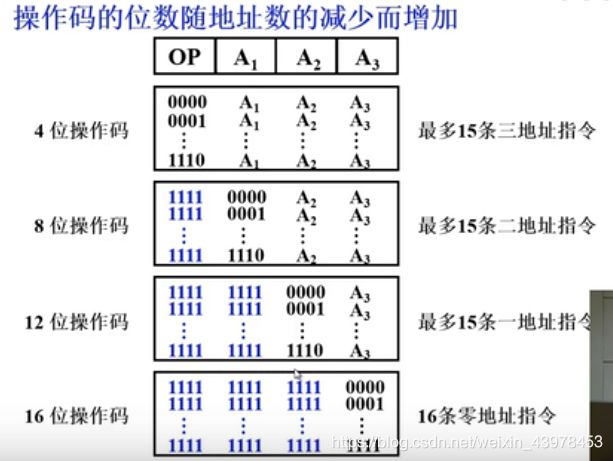

4.单地址双目运算类指令中,除地址码指明的一个操作数以外,另一个操作数通常采用( D )A.堆栈寻址方式 B.立即寻址方式 C.间接寻址方式 D.隐含指定方式

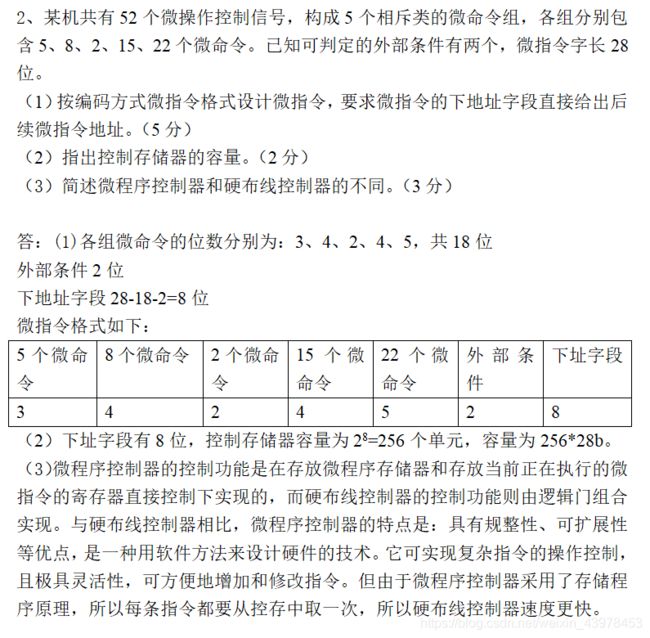

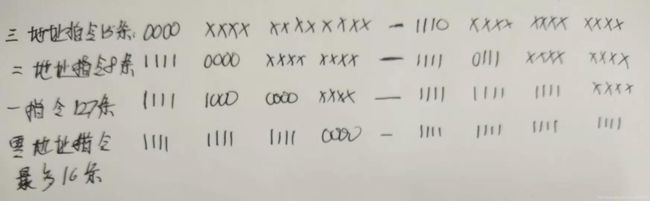

5.某计算机为定长指令字结构,采用扩展操作码编码形式,指令长度为16位,每个地址占4位,三地址指令15条,二地址指令8条,一地址指令127条,则剩下的零地址指令最多有( B )条。A. 15 B. 16 C. 31 D. 32

在本题中:

6.CPU中控制器的功能是( D )。A.产生时序信号 B.控制从主存取出一条指令 C.完成指令操作码译码 D. 完成指令操作码译码,并产生操作控制信号

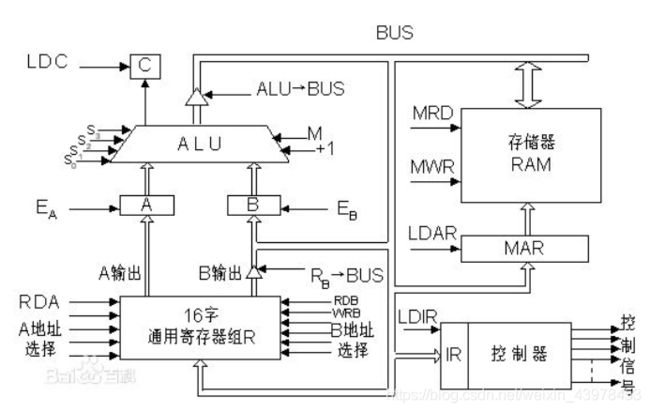

7.下列有关数据通路的叙述中,错误的是( D )。

A. 数据通路由若干操作元件和状态元件连接而成 B. 数据通路的功能由控制部件送出的控制信号决定 C.ALU属于操作元件,用于执行各类算术和逻辑运算 D.通用寄存器属于状态元件,但不包含在数据通路中

数据通路是指 在数字系统中,各个子系统通过数据总线连接形成的数据传送路径

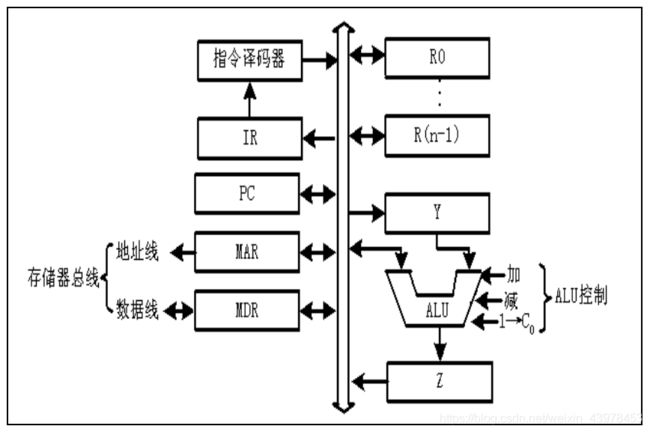

图中所示的数据通路中,两类信息的表示方式是非常明确的:双线表示数据信息,带箭头的单线表示控制信号。所有的控制信号由控制器产生,在它们的协调配合下,数据流通过BUS总线在各子系统之间进行流动。

8.以下有关流水段功能部件的描述中,错误的是( B )。

A. 所有功能部件都是用组合逻辑实现的 B. 同一功能部件可以在不同的流水段中被使用 C. 每个功能部件在每条指令中都只被使用一次 D. 寄存器写口只能在指令结束时的“写回”阶段被使用

9.下面有关半导体存储器组织的叙述中,错误的是( D )

A. 存储器的核心部分是存储体,由若干存储单元构成B. 存储单元由若干个存放0或1的存储元件构成C. 一个存储单元有一个编号,就是存储单元的地址D. 同一个存储器中,每个存储单元的宽度可以不同

10.某计算机主存容量为64KB,其中ROM区为4KB,其余为RAM区,按字节编址,现要用2K×8位的ROM芯片和4K×4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数和RAM芯片数分别是( D )

A . 1、15 B . 2、15 C . 1、30 D . 2、30

因为主存容量为64KB,其中ROM为4KB,所以RAM为60KB,需要ROM:4KBx8位/2KBx8位=2片

需要RAM:60KBx8位/4KBx4位=30片

11.以下有关RAID技术的叙述中,错误的是( C )。

A. RAID技术可实现海量后备存储系统B. RAID技术可提高存储系统的可靠性C. RAID中的校验信息通常都存放在一个磁盘上D. RAID通过多个盘并行访问来提高速度

RAID是“Redundant Array of Independent Disk”的缩写,中文意思是独立冗余磁盘阵列。

RAID磁盘阵列(Redundant Array of Independent Disks)

简单地解释,就是将N台硬盘通过RAID Controller(分Hardware,Software)结合成虚拟单台大容量的硬盘使用,其特色是N台硬盘同时读取速度加快及提供容错性Fault Tolerant,所以RAID是当成平时主要访问数据的Storage不是Backup Solution。

在RAID有一基本概念称为EDAP(Extended Data Availability and Protection),其强调扩充性及容错机制, 也是各家厂商如:Mylex,IBM,HP,Compaq,Adaptec,Infortrend等诉求的重点,包括在不须停机情况下可处理以下动作:

RAID 磁盘阵列支援自动检测故障硬盘;

RAID 磁盘阵列支援重建硬盘坏轨的资料;

RAID 磁盘阵列支援支持不须停机的硬盘备援 Hot Spare;

RAID 磁盘阵列支援支持不须停机的硬盘替换 Hot Swap;

RAID 磁盘阵列支援扩充硬盘容量等。

12.15、以下是有关对DMA方式的叙述,错误的是( B )。

① DMA控制器向CPU请求的是总线使用权② DMA方式可用于键盘和鼠标器的数据输入③ DMA方式下整个I/O过程完全不需要CPU介入④ DMA方式需要用中断处理进行辅助操作

A.①、② B.②、③ C.②、④ D.③、④

DMA方式,Direct Memory Access,也称为成组数据传送方式,有时也称为直接内存操作。DMA方式在数据传送过程中,没有保存现场、恢复现场之类的工作。

由于CPU根本不参加传送操作,因此就省去了CPU取指令、取数、送数等操作。内存地址修改、传送字 个数的计数等等,也不是由软件实现,而是用硬件线路直接实现的。所以DMA方式能满足高速I/O设备的要求,也有利于CPU效率的发挥

基本操作

实现DMA传送的基本操作如下:

1、外设可通过DMA控制器向CPU发出DMA请求;

2、CPU响应DMA请求,系统转变为DMA工作方式,并把总线控制权交给DMA控制器;

3、由DMA控制器发送存储器地址,并决定传送数据块的长度;

4、执行DMA传送;

5、DMA操作结束,并把总线控制权交还CPU。

名词解释:

1.超标量流水线

答:若干条指令同时启动并独立进入流水线执行。即:每个时钟周期发射多条指令,有多套取指部件和指令译码部件,并且同时有多条指令执行,所以应有多个执行部件。超标量流水线是一种多指令发射方式。

2、快表(TLB)

答:全称为Translation-Lookaside Buffer。**用一个特殊Cache来跟踪记录最近用过的页表表项。**页表表项主要用于地址转换,因为在TLB中查找页表项速度很快,所以TLB也被称为快表。TLB通常很小,一般用全相联方式或组相联方式。

3、中断向量

答:每个中断源都有处理程序,称这个处理程序为中断服务程序,其入口地址称为中断向量。

4、CPI

答:全称为Cycles Per Instruction,每条指令平均时钟周期数,是衡量CPU性能的一种基本参数。

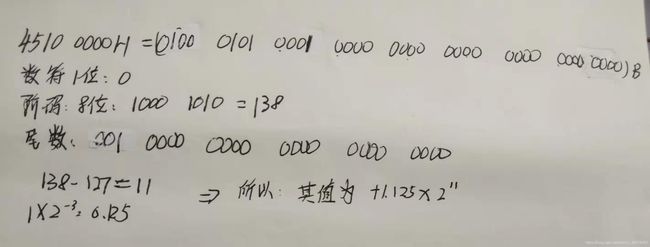

简答题

1.I/O端口有哪两种编址方式?各是什么含义?

答:两种编址方式为独立编址和统一编址。

独立编址是I/O端口和主存单元分别编号,不占主存单元的地址空间,I/O端口和主存单元可能有相同的编号,故需要专门的I/O指令;统一编址是I/O端口和主存单元在同一地址空间中的不同位置,可根据地址范围不同来区分访问的是I/O端口还是主存单元,故无需专门的I/O指令。

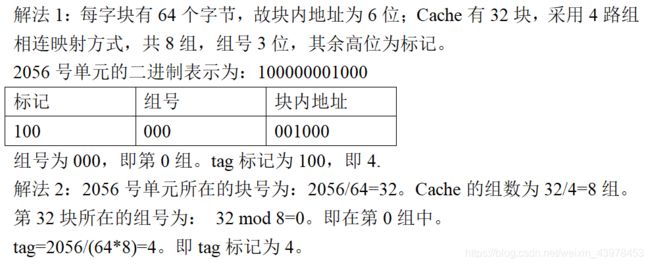

2.某计算机的Cache共有32块,采用4路组相连映射方式,每个主存块大小为64字节,按字节编址。主存号2056号单元所在主存块应装入到cache的组号是多少?tag标记是多少?给出分析过程。(Cache起始行为第0行,答案用十进制表示)

3.RISC和CISC有何不同?分别举出一个采用RISC、CISC的典型架构。

答: RISC是精简指令集计算机,CISC 复杂指令集计算机。RISC和CISC相比,指令数、指令格式、寻址方式少,通用寄存器多,采用组合逻辑,采用优化的编译技术,便于实现指令流水。RISC 便于设计,成本较低,可靠性较高。例如X86架构采用CISC,ARM和MIPS都采用RISC。

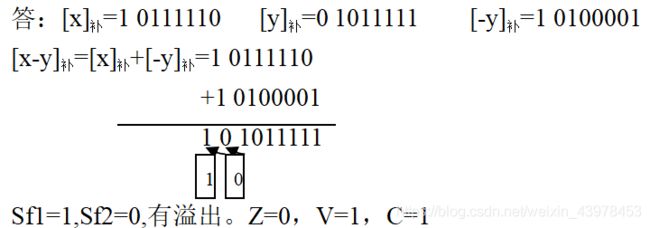

5、已知十进制数x= - 66,y=+95,设机器数字长8位(含1位符号位),先表示出[x]补、[y]补和[-y]补,用补码运算方式计算x - y,要求写出详细过程,判断是否溢出,并给出相应的Z(零标志)、V(溢出标志)和C(进位标志)。

分析题

1、假定某计算机字长16位,CPU内部结构如图所示,CPU和存储器之间采用同步方式通信,按字编址。采用定长指令字格式,指令由两个字组成,第一字指明操作码、寻址方式和一个寄存器编号,第二字为立即数imm16。若一次存储访问所用时间为2个CPU时钟周期(Read1和Read2分别表示两个时钟周期内的操作控制信号),每次存储访问存取一个字,取指令阶段第二次访存将imm16取到MDR中,请写出下列指令在执行阶段的控制信号序列,并说明需要几个时钟周期。(1)将imm16加到寄存器R1中,即R[R1]←R[R1]+imm16(2)将存储单元imm16中的内容加到寄存器R1中,此时,imm16为直接地址。即R[R1] ←R[R1]+M[imm16]。

答:图中所示的数据通路中,所有与内部总线相连的寄存器都有相应的Rin和/或Rout控制信号,以控制总线和寄存器之间的数据传送。总线和ALU输入端之间、Y寄存器与ALU输人端之间都无须控制信号。ALU输出与Z寄存器之间可以有控制信号Zin,也可以没有,此时,每来一个时钟,ALU的输出总是被写入Z寄存器。以下说明中,为了明显表示ALU输出送Z寄存器,假定有控制信号Zin。

(1)指令功能为R[R1]←R[R1]+imm16时,执行阶段不需要访存操作,因此,可用3个时钟周期完成,分别包含以下各控制信号:

MDRout,Yin

R1out,add,Zin

Zout,R1in

(2)指令功能为R[R1]←R[R1]+M[imm16]时,执行阶段需要一次访存操作,因此,至少需要以下5个时钟周期。其中R1、Y这两个控制信号可以在Read1周期就送出,并在Read2周期中保持不变,也可以到Read2周期时再送出。MDRout,MARin

Read1,(R1out,Yin)

Read2, R1out,Yin

MDRout,add,Zin

Zout,R1in