Verilog专题(四)组合逻辑中的for循环与generate-for

前言

对于verilog的学习,这里推荐一个比较好的实践网站HDLBits:https://hdlbits.01xz.net/wiki/Main_Page

本专题记录一些我觉得有价值的题目,希望通过这些题目可以对verilog更加熟练。

第四个专题主要讨论的问题是:for循环与generate-for。

1、Vector100 reverse

题目:Given a 100-bit input vector [99:0], reverse its bit ordering.

即把100位的输入从头到尾反转,对于这种重复性的工作,第一反应就是使用循环去实现。

(PS:在always块中,等号左边的信号一定要声明为reg型,若不如此声明,编译器会报错,但是HDLBits的编译器不会报错,这里我认为是个bug,请注意)

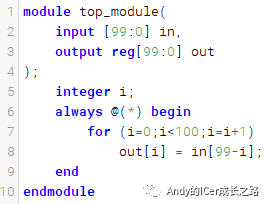

使用for循环的做法如下:

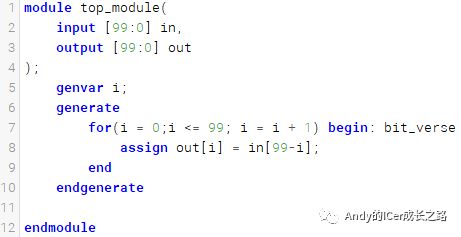

使用generate-for的做法如下:

2、Population count

题目:A "population count" circuit counts the number of '1's in an input vector.

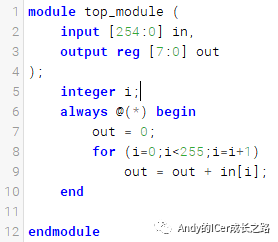

简单来说就是累加,也是一种重复性的工作,只能用for循环,做法如下:

3、Adder 100

题目:Create a 100-bit binary ripple-carry adder by instantiating 100 full adders.

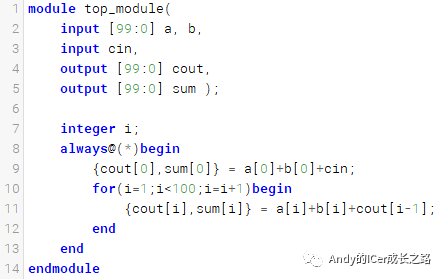

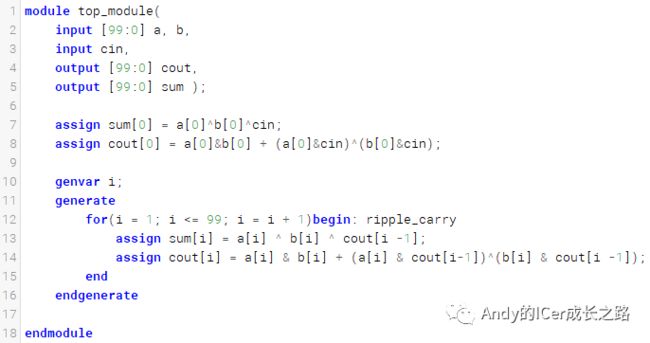

for循环做法如下:

使用generate-for的做法如下:

4、Bcdadder 100

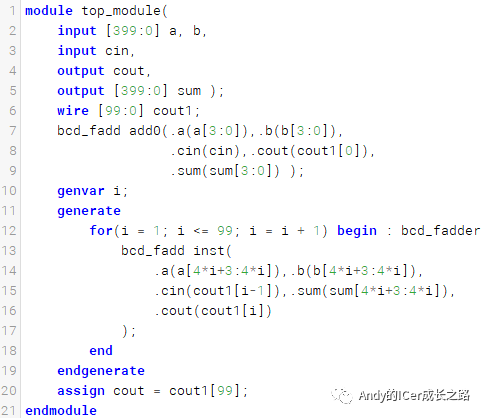

题目:You are provided with a BCD one-digit adder named bcd_fadd to create top_module.

只能使用generate-for,做法如下:

5、总结

1. 从上面的题目可以得出for和generate-for的区别:generate-for只针对于module、reg、assign、always、task等语句或者模块,而for只针对于非例化的循环,从第2和第4题更清晰地看出区别;

2.for和generate-for的优点:一般用作输入多次有一定规律的情况,以提高设计效率。

3.for和generate-for的缺点:浪费资源。在RTL级编码中极少使用for循环,这是因为for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,不能有效的复用硬件逻辑资源,造成巨大的浪费,一般常用case语句代替。

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验(后期打算与csdn同步更新),做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

![]()