Verilog专题(十二)Counter Design

HDLBits网址:https://hdlbits.01xz.net/wiki/Main_Page

1、十进制计数器(decade counter)

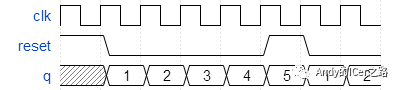

题目:Build a decade counter that counts from 0 through 9, inclusive, with a period of 10. The reset input is synchronous, and should reset the counter to 0.

我的设计:

注意的点:同步复位、1为下限、10为上限。

module top_module (input clk,input reset,output [3:0] q);always@(posedge clk)beginif(reset | q == 4'd10)q <= 1;elseq <= q + 1;endendmodule

2、十二进制计数器

题目:Design a 1-12 counter with the following inputs and outputs:

-

Reset Synchronous active-high reset that forces the counter to 1

-

Enable Set high for the counter to run

-

Clk Positive edge-triggered clock input

-

Q[3:0] The output of the counter

-

c_enable, c_load, c_d[3:0] Control signals going to the provided 4-bit counter, so correct operation can be verified.

You have the following components available:

-

the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

-

logic gates

module count4( input clk, input enable, input load, input [3:0] d, output reg [3:0] Q );

The c_enable, c_load, and c_d outputs are the signals that go to the internal counter's enable, load, and d inputs, respectively. Their purpose is to allow these signals to be checked for correctness.

我的设计:

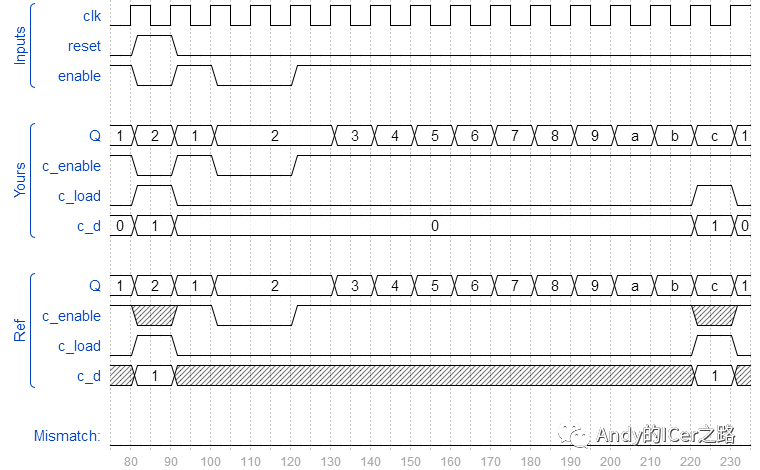

这个计数器的功能是实现从1到12的计数,因此,如果复位reset有效,则计数复位为1,我们需要做的不是自己设计一个计数器,而是需要例化题目给的一个计数器,题目给的计数器需要有一个输入信号为load信号,当计数到12的时候产生一个load信号和一个enable信号,设计如下

module top_module (input clk,input reset,input enable,output [3:0] Q,output c_enable,output c_load,output [3:0] c_d); //always@(*)beginif(reset) beginc_load=1;c_d=1;endelse beginc_load=0;c_d=0;if(Q==4'd12 & enable==1)beginc_load=1;c_d=1;endendendassign c_enable =enable;count4 the_counter (clk, c_enable, c_load, c_d, Q);endmodule

仿真波形

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

![]()