Verilog专题(三十四)两输入的Mealy状态机

HDLBits网址:https://hdlbits.01xz.net/wiki/Main_Page

题目

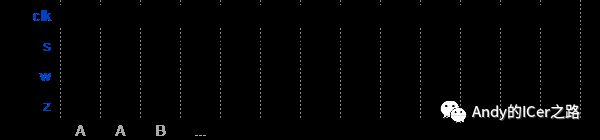

考虑输入为s和w的有限状态机,假定FSM以称为A的复位状态开始。只要s = 0,FSM就会保持状态A,而当s = 1时,FSM会进入状态B。一旦进入状态B,FSM就会在接下来的三个时钟周期中检查输入w的值,如果恰好在这些时钟周期中的两个时钟周期中w = 1,则FSM必须在下一个时钟周期中将输出z设置为1,否则z必须为0。FSM在接下来的三个时钟周期中继续检查w,依此类推。下面的时序图说明了不同w值所需的z值。

使用尽可能少的状态,请注意,s输入仅在状态A中使用,因此只需要考虑w输入。

Module Declaration

module top_module (

input clk,

input aresetn, // Asynchronous active-low reset

input x,

output z );

我的设计

根据状态机转移图和题目描述,代码如下:

module top_module (input clk,input reset, // Synchronous resetinput s,input w,output z);parameter A = 1'b0, B = 1'b1;reg current_state;reg next_state;always@(posedge clk)beginif(reset)begincurrent_state <= A;endelse begincurrent_state <= next_state;endendalways@(*)begincase(current_state)A:beginnext_state = s ? B : A;endB:beginnext_state = B;endendcaseendreg w_reg1;reg w_reg2;always@(posedge clk)beginif(reset)beginw_reg1 <= 1'b0;w_reg2 <= 1'b0;endelse if(next_state == B)beginw_reg1 <= w;w_reg2 <= w_reg1;endelse beginw_reg1 <= 1'b0;w_reg2 <= 1'b0;endendalways@(posedge clk)beginif(reset)beginz <= 1'b0;endelse if(next_state == B && counter == 2'd0)beginif(~w & w_reg1 & w_reg2 | w & ~w_reg1 & w_reg2 | w & w_reg1 & ~w_reg2)beginz <= 1'b1;endelse beginz <= 1'b0;endendelse beginz <= 1'b0;endendreg [1:0] counter;always@(posedge clk)beginif(reset)begincounter <= 2'd0;endelse if(counter == 2'd2)begincounter <= 2'd0;endelse if(next_state == B)begincounter <= counter + 1'b1;endendendmodule

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

![]()