IIC协议总线——总结

IIC采用主从(Master-Slave)通信,适用于短距离,中低速设备通信,每次都是主机发起通信,和结束通信;从机不能主动发起通信。

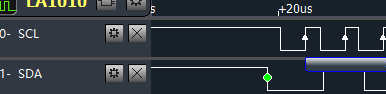

空闲时:SDA和SCL保持为高,此时从机要完全释放总线。这个阶段SDA控制权在主机

总线空闲状态时,通信开始时的start信号产生:SDA由高变低。这个阶段SDA控制权在主机

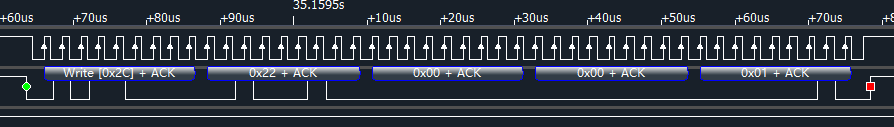

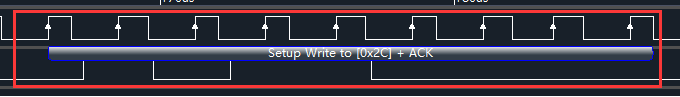

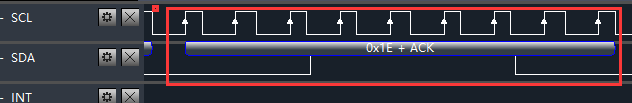

地址发送:在上阶段的基础上,接下来主机发送clk信号,主机也会在clk翻转过程中,将7bit 的IIC地址和控制位由高到低从SDA管脚发送,发送时。SDA在SCL为高电平时保持稳定,在SCL为低时变化。这个阶段SDA控制权在主机

数据发送和接收:根据IIC协议,当通信一旦建立,主机就可以进行读或写,以下假设要读写n(n > 1)个字节的第一个字节,分别介绍:

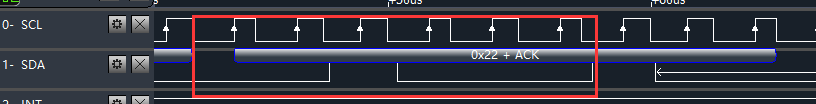

(1)主机放送数据:在上个阶段基础上,从机如果检测到IIC地址与之匹配,就会与主机建立通信,主机按照上一步规则发送8个bit数据,与此同时,从机接收8bt数据,由从机回ACK信号(在第9个clk时,拉低SDA,使SDA为低)。这个阶段前8个clk,SDA控制权在主机,第9个clk控制权在从机

(2)主机接收数据:从机按照规则发送8个bit数据,与此同时,主机接收8bt数据,由主机回ACK信号(在第9个clk时,拉低SDA,使SDA为低)。这个阶段前8个clk,SDA控制权在从机,第9个clk控制权在主机

通信结束时,stop信号的产生:SCL保持为高,SDA由低变高。这个阶段SDA控制权在主机

随后IIC总线进入空闲状态。

1. ACK/NAK信号到底是谁产生?

答:由数据的接收方产生,不管主机和从机,都可以产生ACK/NAK信号。

2.NAK信号什么情况下产生?

答:地址不匹配;数据出错;最后一个字节传输完成,之后没有数据时;异常情况。

3.SCL占空比有何影响?

答:主要体现在数据的保持时间和建立时间的影响,中低速情况影响不大,当高速通信时,例如大于350K,留意IIC的建立和保持时间。

4.IIC总线速度怎么理解?

答:IIC总线速度有50K/100K/200K/250K/300K/400K/500K等规格,SCL每个周期可以发送1个bit,所以,如果SCL频率200KHz,可以理解成200Kbit/s,另外,速度快慢主要看主机如何配置。

5. IIC第一个或前几个字节数据异常,怎么解决?

答:出现数据异常有很多情况。

例如,第一种,有可能软件IIC中断处理过多,耽误时间太长,数据还没放到buf就被总线采集。400K速度下,每个byte时间为9个clk,25us左右。如果软件处理需要>20us,就要检查软件中断处理;

第二种出错可能是没有将数据提前放到buf中。当主机启动读命令时,就要提前将数据放到buf中,每次发送中断需要将下次发送的数据提前放到buf,否则,就会出现第一个字节出错。

第三种:没有正确回应ACK/NAK信号;举个例子,有些场合下,主机来读2次数据,正常应该每次读完主机回应NAK,如果第一次读数据通信结束时,主机回应ACK,没有回NAK,从机就会以为主机还要读数据,所以拉住SDA总线,从机如果也没防范措施,就会持续拉死总线,那么,第2次读数据就会出错。

第四种:器件特殊要求,有些芯片例如24C02一类,写操作最后要延时,数据手册称这段时间write cycle time 一般为5ms~10ms.如果没有延时直接操作进行下次操作就会NAK.

6. IIC地址总是NAK?

答:第一种:地址出错,检查配置的IIC地址;第二种:硬件原因:电压不匹配,SDA与SCL短路断路,上拉电阻不对等等。

7.主机读数据有哪些?

答:标准IIC中,读数据有2种方式:start+addr+w+reg+stop,start_addr+r+data+stop以及start+addr+w+reg+restart +addr+r_data+stop。细看这两种情况,第一种启动2次通信读寄存器,第二种,只发起1次通信就完成读寄存器