Sparten6/Kintex-7 DDR3 IP仿真实例

目录

1、前言

1.1、关于数据、地址等接口位宽说明

1.2、DDR3读写时序理解

2、仿真实例

2.1、IP配置

2.2、仿真模型搭建

2.2.1、IPcore实例化

2.2.2、添加仿真模型

2.2.3、testbench测试激励

2.2.4、顶层top示例

2.2.5、testbench

2.2.6、CTRL模块

2.2.7、工程文件

3、总结

1、前言

一般使用do.sim.do文件,仅是为了方便分析、理解IP的使用访问时序。如何使用modelsim运行do.sim.do,这里就不做介绍。百度一下,很简单。如果仅是看do.sim.do的波形,你可能看不懂它在干什么。

为了更深入的理解IP的使用,最好是自己写testbench测试文件,搭仿真模型。

关于 DDR3 IP的配置过程,可以参考文献1/2;为了便于小白参考,综合考虑,本文提供完整的IP配置流程吧。

在IP配置过程中,需要注意一点,数据位宽、仿真模型型号、主钟,不可以随便选。否则可能会导致仿真模型不能正确响应你写的激励信号,或者出现IP一直初始化不成功等问题。

关于IP 的用户接口控制时序,可以参考文献3。在本文最后,提供完整的工程代码下载链接;若能提供些许帮助,还望读者五星好评一下。Thank you so much!

1.1、关于数据、地址等接口位宽说明

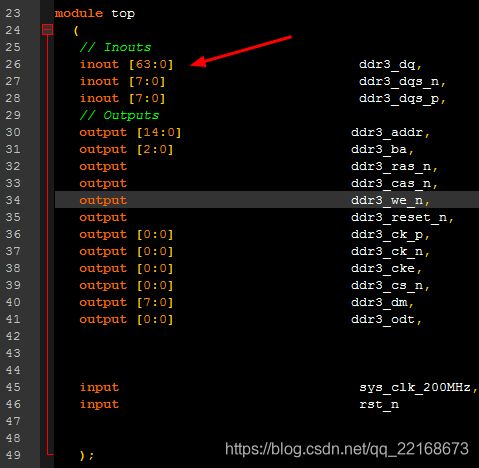

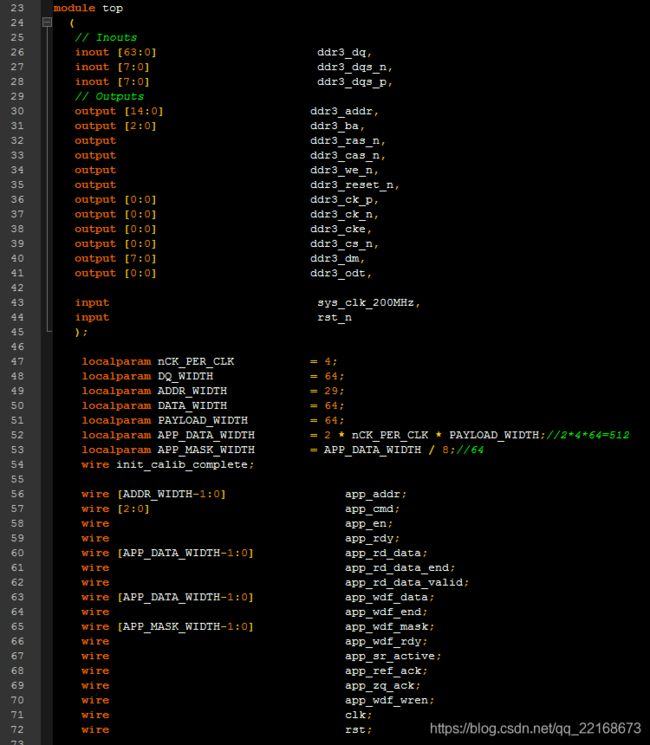

(1)在generate MIG IP的过程中,用户是可以自己选择芯片的数据位宽。如配置成64位,即DDR芯片的DQ数据总线位宽为64位,如下图顶层所示,inout、output端口是连接到DDR3 芯片上的管脚。

(2)用户接口数据位宽相关说明

用户地址app_addr[29-1:0]:位宽== RANK_WIDTH + BANK_WIDTH + ROW_WIDTH + COL_WIDTH;详细见IP生成的example_design_top文件。

用户数据app_rd_data[512-1:0]:下图中有计算公式:2*4*64=512。

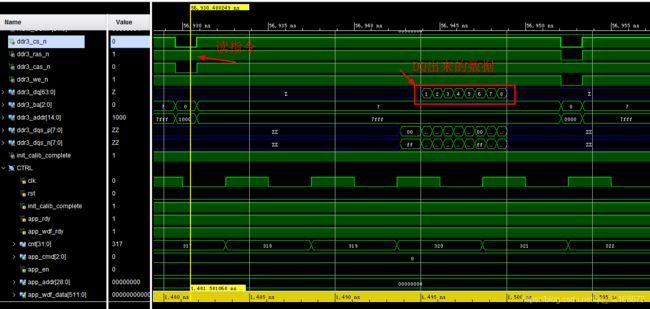

因为DDR的burst突发机制,突发长度为8,即每次给MIG发一个写指令app_cmd,MIG会自动从起始地址app_addr向DDR3芯片中连续写入8个数据。如app_addr起始地址是0,写数据是app_wdf_data = {64'd8,64'd7,64'd6,64'd5,64'd4,64'd3,64'd2,64'd1},

MIG则会在DDR3芯片地址0-7写入数据1-8.见下图。读机制也类似。

下图是写打印的报告。在下图中前四行似乎是在相同地址连续写了四次???注意前四行的开头,它们其实是我例化了四个DDR 仿真模型。因为仿真模型的数据位宽是16,MIG IP配置的DQ数据位宽是64,所以需要四个仿真模型进行拼接。

下图是读打印的报告

1.2、DDR3读写时序理解

在实际应该中,基本上不需要考虑DDR3芯片的接口控制逻辑。因为这部分逻辑都是由DDR3 MIG IP核自动管理的。

用户实际关系和控制的,是DDR3 MIG IP核的用户接口部分;即通过控制app_cmd等接口逻辑,即可实现对DDR3芯片的数据的正常读写访问。

不过,想深入理解数据是如何写入DDR3芯片的,可以看看这部分。

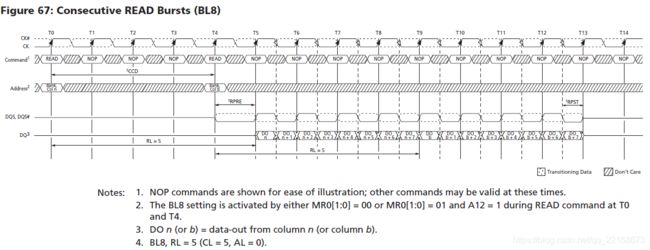

DDR3芯片型号MT41J256M16HA,芯片手册读写指令截图如下

理论写时序图

仿真写时序图,仿真时序图的写指令还是与手册一致,不过写地址似乎不太一样。至于原因,暂时不太清楚。不过,数据能够正确的写入、正确的读出。这一点看上面仿真模型给的打印报告可以确认。

仿真读时序

手册里的读时序

2、仿真实例

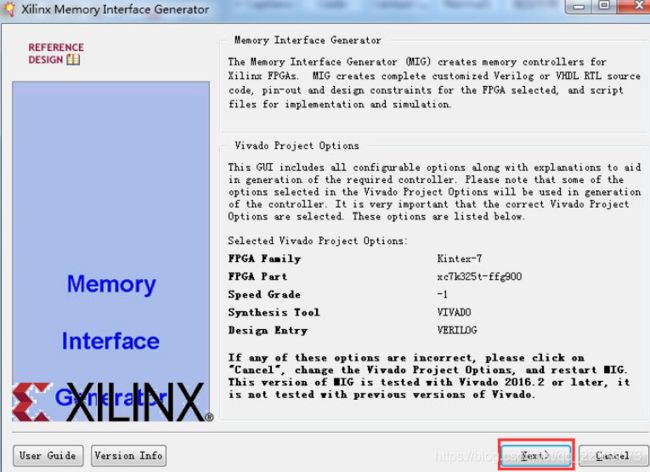

软件版本:vivado2017.4,

芯片型号:见下图

2.1、IP配置

下面有一些被我跳过了,按照默认即可。

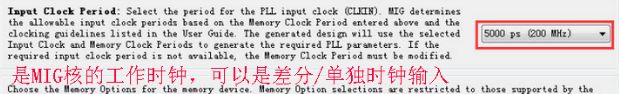

1、这里需要注意区分上图中Clock Period时钟是指DDR3芯片时钟,是FPGA输出给DDR3芯片的时钟;

2、Clock Period时钟的四分频(4:1),是用户时钟,800MHZ的四分频是100MHZ,即用户时钟是100MHZ.

3、DDR3芯片的数据位宽,上图配置的是64bit.

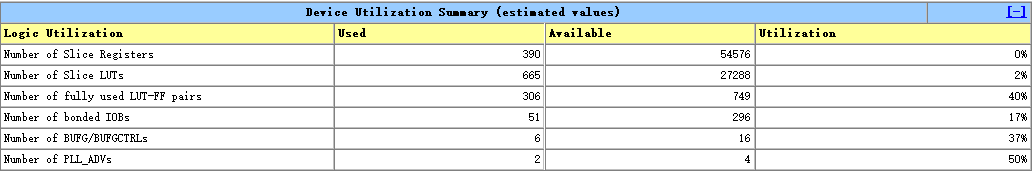

MIG是FPGA的硬核资源。若该FPGA芯片中共有6个PLL,在没例化MIG时,这六个PLL都可以被用户例化使用;但若例化了MIG,则用户只能使用剩下的5个PLL资源。如下图所示,在下面的工程中我仅例化了一个PLL和一个DDR3 MIG核,在综合之后显示PLL使用量是“2”,从而验证了上述推论。

关于上面DDR3芯片的驱动时钟频率,与用户时钟频率之间的关系,进一步补充解释如下图所示:

关于DDR3芯片的数据位宽与MIG核的用户数据位宽之间的关系如下:

因为这里时钟比率选了4:1,DDR3芯片的数据宽度是64bit,并且还是上下沿都能打数据,那么用户数据接口宽度就是64X4X2=512bit。

这里X4是4:1造成的,X2是因为DDR接口上下沿都能打数据,而用户接口不可以这么干,只能老老实实的上沿打数据。

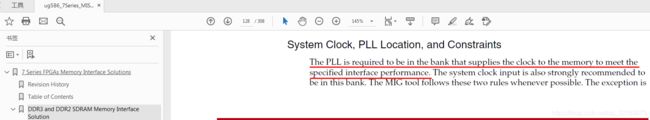

关于系统时钟:上图Input Clock Period是指MIG核的工作时钟(也即系统时钟sys_clk),由于MIG核访问DDR3芯片是采用时钟双沿进行数据传送的,所以在调用MIG核的同时,MIG核会默认占用FPGA芯片的一个PLL IP资源,用于产生DDR3芯片的驱动时钟、MIG核的用户时钟。所以,在介绍Input Clock Period时是将其介绍为PLL input clock(CLKIN),该时钟也就可以理解是MIG核的工作时钟,这个工作时钟需要进一步配置为是单端/差分,如下图所示:

关于参考时钟,因为倍频之后的时钟质量下降,所以还要用没倍频时钟来作为系统运行的基准,计算系统延迟啥的。独立参考时钟或许不接也没问题,这个我没试过。

补充介绍系统时钟sys_clk和参考时钟ref_clk,如下图所示。

2.2、仿真模型搭建

工程目录如下,用户逻辑和IP core都在.srcs文件夹里。

点击去,找到 ip -> ddr3_mig,example_design文件夹。

example_design文件夹有官方提供的一个设计实例,有DDR3 芯片的仿真模型和sim.do文件。

example_design文件夹里rtl文件夹,是Verilog代码,里面还有example_top,含有DDR3 IP core的实例化。

example_design文件夹里sim文件夹,放有DDR3芯片的仿真模型,sim.do文件。

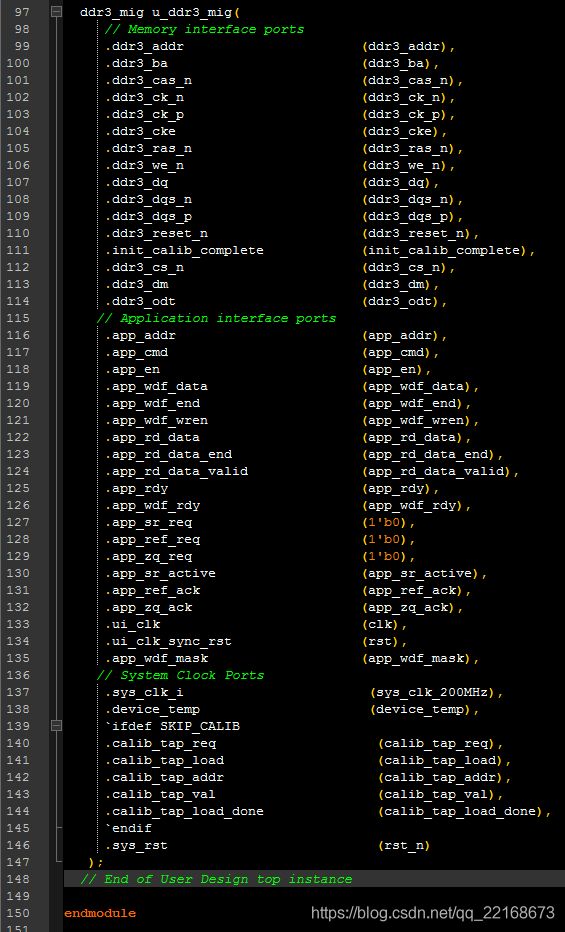

2.2.1、IPcore实例化

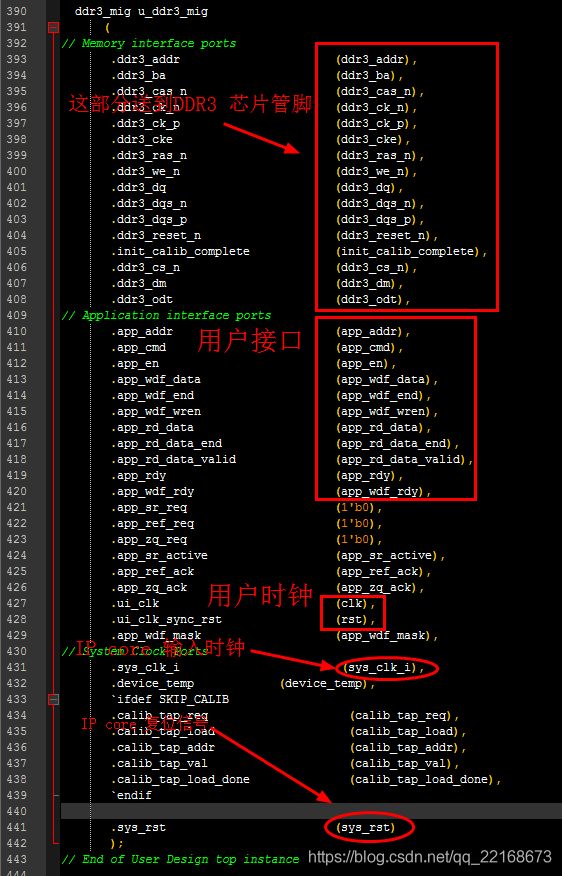

在example_design--- rtl 文件夹里找到example_top文件,将里面的下面几行代码粘贴复制到你工程的顶层,即完成了对DDR3 IP core的实例化。

(1)clk、rst是DDR3 MIG IP核提供的用户时钟和用户复位信号,高电平复位。

(2)关于系统时钟:sys_clk_i,是FPGA给DDR3 MIG IP core提供的输入时钟(配置MIG IP时配置sys clk nobuffer);若将sys clk配置为差分的,则sys_clk_i会变为sys_clk_p/sys_clk_n。

(3)关于参考时钟:由于在配置MIG核时选择用系统时钟作为参考时钟,所在这里没有ref_clk_i,若是差分参考时钟则是ref_clk_p/ref_clk_n

(4)sys_rst,是DDR3 MIG IP core的复位输入信号。

2.2.2、添加仿真模型

ddr3_model是仿真模型,需要添加到工程仿真文件里;

ddr3_model_parameters,是参数配置,相当于头文件一类的参数,需要添加到工程仿真文件里;

sim_tb_top是官方提供的testbench顶层,里面含有对仿真模型的例化实例,现在打开该文件。

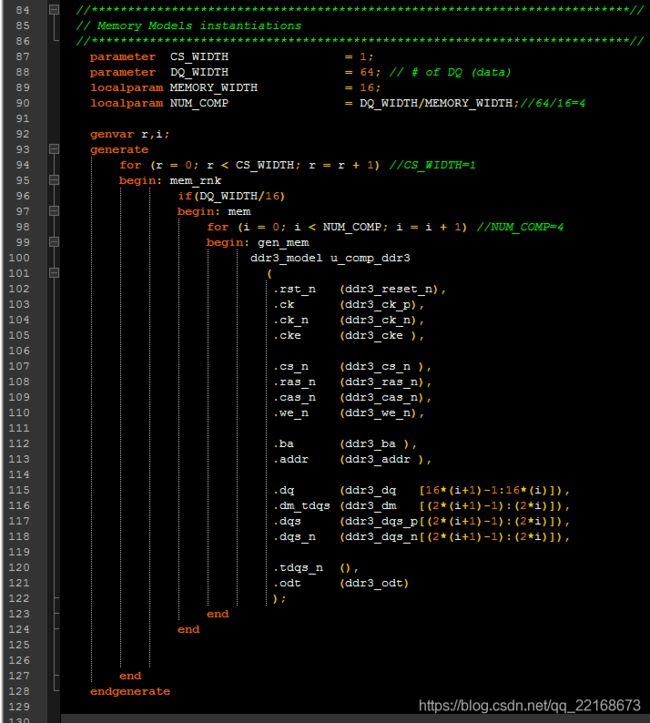

下图就是在sim_tb_top中关于仿真模型的代码。

将下面几行代码粘贴复制到你自己设计的testbench中。

需要注意的是:

(1)下面有一些参数是需要从sim_tb_top前面的一些parameter等参数里去找。最好将那几个参数粘贴复制过去。

(2)下面的信号连线也是需要需该的,修改为top的那些端口,连接到一起就行了。

(3)还是不知道该怎么操作???好吧,下面提供关于仿真模型的搭建代码!

下面generate了4片仿真模型。为啥是4片?还不知道为啥????

再说一遍吧,因为仿真模型的数据位宽是16,DDR3 MIG IP配置的数据位宽是64。所以是4个仿真模型。

2.2.3、testbench测试激励

激励这里我仅是提供了DDR3的时钟输入和复位输入信号。读写控制都放在顶层的CTRL模块里。

如果能实现读写一个burst,则基本就会使用DDR3了。

至于是否要进行板级测试,有条件的可以进行。每有板子的,做仿真跟板卡测试的效果是一样的。

因此,小白们不用担心自己是否有DDR3的板子!

2.2.4、顶层top示例

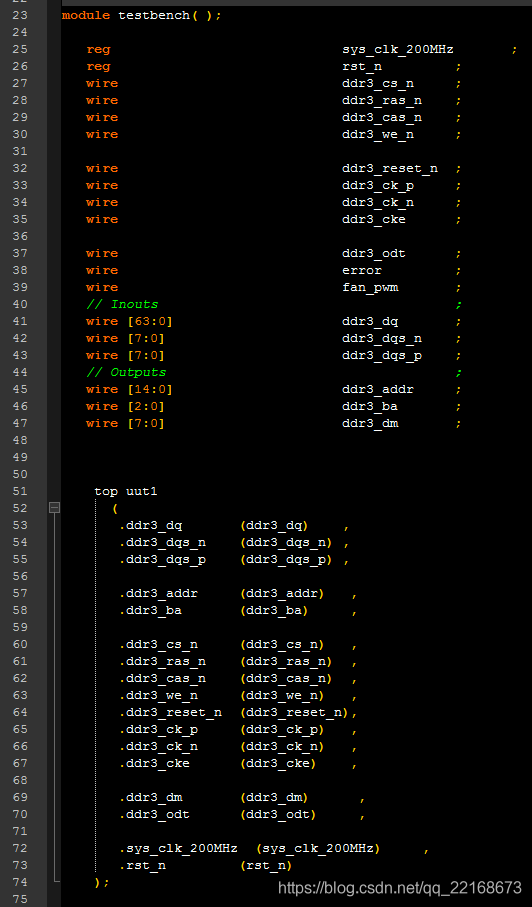

2.2.5、testbench

2.2.6、CTRL模块

至于这个模块的设计呐,就交给天赋异禀的你了!

因为你必须理解自己想放DDR3里写入什么数据,然后回读回来,才能表明你理解并会用DDR3 MIG IP core了。

按照前一篇博客的时序设计就好。能够实现简单的读写测试即可。

好吧,我还是把前面的时序粘贴在这里吧

写控制时序:

读控制时序:

2.2.7、工程文件

上面都整理完后,工程文件应该是这几个。

3、总结

在配置MIG IP核时,需要注意区分核掌握概念:

小结一:DDR3芯片驱动时钟与用户时钟之间的关系;

小结二:DDR3芯片的数据位宽与MIG核用户数据位宽之间的关系;

小结三:理解MIG核的系统时钟sys_clk(即PLL的输入时钟,这个PLL是MIG核自动占用的一个PLL资源)与参考时钟的概念。

小结四:掌握MIG核用户读写访问指令与时序;

小结五:建立工程,搭建仿真环境,对MIG核进行读写访问。

如果你在仿真波形里,顺利的向DDR3 MIG IP core 发了一个写命令,并顺利的回读出来该数据,则恭喜你,基本掌握DDR3的使用方法。

补充:

ISE中Kintex-7 DDR3 IP core的仿真与vivado应该差不多,再次提醒,不要随便乱选仿真模型、数据位宽、主钟等一类的东西,否则可能会导致仿真模型工作不正常。

至于Sparten6 DDR3 IP core的仿真,可以参考我的上一片博客的架构。

最后,附上上述工程的全部代码。看在本人辛苦整理的份上,希望大家给贡献点下载积分!非常感谢!

下载链接: https://download.csdn.net/download/qq_22168673/11171084

>>点击这里返回导航页<<

参考文献:

【1】https://blog.csdn.net/zhyl558/article/details/82018271#

【2】https://blog.csdn.net/fzhykx/article/details/79642327

【3】https://blog.csdn.net/qq_22168673/article/details/89743195