总线,接口详解

一、什么是总线?什么是接口?

总线和接口都有相互连接的含义。接口:两个部件连接。总线:多个部件连接。

接口与总线有时也不加区分,合称为总线接口或接口总线等。

部件:CPU,内存,显卡,硬盘, KVM。

总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束;

接口包括:PCI总线接口、USB串行接口、RS232串行接口、打印机并行接口(老式主板上有)等;

USB接口电路:由USB接口底座、电感、滤波电容、电阻排、保险电阻和南桥芯片(USB控制器)等组成。

部件通过接口和总线连接完成通信。

二、总线组成

总线由总线控制器,接口和传输线组成;

总线控制器:由于总线的共享性,所以需要一个总线控制器来控制总线的使用和分配;

接口:由三态门和缓冲寄存器组成。三态门可以决定当前总线与这个部件的联通状态,三态门的输出可以是1、0和高阻抗三个状态;

传输线:除了传输数据、地址和控制信号的信息线外,还有电源线和接地线来连接到每个部件;

按功能分为控制线,地址线和数据线;

参考:https://blog.csdn.net/stringNewName/article/details/51451955

参考:https://www.cnblogs.com/onlyforcloud/articles/4444321.html 计算机原理学习(2)-- 存储器和I/O设备和总线

参考:https://wenku.baidu.com/view/e78eef22aeaad1f347933f2c.html 计算机总线

参考:http://baijiahao.baidu.com/s?id=1601905877566591798&wfr=spider&for=pc 主板怎么选?看完秒懂

举例:

主板芯片组一般由北桥(North Bridge)芯片和南桥(South Bridge)芯片组成。它们都是总线控制器。

北桥芯片是处理器和高速设备之间的联系纽带,如内存、PCI-E等设备的总线就构建于北桥之上。

南桥芯片负责相对低速的系统设备的连接,如I/O设备、IDE、SATA、USB 2.0、32Bit的普通PCI插槽等,同时现代的南桥芯片还集成了诸如AC'97声卡控制器、网络控制器等常用而又要求不高的设备。

北桥和南桥之间则通过高速的总线连接起来,如Intel的Hub Link技术、VIA的V-Link技术、SIS的Multi-Threaded“妙渠”技术、都是为方便两者间大数据量的传输而开发的高速总线。

参考:https://baike.baidu.com/item/%E6%8E%A5%E5%8F%A3%E6%80%BB%E7%BA%BF/12724095

三、总线的分类?

按照CPU内外来分类:

- 内部总线:在CPU内部,ALU/CU和Cache(Cache控制器)之间传输数据所用的总线称为片内总线。

- 外部总线:CPU与内存/PCIE显卡/PCH之间进行通讯的通路,也称系统总线。通常所说的总线指片外部总线。

- I/O总线:第一层I/0总线和第二层I/O总线。

参考:http://www.360doc.com/content/18/0801/17/16534268_774955702.shtml 主板芯片详细介绍

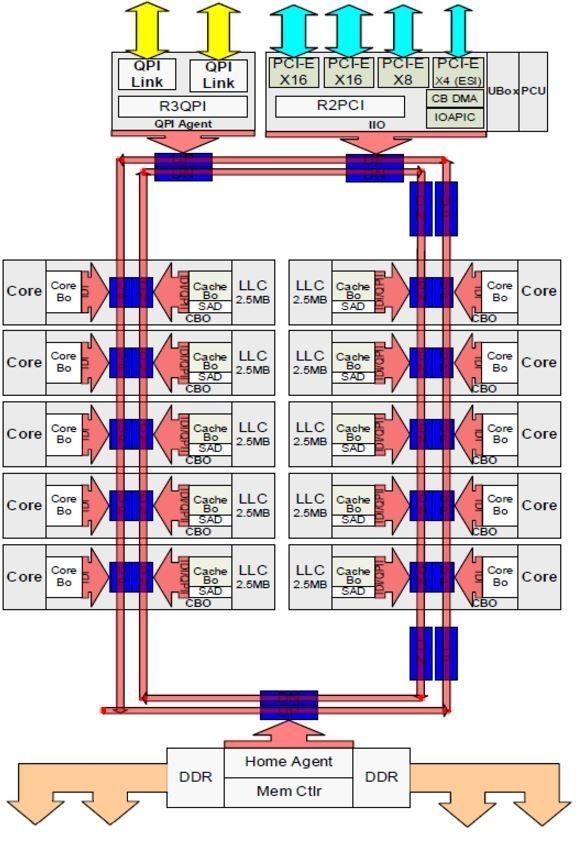

1. 环形总线(片内)

内核,LLC(三级缓存LastLevelCache)通过总线控制器与其他内核,内存控制器等总线控制器通信。

CPU环形总线倍频:也是CPU缓存频率,CPU Cache Ratio。

参考:http://www.sohu.com/a/224211922_641165 小科普 | BIOS设置选项详细解释①——CPU核心篇

Cache(数据Cache)及其地址变换逻辑(也叫Cache控制器)

https://blog.csdn.net/Kiloveyousmile/article/details/74331592 Cache控制器的设计

2.1 QPI/UPI总线(外部总线)

QPI总线实现芯片之间的直接互联;

QPI采用了与PCI-E类似的串行式点对点设计(基于包传输);

一组QPI具有具有20条数据传输线,每一条通路可传送20bit数据。有16bit是真实有效的数据,其余四位用于循环冗余校验;

QPI是双向的,在发送的同时也可以接收另一端传输来的数据;

QPI总线总带宽=QPI传输速率(GT/s)×每次传输的有效数据(即16bit/8=2Byte)×双向。

QPI总线总带宽=4.8GT/s×2Byte×2=19.2GB/s,QPI总线总带宽=6.4GT/s×2Byte×2=25.6GB/s。

https://wenku.baidu.com/view/41b249e9aeaad1f346933f6d.html FSB总线与HT总线与QPI总线的区别

Intel于2017年发布的Skylake-SP 至强中,用UPI取代QPI。UPI@ 10.4GT/s

2.2 内存总线(外部总线)

CPU和内存的之间的连接,CPU集成的内存控制器负责通过内存总线和内存模组(DDR1/2/3/4)通讯,例如寻址、读写等。

http://tieba.baidu.com/p/4650289532 为什么电脑所有总线都串行了,只有内存是并行的

2.3 PCI-E总线(外部总线)

PCI-E总线是全双工点对点串行连接,(与PCI总线共享并行架构相比)

与基于半双工共享并行架构而制定的PCI以及AGP规范不同,PCI-E规范是基于全双工点对点串行架构制定的,而且还支持热拔插,其中全双工代表每个PCI-E通道在同一周期内可以实现数据的双向传输;点对点意味着每个PCI-E设备都是独立连接,不需要向整个总线请求带宽;串行传输则可以让其信号速率轻松达到GT/s(相当于GHz)的级别。

点对点意味着每一个PCI Express设备都拥有自己独立的数据连接(通道),各个通道之间并发的数据传输互不影响,

PCI-E 3.0 传输速率8GT/S,单通道单向带宽=8GT/s x 128/130 ÷ 8 =0.98GB/s≈1GB/S(GT/S描述物理层通信协议的速率);

显卡接口(显卡控制器):占用PCI-E 3.0 X16

参考:https://www.cnblogs.com/shaobojiao/p/7885553.html

2.4 DMI接口(PCH)(外部总线)

CPU集成内存控制器及PCI-E控制器,直接和内存及显卡进行数据传输,DMI连接南桥整合了所有的I/O功能。

DMI采用点对点连接,DMI 3.0,占用PCI-E 3.0 x4

参考:https://wenku.baidu.com/view/3c9c5f190a4e767f5acfa1c7aa00b52acfc79cb0.html PCH简单介绍

参考:https://wenku.baidu.com/view/fe7cb313f11dc281e53a580216fc700abb6852b6.html 认识主板及PCH

3. I/O总线

3.1 USB总线(第一层I/O总线)

USB 3.0 线缆具有8个主要的传导体(conductors):3个双绞信号对用于USB数据通路,以及一对用于电源。

四线差分信号,与USB2.0两线非超高速信号分离;每条数据线的时钟频率是2.5Ghz,单向带宽:5Gbps;

USB 3.0对Wifi 2.4GHz有干扰;

参考:https://www.cnblogs.com/coryxie/p/3956220.html USB 3.0体系结构概览

3.2 SPI总线(第一层I/O总线)

Serial Peripheral Interface串行外设接口。南桥与外设以串行方式通信。在Intel架构中放BIOS/UEFI固件的Flash可以通过SPI总线和南桥连接

3.3 LPC总线(第一层I/O总线)

LPC(Low Pin Count, 少引脚数),连接Super I/O等接口,连接legacy I/O controller控制

3.3.1 LPT接口(第二层I/O)

并口,打印终端(line print terminal)接口

3.3.2 RS-232接口(第二层I/O)

串口

3.3.3 PS/2接口(第二层I/O)

在开发MCU应用系统时,如果单颗MCU无法满足系统的要求,一个很普遍的做法就是使用两颗或更多的MCU,把一部分“杂项工作”分配给另一个有“助理”性质的低端MCU来完成。但是,采用两颗MCU,缺点也很明显,尤其是在芯片与PCB成本、系统可靠性及功耗方面都有先天的不足。此外,若采用了不同架构的MCU,还要面临需要不同的开发工具与开发人员的挑战。如果换一种思路,让MCU内部包含两个内核,其中一个用于主控,另一个用于协控,并且它们主控与协控在架构上能够向下兼容、高效通信,则在很多场合下都可以既保持多机系统的强大,又能避免多机系统的不足。

http://www.techbulo.com/2484.html

总线工作频率为33MHZ说的是一秒钟有33M个总线传输周期(不是时钟周期)

32位宽度指的是数据线有32条

一个传输周期传送32位数据,4字节

数据传输速度就是一秒钟4*33字节