CEVA DSP构成

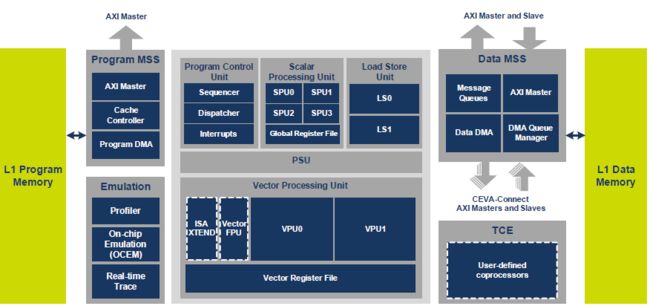

CEVA-XM4系统组成:

1,VP (vector processor) main DSP core

2,PMSS (program memory subsystem)

3,DMSS (data memory subsystem)

指令集架构:

1,VLIW : very long instruction word 并行

2,SIMD : single instruction multipe data 优化

物理构成:

1,SPU (scalar processing units) X4

2,LSU (load/store units) X2

256 bit/cycle each

3,PCU (program control unit ) X1

4,VPU (vector progress unit) X2

5,PSU (power scaling unit) X1

6,MSS (memory subsystem) X1

register file:

1,general register file(GRF)-->

SPUs, LSUs and PCU use

包含32个32bit registers 每个可以做成这些矢量类型:int、short、char、float

2,vector register file(VRF) 包含40个256bit的vector register

(1) general-purpose registers :V0-V39 (32 个) 每个可表示: vX.f8,vX.i8,vX.s16,vX.c32

(2)accumulators :V24-V39 (16个) 双reg组成512bit accumulator: i16=vW0.i8+vW1.i8, short32=vW0.s16+vW1.s16

V24-V31可复用

3,predicate register file(PRF)

(1)predicate register :scalar operations 15个 prX 大小:1byte

(2)vector predicate registers 7个 vprX 大小:32bit

4,address register file(ARF)

(1) astack pionter

(2) modulo registers

(3) step registers

5,system register file(SRF)