台积电技术研发实力

台积电技术研发实力

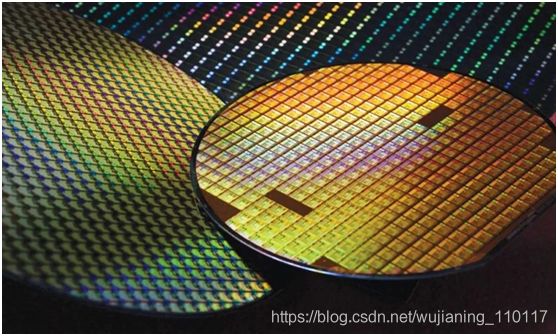

台积电在半导体行业的地位毋庸置疑。他们究竟有多强大,大部分读者了解得可能非常片面。从最新公布的2019年财报里,看看台积电的真正实力。

一、台积电在市场上的地位

根据公司财报,台积公司在先进制程技术、特殊制程技术,以及先进封装技术的发展上持续领先全球集成电路制造服务领域,2019年的市场占有率为52%。台积公司总体营收以地区划分(主要依据客户营运总部所在地),来自北美市场的营收占台积公司总体营收的60%、日本与中国大陆以外的亚太市场占9%、中国大陆市场占20%、欧洲、中东及非洲市场占6%、日本市场占5%。依据产品平台来区分,智能型手机占台积公司总体营收的49%、高效能运算占30%、物联网占8%、车用电子占4%。此外,消费性电子产品占5%、其他产品占4%。

单单在2019年,台积公司就以272种制程技术,为499个客户生产10761种不同产品。

二、台积电的工厂布局和员工数量;

台积公司及其子公司所拥有及管理的年产能超过一千二百万片十二吋晶圆约当量。台积公司在台湾设有三座十二吋超大晶圆厂(GIGAFAB®Facilities)、四座八吋晶圆厂和一座六吋晶圆厂,并拥有一家百分之百持有之海外子公司—台积电(南京)有限公司之十二吋晶圆厂及两家百分之百持有之海外子公司—WaferTech 美国子公司、台积电(中国)有限公司之八吋晶圆厂产能支援。

台积公司在北美、欧洲、日本、中国大陆,以及南韩等地均设有子公司或办事处,提供全球客户实时的业务与技术服务。至2019年年底,台积公司及其子公司员工总数超过51000人。

三.研发团队之组织与投资

2019年,台积公司持续投资研究与开发,全年研发总预算约占总营收之 8.5%,此一研发投资规模相当于或超越了许多其他高科技领导公司的规模。延续每二年半导体运算能力增加一倍之摩尔定律所面临的技术挑战日益困难,台积公司研发组织的努力着重于让台积公司能够提供客户率先上市且先进的技术和设计解决方案,帮助客户取得产品的成功。

2019年,随着 7 纳米强效版技术的量产,以及 5 纳米技术成功试产,公司的研发组织持续推动技术创新以维持业界的领导地位。当台积公司采用三维晶体管之第六代技术平台的 3 纳米技术持续全面开发时,公司已开始开发领先半导体业界的 2 纳米技术,同时针对 2 纳米以下的技术进行探索性研究。

除了发展互补金属氧化物半导体逻辑技术,台积公司广泛的对其他半导体技术进行研发,以提供客户行动系统单芯片(SoC)及其他应用所需的功能。

2019年完成的重点包括:

● 创新的晶圆级封装技术ー系统整合芯片 TSMC-SoIC®ー的制程认证;

● 大量生产第四代整合型扇出层叠封装技术(InFOPoP)以支援行动处理器封装;

● 成功验证第五代整合型扇出层叠先进封装技术以支援行动应用,与第二代整合型扇出暨基板封装,以支援高效能运算(HPC)应用;

● 开发业界独特的 40 纳米 BCD(Bipolar-CMOSDMOS)技术,提供先进的 20-24 伏高压元件并与40 纳米超低功耗平台完全兼容,以及整合了可变电阻式存储器(RRAM),支援行动应用所需的低功耗、高整合度、以及小布局面积的高速通讯界面;

● 28 纳米嵌入式快闪存储器支援高效能行动运算与高效能低漏电制程平台,达成了车用电子及微控制器单元(MCU)的技术验证;

● 完成开发最新一代次微米像素传感器以支援行动应用,并开发嵌入式三维金属 - 介电质 - 金属(MiM)高密度电容,支援全域快门与高动态范围传感器之应用。

2019年,台积公司致力于维系与许多世界级研究机构的强力合作关系,包括美国的 SRC

及比利时的 IMEC。台积公司亦持续扩大与世界顶尖大学的研究合作,达到半导体技术进步及培育未来人才的二大目标。

四.2019年研究发展成果 研究发展组织卓越成果

● 5 纳米制程技术

虽然半导体产业逼近硅晶之物理极限,5 纳米制程仍遵循摩尔定律,显著地提高芯片密度,在相同的功耗下提供更好的效能,或在相同的效能下提供更低的功耗。2019年,台积公司持续进行 5 纳米制程之全面开发,专注于基础制程制定、良率提升、晶体管及导线效能善,以及可靠性评估。静态随机存取(SRAM)记忆体及逻辑电路之良率均符合预期,台积公司已达成2019年进入试产的目标。

●3 纳米制程技术

相较于 5 纳米制程技术,3 纳米制程技术大幅提升芯片密度及降低功耗并维持相同的芯片效能。2019年的研发着重于基础制程制定、良率提升、晶体管及导线效能改善以及可靠性评估。2020年,台积公司将持续进行 3 纳米制程技术的全面开发。

● 2 纳米制程技术

2019年,台积公司领先半导体产业进行 2 纳米制程技术的研发。

●微影技术

2019年微影技术研发的重点在于 5 纳米的技术转移、3 纳米技术的开发及 2 纳米以下技术开发的先期准备。5 纳米技术已经顺利地移转,研发单位与晶圆厂合作排除极紫外光微影量产问题。针对 3 纳米技术的开发,极紫外光(EUV)微影技术展现优异的光学能力,与符合预期的芯片良率。研发单位正致力于极紫外光技术,以减少曝光机光罩缺陷及制程堆栈误差,并降低整体成本。

2020年,台积公司在 2 纳米及更先进制程上将着重于改善极紫外光技术的质量与成本。

2019年,公司的极紫外光项目在光源功率及稳定度上有持续性的进展,光源功率的稳定与改善得以加快先进技术的学习速度与制程开发。此外,极紫外光光阻制程、光罩保护膜及相关的光罩基板也都展现显著的进步,极紫外光技术正逐步迈向全面生产制造就绪。

●光罩技术

光罩技术是先进微影技术中极为重要的一环。2019年,研发组织成功地完成 5 纳米制程光罩技术的转移,并在 3 纳米技术顺利导入更复杂且先进的极紫外光的光罩技术,生产良率、周期时间及基板缺陷亦有实质进展,以符合大量生产的要求。

●导线与封装技术整合

台积公司在导线互连间距密度和系统尺寸上持续升级晶圆级系统整合技术(WLSI),推动系统性能向前演进超越了摩尔定律。WLSI 利用前段三维(3D)整合,系统整合芯片(TSMC-SoIC®)和后段三维整合而开发出创新技术,包括整合型扇出(InFO)和 CoWoS® 技术。台积公司拥有最先进制程的晶圆/芯片,以及混合匹配的前段三维和后段三维系统整合,客户可以利用台积公司独特的从晶圆到封装的整合式服务来打造具差异化的产品。

●三维集成电路(3D IC)与系统整合芯片(TSMCSoIC®)

系统整合芯片(TSMC-SoIC®)是一种创新的晶圆级封装技术,将多个小芯片(Chiplet)整合成一个面积更小与轮廓更薄的系统单芯片,透过此项技术,7 纳米、5纳米甚至 3 纳米的先进系统单芯片能够与多阶层、多功能芯片整合,可实现高速、高频宽、低功耗、高间距密度、最小占用空间的异质三维集成电路。有别于传统的封装技术,TSMC-SoIC® 是以关键的铜到铜接合结构,搭配硅导孔(Through-Silicon-Via, TSV)以实现最先进的 3D IC 技术。目前台积公司已完成 TSMC-SoIC® 制程认证,开发出微米级接合间距(bonding

pitch)制程,并获得极高的电性良率与可靠度数据,展现了台积公司已准备就绪,具备为任何潜在客户用 TSMC-SoIC® 生产的能力。

简言之,TSMC-SoIC®技术不仅提供延续摩尔定律的机会,并且在系统单芯片效能上取得显著的突破。

●硅中介层(Si Interposer)与 CoWoS®

2019年,由于高效能运算(HPC)与人工智能(AI)市场的快速成长,CoWoS® 需求持续强劲,该产品类别的独特要求包括将具有最高运算能力的逻辑芯片与具有最大容量和频宽的存储器芯片整合在一起,而这正是 CoWoS® 的优势所在。为了满足持续增加的生产需求,先进后段晶圆厂 AP3 和 AP5 与最初的 CoWoS®晶圆厂 AP1 合力提供客户所需的 CoWoS® 产能。

在技术方面,第四代CoWoS® 藉由扩大硅中介层的尺寸而进一步提高封装整体性能,中介层面积高达 1,700 平方毫米,其大小足以容纳一个全光罩(full-reticle)尺寸的系统单芯片和多达六个三维(3D)高频宽存储器(HBM)的堆栈。正在开发的第五代 CoWoS® 的中介层面积高达 2,400 平方毫米,并同时考虑了新的芯片架构,例如小芯片、系统整合芯片、以及第三代高频宽记忆体(HBM3)。

●先进扇出与整合型扇出(InFO)封装技术

2019年,台积公司持续领先全球大量生产第四代整合型扇出层叠封装技术(InFO-PoP

Gen-4)以支援行动应用处理器与整合型扇出暨基板封装技术(InFO_oS)高效能运算(HPC)晶粒分割的应用。第五代InFO-PoP 和第二代 InFO_oS 也分别通过了认证,支援行动应用和高效能运算应用。根据第五代 InFO-PoP 认证,此技术可以具有更小的封装尺寸,更多的接脚数和更好的电源完整性(power integrity)。

第二代InFO_oS 提供了更多的晶粒分割整合于更大的封装尺寸和更高的频宽上。持续开发具有更细间距晶粒到晶粒互连的多晶粒异质整合成就了无基板的崭新整合型扇出技术,支援消费性应用。新世代整合式被动元件技术(Integrated Passive Device, IPD)提供高密度电容器和低有效串联电感(Effective Series Inductance, ESL)以增强电性,并已通过 InFO-PoP 认证。AI 与 5G 行动应用将受惠于强化的 InFO-PoP 技术,新世代 IPD 预计于2020开始进入大量生产。

●先进导线技术

为了强化客户的竞争力,台积公司透过导线技术架构的创新与新材料的开发,提供先进导线技术以提升芯片效能。创新的电力分布网络(PDN)方案在于减低传统作法上的高压降与电阻电容延迟,并利用更好的布线资源来改善线路密度。新材料包括金属与介电质材料,开发着重于结实的低介电材料与较低等效电容结构。

除了金属阻绝层的开发之外,台积公司亦研发单金属元素、双元与三元合金。先进技术研究晶体管结构及材料的创新持续提升先进逻辑技术的效能并降低功耗。台积公司在二维材料及纳米碳管晶体管的研究一直走在业界前端。

2019年,台积公司在超大型集成电路技术研讨会(Symposia on VLSI Technology, VLSI)发表了使用有区域选择的通道化学气相沉积技术成长在二氧化硅 / 硅基板上的 40 纳米通道长度上方闸极二硫化钨 p 通道场效晶体管的首次展示。没有使用二维材料层转移,此直接化学气相沉积技术更适合量产。

台积公司也在2019年举行的国际电子元件会议(International Electron Device Meeting, IEDM)成功率先展示使用后段制程兼容的低温低成本和高迁移率的后段制程纳米碳管晶体管在先进的 28 纳米硅逻辑电路上进行异质整合。台积公司持续寻找支援人工智能和高效能运算的新兴高密度、非挥发性存储器硬件加速器。台积公司的先进技术研究可望为持续密度微缩、提升效能、降低功耗铺路,提供先进逻辑技术以支援行动与高效能运算应用。

五、台积电的工艺多样性;

我们谈台积电的时候,很多时候会强调他们在先进工艺的实力,但这其实只是冰山一角。

首先看逻辑制程技术方面:

●5纳米鳍式场效电晶体制程(Fin Field-Effect

Transistor, FinFET)(N5)技术为台积公司推出的最新技术。此一领先全球的技术于2019已接获多个客户产品投片,包含行动通讯以及高效能运算产品,并预计于2020年上半年开始量产。

相较于7纳米FinFET(N7)技术,N5技术速度增快约15%,或者功耗降低约 30%。此外,N5技术自规划开始,便同时针对行动通讯与高效能运算应用提供优化的制程选项。

●5纳米FinFET强效版(N5P)技术为N5技术的效能强化版技术,并采用相同的设计准则。相较于 N7技术,N5P技术速度增快约20%,或功耗降低约40%。N5P技术的设计套件预计于2019年第二季进行下一阶段 N5 技术更新时推出。

●6纳米FinFET(N6)技术于2019年成功完成产品良率验证。由于N6技术采用极紫外光(ExtremeUltraviolet,

EUV)微影技术,能够减少光罩数量,因此,如果与N7技术生产相同产品相较,采用N6技术生产可以获得更高的良率,并缩短产品生产周期。此外,与N7技术相较,N6技术的逻辑晶体管密度提高约 18%,加上因光罩总数减少而获得较高良率,能够协助客户在一片晶圆上,获得更多可用的晶粒。

另外,N6技术的设计法则与N7技术兼容,亦可大幅缩短客户产品设计周期和上市的时间。N6技术于2020年第一季开始试产,并预计于2020年底前进入量产。

●N7技术是台积公司量产速度最快的技术之一,并同时针对行动运算应用及高效能操作数件提供优化的制程。总计截至2019年底共接获超过100个客户产品投片,涵盖相当广泛的应用,包含行动装置、游戏机、人工智能、中央处理器、图形处理器,以及网络连接装置等。此外,7纳米FinFET强效版(N7+)技术于2019年开始量产,协助客户产品大量进入市场。N7+技术是全球集成电路制造服务领域首个应用极紫外光于商业运转的技术。此一技术的成功,除了证明台积公司领先全球的EUV技术量产能力,也为6纳米和更先进技术奠定良好基础。

●12纳米FinFET精简型强效版(12nm FinFET Compact Plus, 12FFC+)技术与16纳米FinFET精简型强效版(16nm FinFET Compact Plus,16FFC+)技术系台积公司继16纳米FinFET强效版(16FF+) 技术、16纳米FinFET精简型(16nm FinFET Compact, 16FFC)技术及12纳米FinFET精简型(12nm FinFET Compact, 12FFC)技术之后,所推出的最新16/12纳米系列技术,拥有集成电路制造服务领域16/14纳米技术中最佳产品效能与功耗优势,并于2019年进入试产。

16FF+技术系针对高效能产品应用,包括行动装置、服务器、绘图芯片,及加密货币等产品。12FFC+、12FFC、16FFC+及16FFC则皆能支援客户主流及超低功耗(Ultra-LowPower, ULP)产品应用,包括中、低阶手机、消费性电子、数位电视、物联网等。总计目前

12FFC+、12FFC、16FFC+、16FFC、16FF+已接获超过 500个客户产品投片,其中绝大部分都是第一次投片即生产成功。

●22纳米超低漏电(Ultra-Low Leakage, ULL)(22ULL)技术于2019年进入量产,能够支援物联网及穿戴式装置相关产品应用。同时,此一技术的低操作电压(Low Operating Voltage, Low Vdd)技术也于2019年准备就绪。与40纳米超低功耗(Ultra-Low Power, ULP)(40ULP)及55纳米ULP制程相较,22ULL技术提供新的ULL元件、ULL静态随机存取记忆体(Static Random Access

Memory, SRAM),和低操作电压技术,能够大幅降低功耗。

●22纳米ULP(22ULP)技术发展系根基于台积公司领先业界的28纳米技术,并于2019开始量产。与28纳米高效能精简型强效版(28nm High Performance

Compact Plus, 28HPC+)技术相较,22ULP技术拥有芯片面积缩小10%,及效能提升10% 或功耗降低20%的优势,以满足影像处理器、数位电视、机上盒、智能型手机及消费性产品等多种应用。

●28HPC+技术截至2019年底,总计接获超过300个客户产品投片。28HPC+ 技术进一步提升主流智能型手机、数位电视、储存、音效处理及系统单芯片等产品应用的效能或降低其功耗。与28纳米高效能精简型(High Performance Compact)(28HPC)技术相较,28HPC+ 技术能够进一步提升效能约15%或降低漏电约50%。

●40ULP技术截至2019年底共接获超过100个客户产品投片。此技术支援多种物联网及穿戴式装置相关产品应用,包含无线网络连接产品、穿戴式应用处理器及微控制器(Micro Control Unit, MCU)(Sensor Hub) 等。此外, 台积公司采用领先的40ULP

Low Vdd技术,为物联网产品及穿戴式联网产品提供低功耗的解决方案。新的强化版类比元件顺利开发中,将进一步强化40ULP平台,支援客户未来更广泛的类比电路设计。

●55纳米ULP(55ULP)技术,截至2019年底共接获超过70个客户产品投片。相较于55纳米低功耗(55LP)技术,55ULP技术可大幅延长物联网相关产品的电池使用寿命。此外,55ULP亦整合了射频制程与嵌入式快闪存储器制程,能让客户的系统单芯片设计更为简单。

再看特殊制程技术方面;

●16FF+技术自2017年起已为客户生产汽车产业应用产品。16FFC技术基础硅智财(FoundationIP) 已 通 过 车 用 电 子 协 会(Automotive

Electronic Council, AEC)AEC-Q100 Grade-1验证,并且获得功能性安全标准ISO 26262 ASIL-B认证。

此外,也导入TSMC 9000A质量管理系统来规范车用硅智财,透过和第三方硅智财供应商合作来建立车用设计生态环境。台积公司持续开发更多7纳米车用基础硅智财,并于2020年第一季通过AEC-Q100 Grade-2验证。

●16FFC射频(Radio Frequency, RF)(16FFC RF)技术于2018年上半年领先业界为客户量产第五代行动通信技术(5G)RF 芯片。此一技术进一步支援新一代无线区域网络802.11ax(Wireless Local Area Network, WLAN 802.11ax)、 毫 米 波(MillimeterWave, mmWave),以及5G智能型手机等无线连接应用。台积公司不断精进16FFC RF技术,不但于2019年领先全球推出首个截止频率(Cut-offFrequency, fT)超过300吉赫兹(GHz) 的

FinFET元件,亦领先全球完成震荡频率(Maximum Clock Frequency, fmax)超过400GHz的最佳FinFET元件的开发。此一高性能且更具成本效益的技术也将被采用来满足更多的应用,例如雷达、扩增实境/虚拟实境等,以降低芯片功耗及芯片尺寸并支援SoC设计。

●22ULL RF技术除了支援磁性随机存取存储器(Magnetic Random Access Memory, MRAM)、可变电阻式存储器(Resistive Random Access Memory,RRAM),及高截止频率(Cut-off Frequency, fT)元件之外,于2019年新增支援无线区域网络功率放大器(Wireless LAN Power Amplifier)元件与极低漏电(Ultra-Low Leakage)元件,进一步支援5G 毫米波行动无线通讯和物联网应用的芯片开发。

●22ULL嵌入式电阻式随机存取存储器(ResistiveRandom Access Memory, RRAM) 技术,于

2019年开始试产,并预计于2020年完成硅智财(IP)可靠性认证。此一技术可支援各种不同应用,例如物联网微控制器(IoT MCU)及人工智能(Artificial Intelligence, AI)存储器元件等。

●22ULL嵌入式磁性随机存取存储器(Magnetic Random Access Memory, MRAM)技术硅智财预计于2020年度完成可靠性认证。此外,16纳米MRAM 技术也正在开发,且进展良好。MRAM

技术为包括AEC-Q100 Grade-1产品应用在内的高可靠性MCU产品的eFlash替代方案,提供了一个极具竞争力的转换途径。

●28HPC+ RF于2018年领先集成电路制造服务领域提供首个RF制程设计套件(Process Design Kit,PDK),支援110吉赫兹(GHz)毫米波和150℃车用规格等元件,以支援5G毫米波射频及车用雷达产品的设计。2019年,28HPC+RF技术新增支援极低漏电(Ultra-Low Leakage)元件及嵌入式快闪存储器(Embedded Flash)。客户5G毫米波射频及车用雷达产品皆已进入量产。

●28 纳米ULL嵌入式快闪存储器制程(eFlash)技术,已于2019年通过AEC-Q100 Grade-1可靠性认证。台积公司持续强化此一技术,并预计于2020年通过更严格的AEC-Q100 Grade-0要求。

●40ULP嵌入式快闪存储器制程(eFlash)技术截至2019年底,总计接获超过40个客户产品投片,其中包括微控制器(MCU)、无线通讯微控制器(Wireless MCU),和安全元件(Security Element)。此外,此一技术也提供低操作电压选择,为物联网设备和可穿戴连接设备提供低能耗的解决方案。

●40ULP嵌入式RRAM技术的IP于2019年完成可靠性认证。此一技术的设计套件和硅智财完全与互补式金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)逻辑制程兼容,其相关应用包括无线通讯微控制器(Wireless

MCU)、物联网装置,以及穿戴式装置。

●持续强化40ULP类比技术平台,包括降低噪声、改善匹配(Mismatch),及提供低漏电元件等。完整的设计技术文件则预计于2020年完成。此一强化的40ULP类比技术平台与数位逻辑制程完全兼容,并可以同时支援高精确类比效能、低耗能的类比设计。

●十二吋0.13微米双载子-互补式金氧半导体-扩散金属氧化半导体强化版(Bipolar-CMOS-DMOS

Plus, BCD Plus)技术于2017年开始生产,晶圆出货于2018年及2019年皆显著成长。相较于前一世代0.13微米双载子 - 互补式金氧半导体-扩散金属氧化半导体强化版(Bipolar-CMOS-DMOS,

BCD)技术,此一新制程技术持续提供更优异的效能及功能强化,以满足高阶智能型手机的电源管理应用。

●0.18微米第三代BCD制程技术于2018年完成 AEC-Q100 Grade-1验证,并进一步于2019年完成 AEC-Q100 Grade-0 验证。相较于第二代BCD制程技术,此一制程技术提供更优异的成本竞争优势。

●持续强化电源硅基板氮化镓(Gallium Nitride on

Silicon)技术,在650伏特和100伏特两种平台上,将氮化镓功率开关与驱动器整合,并持续改善硅基板氮化镓技术的可靠度,以支援客户高功率密度及高效率解决方案的芯片设计,满足多元的产品应用。650伏特和100伏特氮化镓集成电路技术平台皆预计于2020年开发完成。

●硅基板有机发光二极体(Organic

light-emittingdiode on silicon, OLED-on-Silicon)面板技术与传统玻璃基板有机发光二极管面板技术相较,能够增加像素点密度5到10倍,以支援对高质量扩增实境(Augmented

Reality)/ 虚拟实境(Virtual Reality)眼镜日益增加的需求。台积公司与客户共同合作,成功同时在八吋及十二吋高压技术上展示此一技术的可行性,为扩增实境 / 虚拟实境供应商在工业、医疗,及消费电子多种产品应用的下一世代眼镜开发上,奠定精实的基础。

●有鉴于许多安防监控、汽车、家用,和行动通讯应用已迅速导入机器视觉(Machine Vision)技术,台积公司提供下一世代全区域曝光式(Global Shutter)互补式金氧半导体影像传感器(CMOS Image Sensor,CIS)与强化版近红外光CIS技术,使得机器视觉系统更安全、更小巧,及更省电。

●台积公司成功采用晶圆级封装(CSP)技术协助客户推出全球尺寸最小的互补金属氧化物半导体微机电(Micro-electromechanical

Systems)单芯片加速度计(Accelerometer),其尺寸可小于1平方厘米。此一尺寸小巧的优势,能够协助许多物联网与穿戴装置减少体积与重量。

先进封装技术也是台积电必不可少的一方面;

●针对先进行动装置的应用,成功开发能够整合7纳米系统单芯片和动态随机存取存储器(DRAM)的整合型扇出层叠封装技术(Integrated Fan-Out Packageon-Package, InFO-PoP),并于2019年协助数个客户产品大量进入市场。

●针对高效能运算的应用,能够在尺寸达二倍光罩大小的硅基板(Silicon Interposer)上异质整合多颗7纳米系统单芯片与第二代高频宽存储器(HighBandwidth Memory 2, HBM2)的CoWoS®技术,于2019年第三季成功通过验证。

● 除了CoWoS®技术之外,能够整合多颗7纳米单芯片的整合型扇出暨封装基板(InFO on Substrate, InFO_oS)技术于2019年开始量产。

●针对先进行动装置及高效能运算的应用,用于5纳米晶圆覆晶封装的细小间距阵列铜凸块(Cu

bump)技术已于2019年成功通过验证。

●针对物联网及高阶智能型手机产品应用,成功开发适用于物联网应用的16纳米制程的晶圆级封装(WaferLevel Chip Scale Packaging, WLCSP)技术,并于2019年协助客户产品大量进入市场。

六.特殊制程技术

台积公司提供多样化的新制程技术以协助客户广泛解决各类产品的应用:

●混合讯号/射频

2019年,台积公司成功开发以 5 纳米硅及电磁模拟为基础的 LC 振荡器设计解决方案,满足高速SerDes电路设计的需求,藉由不同金属层组合及特定布局来缩短设计周期。为了满足客户对于 5G 网络蓝图之高速、低延迟、以及大量物联网应用的需求成长,台积公司提供 16 纳米及 28 纳米射频元件,透过提升截止频率与最大震荡频率以支援射频收发器设计,以及 40 纳米特殊制程强化崩溃电压,在来自导通电阻与断电容的乘积降低的相同效益下,支援射频切换器设计的应用。

●电源 IC /双极—互补金属氧化半导体—双重扩散金属氧化半导体(BCD)

2019年,台积公司透过 40 纳米超低功耗平台开发出 20-24 伏高压元件的 40 纳米 BCD 技术,与低压元件和逻辑制程完全兼容,并首次成功整合可变电阻式存储器,在小布局面积提供低功耗、高整合度,支援行动应用装置的高速通讯界面,台积公司将持续开发 28 伏及 12-16 伏高压元件以涵盖更多的电源管理芯片应用。

●面板驱动

2019年,台积公司完成双平台先进高压显示驱动器 IC 技术。晶圆堆栈(WoW 28HPC / 40HV)和28HV 技术通过制程及可靠性认证,晶圆堆栈技术也已经完成了客户的产品良率和认证,相较于 40HV,其主动功耗降低 60%。

多家客户已完成

28HV 技术之早期IP 验证。这些技术是支援小尺寸面板 4K 分辨率、有机发光二极管(OLED)和 120Hz 显示驱动 IC 的先进技术。

此外,支援 AR/ VR 应用的硅基OLED 在80HV 技术上展现出优异的亮度均匀度。2020年,台积公司计划提升 28HV OLED 触控显示整合(TDDI)应用以及晶圆堆栈 8 伏晶体管的效能。

●微机电系统

2019年,台积公司完成模块化微机电系统(Modular MEMS)技术的验证,以大量生产高解析度加速度计与陀螺仪。未来计划包含开发下一世代高敏感度薄型麦克风、十二吋晶圆微机电光学影像稳定(Optical Image Stabilization, OIS)系统解决方案、以及生物微机电应用。

●氮化镓半导体

2019年,第一代 650 伏和 100 伏增强型高电子移动率晶体管(E-HEMT)投入生产,第二代 650 伏 和 100伏 E-HEMT 之质量因素(FOM)较第一代改善50%,并且通过工程验证。此外,台积公司完成100V D-HEMT 元件的开发,已通过工程验证,预计于2020年进入试产。

●互补式金属氧化物半导体(CMOS)影像传感器

2019年,台积公司在互补式金属氧化物半导体影像传感器技术获得数项进展。两项主要成果:完成开发最新一代微缩化次微米像素传感器,其像素尺寸较前一代减少 12.5%,并提高画素读取速度,降低读取杂讯,以支援行动应用;并成功开发三维金属 - 介电质 -金属(MiM)高密度电容,内嵌影像传感器阵列支援全域式快门与高动态范围传感器之应用。

●嵌入式快闪存储器/新兴存储器

2019年台积公司在嵌入式非挥发性存储器技术领域达成数项重要的里程碑。在 40 纳米制程方面,公司已成功量产分离闸(Split-Gate)反或闸式(NOR)技术,支援消费性电子产品的应用,例如物联网、智慧卡和微控制器单元(MCU),也支援各种车用电子产品的应用。在 28 纳米制程方面,公司的嵌入式快闪存储器开发支援高效能行动运算与高效能低漏电制程平台已完成

技术验证,以因应车用电子及微控制器的应用。台积公司并提供嵌入于非挥发性存储器之电阻存储器技术,作为低成本解决方案,支援对价格敏感的物联网市场。40纳米已完成技术验证,客户产品验证持续进行,28 纳米预计于2020年进入量产,22 纳米的开发符合进度,预计于2020年完成技术验证。台积公司也正在开发 22 纳米嵌入式磁阻式随机存取存储器,并已成功完成技术验证进入量产,此外,台积公司致力于 16纳米嵌入式磁阻式随机存取存储器的开发,以支援下一世代嵌入式存储器 MCU、车用电子元件、物联网、以及人工智能等多项新应用。

七.技术平台

台积公司提供客户具备完整设计基础架构的先进技术平台,以达成令人满意的生产力及生产周期,其中包括:电子设计自动化(EDA)设计流程、通过硅芯片验证的元件数据库及硅智财(IP)、以及模拟与验证用的设计套件,例如制程设计套件(PDK)及技术档案。

针对台积公司最先进的 5 纳米、6 纳米、7 纳米、7纳米强效版、12 纳米、22 纳米及 3D IC 技术设计实现平台,所需要的电子设计自动化工具、功能及硅智财解决方案都已经准备就绪来让客户采用以满足产品在不同设计阶段上的需求。

此外,台积公司扩展其硅智财质量管理项目(TSMC 9000),使得硅智财稽核得以在台积公司或其外部认证的实验室进行。为了能够结合台积公司开放创新平台生态系统的硅智财以协助客户规划新的产品设计定案,开放创新平台生态系统提供一个入口网站,连结客户至一个拥有 42 个解决方案提供者的生态系统。

总体而言,台积公司与硅智财伙伴们从0.35 微米到 5 纳米所累积的硅智财组合超过 2 万 6,000 个,满足了客户设计的需求。台积公司与电子设计自动化伙伴从0.13 微米到 5 纳米打造许多的电子设计自动化解决方案,成功地支援客户设计定案。

八、台积电的经营策略

台积公司深信,差异化的竞争优势将使台积公司更能把握未来集成电路制造服务领域的成长机会。因应智能型手机、高效能运算、物联网及车用电子四个快速成长的主要市场,及客户需求从以制程技术为中心转变为以产品应用为中心,台积公司已经分别建构四个对应的技术平台,提供客户最完备且最具竞争优势的逻辑制程技术、特殊制程技术、硅智财,以及封装测试技术,协助客户缩短芯片设计时程及加速产品上市速度。这四个技术平台分别为:

(1)智能型手机平台:

台积公司针对客户在顶级(Premium)产品的应用,提供领先的5纳米鳍式场效晶体管(5nm FinFET, N5)、6纳米鳍式场效晶体管(6nm FinFET, N6)、7 纳米鳍式场效晶体管强效版(7nm FinFET Plus, N7+),及 7 纳米鳍式场效晶体管(7nm FinFET,N7)等逻辑制程技术以及完备的硅智财,更进一步提升芯片效能、降低功耗及芯片尺寸大小。针对客户在主流产品的应用,则提供领先的 12纳米鳍式场效晶体管FinFET精简型(12nm FinFET Compact, 12FFC)、16纳米鳍式场效晶体管精简型(16nm FinFET Compact,16FFC)、28 纳米高效能精简型制程技术(28nmHigh Performance

Compact, 28HPC)、28纳米高效能精简型强效版制程技术(28nm High PerformanceCompact Plus, 28HPC+),和22纳米超低功耗(22nmUltra-Low Power, 22ULP)等不同逻辑制程选项以及完备的硅智财,满足客户对高效能、低功耗芯片产品的需求。

此外,不论顶级、高阶、中阶或低阶产品应用,也提供客户领先业界且最具竞争力的射频、嵌入式快闪存储器、新兴存储器、电源管理、传感器、显示芯片等特殊制程技术,以及包括领先产业的整合型扇出(InFO)的多种先进封装技术。

(2)高效能运算平台

台积公司提供领先的 N5、N6、N7,和12/16纳米鳍式场效晶体管等逻辑制程技术,以及包括高速互连技术等完备的硅智财,来满足客户对资料高速运算与传输的需求。台积公司也提供涵盖CoWoS®、InFO,和3D IC的多种先进封装技术,能够完成异质和同质芯片整合,以满足客户对运算效能、功耗以及系统设备空间的需求。台积公司将持续优化高性能运算平台,协助客户赢取由海量数据和应用创新所驱动的市场成长。

(3)物联网平台:台积公司提供领先、完备,且高度整合度的超低功耗(Ultra-Low Power, ULP)技术平台来支持物联网及穿戴式装置的产品创新。台积公司领先业界的55纳米ULP技术、40纳米ULP技术、28纳米ULP技术,以 及22纳米ULP/ 超 低 漏 电(Ultra-Low Leakage,ULL)技术,已被各种物联网和可穿戴应用广泛采用。

台积公司更进一步扩展其低操作电压(Low OperatingVoltage, Low Vdd)技术,以满足极低功耗(ExtremeLow Power)产品应用。同时,为了支援物联网边缘计算和无线连网不断增长的需求,台积公司也提供客户最具竞争力且最完备的多样 RF 射频、强化版类比元件、嵌入式快闪存储器、新兴存储器、传感器和显示芯片等特殊制程技术,以及包括领先的整合型扇出(InFO)技术的多种先进的封装技术。

(4)车用电子平台:台积公司提供客户领先的车用技术,满足车用电子产业中的三大应用趋势:更安全、更智能,和更环保。同时,也领先业界推出坚实的车用硅智财生态系统,从16纳米鳍式场效晶体管制程技术起,扩展到N7及N5,以满足汽车产业中两个最需大量运算需求的先进驾驶辅助系统(Advanced DriverAssistance Systems, ADAS) 和先进座舱系统(InVehicle Infotainment, IVI)。

除了先进逻辑技术平台外,台积公司亦提供广泛而且具竞争力的特殊制程技术,包括28纳米嵌入式快闪存储器,28纳米、22纳米,和16纳米毫米波射频,高灵敏度的互补式金氧半导体影像传感器(CMOS Image Sensor, CIS)/光学雷达(Light Detection and Ranging, LiDAR)传感器和电源管理芯片技术。新兴的磁性随机存取存储器(Magnetic

Random Access Memory, MRAM)正在顺利开发中,以满足汽车Grade-1标准的要求。这些技术均符合台积公司基于美国车用电子协会(AutomotiveElectronic Council, AEC)AEC-Q100汽车等级制程规格验证标准。

台积公司将继续强化其核心竞争力,适切规划公司长短期技术及业务发展策略,并协助客户因应电子产品周期快速汰换以及市场上激烈竞争的挑战,以达成投资报酬率与成长目标。

九.协助客户开始设计

台积公司的技术平台提供了坚实的基础,协助客户实现设计,客户得以透过台积公司内部开发的硅智财与工具,或其 OIP 伙伴拥有的硅智财与工具进行芯片设计。

十.技术档案与制程设计套件

电子设计自动化工具的验证是奠定硅智财和客户设计的基础,以确保它们都符合台积公司制造技术上的需求,而验证的结果可于TSMC-OnlineTM 取得。这些验证工具都有相对应的技术档案及制程设计套件(PDK)提供给客户下载来使用。从 0.5 微米到5 纳米制程,台积公司提供广泛的制程设计套件,支援数位逻辑、混合讯号、射频(RF)、高压驱动器、CMOS 影像传感器(CIS)、以及嵌入式快闪技术等应用领域。除此之外,台积公司提供技术档案:设计法则检查(Design Rule Check)、布局与电路比较(Layout Versus Schematic)、寄生元件参数萃取(RC Extraction)、自动布局与绕线(Place-and-Route)及布局编辑器(Layout Editor)以确保电子自动化工具支援其制程技术。

截至2019年,台积公司已在 TSMC-OnlineTM 上提供客户超过1 万600 个不同的技术档案及 360 个制程设计套件。每年客户下载使用技术档案与制程设计套件已超过10 万次。

十一. 元件数据库与硅智财

硅智财是集成电路设计所需要的基本元件,台积公司和生态伙伴针对客户不同的设计应用需求提供了不同种类的硅智财,包括了基础硅智财,类比硅智财,崁入式记忆硅智财,界面硅智财和软智财,为了支援3D IC 客户的需求,台积公司也于2019年开始提供3D IC硅智财。台积公司与其设计联盟合作伙伴为客户提供了丰富的可重复利用硅智财,对许多电路设计来说,这些硅智财是不可或缺的基本元件。

2019年,台积公司扩增其元件数据库与硅智财内容,使其总数超过 2 万 6,000 个,较2018年成长 30%。

十二. 设计方法与流程

参考设计流程是建立在经过验证的电子设计自动化工具上,提供客户额外所需的设计流程方法上的创新来帮助提高生产力。2019年,台积公司透过开放创新平台的合作,克服了关键的设计挑战,针对数位及系统单芯片应用所需的创新 6 纳米及 3D IC 技术发表了完整的参考流程,为了达到效能、功耗与面积的最佳化目的,提供 FinFET 和 TSMC-SoIC® 设计解决方案及设计方法。

未来智能实验室的主要工作包括:建立AI智能系统智商评测体系,开展世界人工智能智商评测;开展互联网(城市)云脑研究计划,构建互联网(城市)云脑技术和企业图谱,为提升企业,行业与城市的智能水平服务。

十三、台积电对产业未来的展望、机会与挑战

集成电路制造服务领域这些年来的成长,主要是由健康的市场需求所驱动。然而,2019新型冠状病毒(COVID-19)全球大流行对整体半导体产业的供给与需求造成不确定性,台积公司考虑可能的影响后,预估整体半导体产业(不含存储器)在2020年将持平或是微幅下跌。然而,就长期而言,因电子产品采用半导体元件的比率提升,无晶圆厂设计公司持续扩大市占率,整合元件制造商委外制造的比例逐渐增加,以及系统公司增加特殊应用元件委外制造等因素,自2019年至2024年,集成电路制造服务领域的成长可望较整体半导体产业(不含存储器)的中个位数百分比年复合成长率更为强劲。集成电路制造服务领域位居整个半导体产业链的上游,其表现与主要产品平台的市场状况息息相关,包含智能型手机、高效能运算、物联网、车用电子与消费性电子产品。

● 智能型手机

智能型手机2018年的单位出货量首次衰退4%,2019年的单位出货量再次衰退 2%,反映许多先进国家和中国市场已趋近饱和。2020年,随着5G商用化开始加速,新的5G智能型手机将缩短整体换机周期,然而,COVID-19全球大流行将可能造成换机延后,台积公司因此预期智能型手机市场于2020年将呈现高个位数百分比衰退。

长期来看,由于智能型手机加速演进至5G,加上拥有更高性能、更长电池使用时间、生理感应器及更多人工智能应用,智能型手机将持续吸引消费者的购买兴趣。低耗电特性的芯片对手机制造商而言是不可缺少的一环,拥有最佳成本、耗电及外型尺寸(芯片面积与高度)潜力的系统单芯片设计,是首选的解决方案,而台积公司在此制程技术方面已居领导地位。对于人工智能应用、各种复杂软件运算与高分辨率视讯处理的高效能需求,将持续加速先进制程技术的推进。

● 高效能运算

高效能运算平台包括个人计算机,平板计算机,服务器,基站,游戏机等。2019年,主要高效能运算产品单位出货量下降了4%,主要由于消费类个人计算机的更换周期延长,企业服务器需求降低以及当代游戏机进入产品生命周期尾端;而5G基站部署及成长之企业个人计算机需求部份抵消了衰退。

2020年,受到COVID-19全球大流行影响,预期高效能运算平台单位出货量将呈现中个位数百分比衰退。尽管如此,多项因素预期将推动高效能运算平台需求,包括:持续的5G基站部署,增长的数据中心人工智能服务器需求以及新一代游戏机的上市等。这些都需要高效能及高功耗效率的中央处理器、绘图处理器、网络处理器、人工智能加速器与相关的特殊应用集成电路,并将驱使整体高效能运算平台朝向更丰富的半导体内容与更先进制程技术迈进。

● 物联网

物联网平台包含如智能穿戴、智能音箱、与网络监视器等各式各样联网装置。2019年物联网装置单位出货量成长25%,蓝牙耳机,智能手表与智能音箱为主要成长动能。

展望2020年,尽管受到COVID-19全球大流行的影响,在蓝牙耳机,智能手表与智能音箱持续成长,以及其他各式各样应用持续发展,物联网装置单位出货量将呈现中十位数百分比的成长。伴随更多的人工智能功能的加入,物联网装置将带动更多需求于更强大却更省电的控制芯片、联网芯片与感测芯片。台积电提供高效能、低功耗的制程技术来强化客户竞争力以赢得市场。

● 车用电子

2019年,因为全球经济环境转弱的影响,汽车单位销售量衰退5%;2020年,受到COVID-19全球大流行与整体经济持续的不确定性因素影响,预计将再次衰退低十位数百分比。

展望未来,预期电动车,先进驾驶辅助系统及信息娱乐系统需要更丰富的半导体内容,将带动处理器、传感器、类比及电源集成电路等需求。台积公司提供各种车用制程技术以帮助客户在车用市场取得胜利。

● 消费性电子产品

2019年,消费性电子产品单位销售量衰退7%;电视及机上盒销售量受全球经济环境的不确定因素影响而降低,而MP3播放器、数位相机市场则持续受到智慧型手机的侵蚀,销售量皆呈现下滑。

展望2020年,整体消费性电子产品出货量预计将维持下滑,但是其中的4K及8K超高分辨率电视出货将达到正成长。此外,电视上使用人工智能技术来提高画面质量、语音控制等功能已成为未来趋势。预期台积公司将掌握此波趋势,以广泛的先进制程技术以满足客户对市场趋势之需求。