【汇编语言与计算机系统结构笔记20】补充内容:可定制处理器指令集

本次笔记内容:

31.补充内容——可定制处理器指令集-1

32.补充内容——可定制处理器指令集-2

注:我找到了对应内容的课件,请见我于GitHub的CS笔记仓库。

本节课对应幻灯片:汇编语言程序设计-可定制处理器指令集.pdf,第1页起。

本系列课程最后一节!

老师做一些扩展方面的阅读,老师也从事这方面的研究。

文章目录

- 应用为中心的定制化处理器及指令

- 应用潜力

-

- 云计算时代

- 超级计算领域应用定制化处理器

- 一些技术

- Xtensa

-

- Xtensa指令集

- Tensilica Instruction Extension

-

- Overflow

应用为中心的定制化处理器及指令

随着处理器片上资源的日益丰富,如何充分利用这些资源成为首要问题:

- 通用处理器之所以是通用处理器,因为其所面临的应用种类复杂:如桌面应用

但是应用领域日益细分,移动计算、云计算等范围越来越广:

- 不存在“通用”的嵌入式处理器

- 会出现越来越多的为应用定制的指令系统

应用潜力

云计算时代

传统的基于PC机的个人信息访问与处理模式将被更加多样化、网络化的模式所替代。

网络的快速发展以及各种网络终端的引入使得信息处理的界限变得模糊——通过大型数据中心提供IT基础设计、存储资源以及应用服务成为趋势。

未来的数据中心可能将承担大量需求各异的数据处理任务,包括文本分析搜索、媒体处理、数据统计、事务处理等等。

针对需求各异的应用,可以设计分别为其定制的处理器结构与指令:首先分析应用的计算、访存与通讯特征,并通过处理器结构的裁剪与扩展(包括指令扩展与存储结构扩展等),在一定的功耗与面积限制前提下使得处理器资源能够发挥最大的效能。

这一点与桌面计算机不同:

- 后者承担的任务种类繁多,很难实现定制化结构设计,而只能使用通用处理器;

- 但是前者,因为数据中心内的处理器数目巨大,且需要面临海量的处理请求,这就使得差异化的定制处理器有了发挥空间——可以集中处理各自所适合的应用,同时定制化处理器通常能够获得很高的性能功耗比。

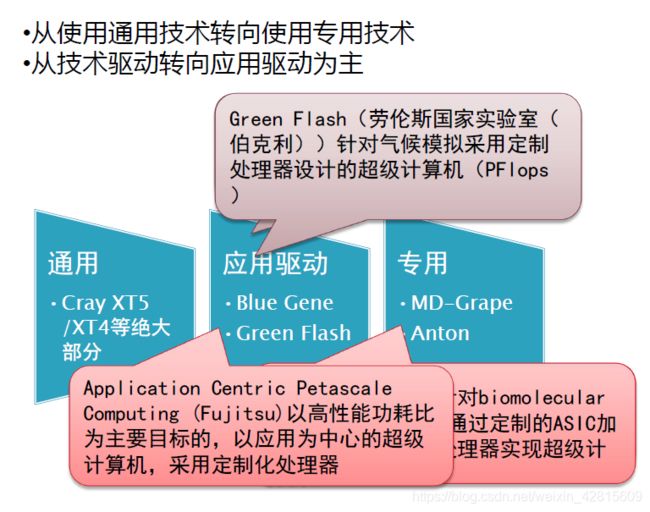

超级计算领域应用定制化处理器

通用处理器在高性能计算领域的问题面临功耗大、效率低与可靠性低等问题。

实际上,能充分利用超级计算系统计算能力的应用是非常有限的,针对关键应用,采用应用定制的方法进行处理器结构设计是有效的大大提升处理效率的方法之一。

定制化方法在嵌入式处理器领域已经成熟,借鉴该方法,将其应用于高性能计算领域。

一些技术

传统的处理器设计:所有的设计与上一代兼容,追求大而全。但是定制处理器只保留核心,并且做横向拓展,不追求大而全。

Xtensa

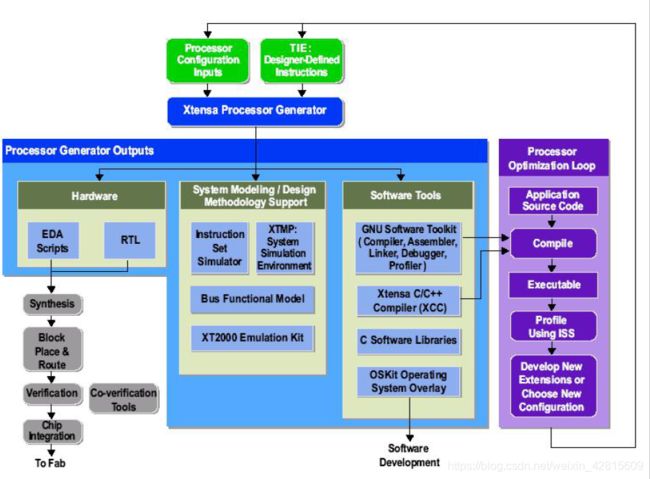

tensilica 研发出世界第一个可以灵活定制与扩展的微处理器结构Xtensa;并自动提供一个软件开发、模拟、验证环境。

采用 Xtensa技术后,系统设计工程师可以挑选所需的体系结构单元,再加上自定义的新指令与硬件执行模块,就可以设计出具有更高性能的处理器内核。

Xtensa 生成器可以针对每一个处理器的特殊定制,自动有效地产生出一套包括操作系統,编译环境,模拟环境在内的完善软件工具。

Xtensa指令集

有一套专门为嵌入式系统设计的,精简高效的16/24

bit指令集。

其核心拥有80条 RISC 指令,支持——32位 算逻部件(ALU)、6个管理特殊功能的寄存器、32或64个普通功能32位寄存器等。这些32位寄存器具备寄存器窗口功能。

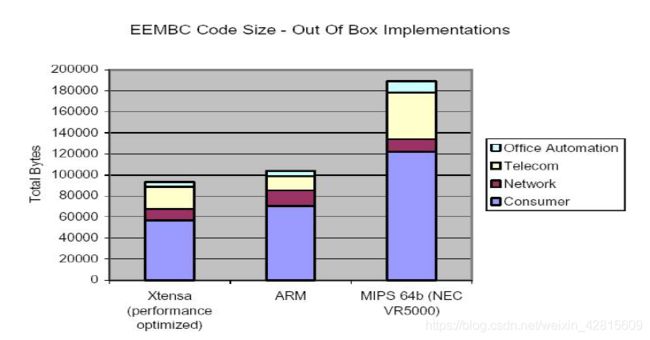

可以帮助系统设计师大量缩减编码长度,从而提高指令的密度并降低能耗。这是降低成本的重要关键。

典型的RISC指令级具有如下特点:

- 固定的指令字长;

- 较大的寄存器堆;

- 简单固定的指令编码格式;

- 访存模式简单。

RISC 缺点:生成的目标程序较大,指令字段的利用不高,导致功耗与性能的损失。

因此,Xtensa 做出些改进。

一、混合的指令宽度(16/24bit)

- 大多数频繁使用的指令都有16bit版本,包括load/store/branch/ALU/Logic/Move等;

- 16bit与24bit指令可以混合运行,不需要模式切换。

二、功能强大的跳转指令

- 大量的compare-and-branch指令,包括与常数的比较以及基于某些条件位的跳转;

- 零负载的循环跳转指令支持。

三、可变长的寄存器窗口机制

- 16个可见的寄存器;但物理寄存器多于此数(32-64个);

- 支持多个寄存器窗口,降低了进程切换/异常处理的数据保存与恢复的负载;同时寄存器窗口的重叠使得过程调用更加高效;

- 支持可变长的寄存器窗口覆盖,提高了利用效率。

Tensilica Instruction Extension

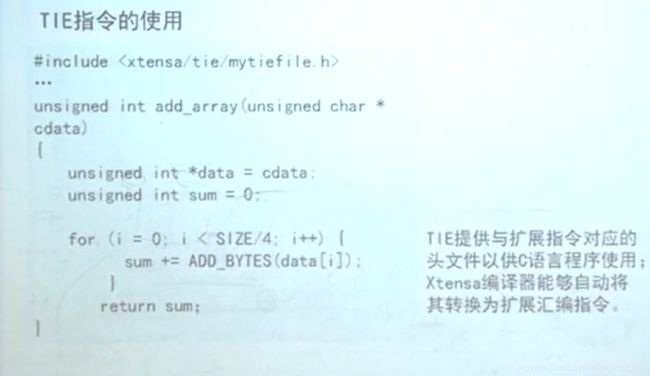

Tensilica Instruction Extension (TIE) 是一种用于扩展Xtensa处理器功能的描述语言。

- TIE可以描述欲扩展的机器指令、新的寄存器以及执行单元,这些内容最终将被自动添加至新的处

理器中。 - TIE 扩展自动进行流水线划分,相关逻辑自动生成。

Overflow

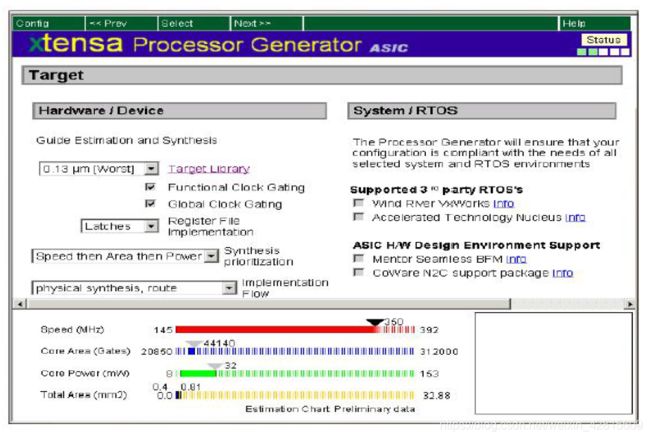

Processor Generator:在一小时内完成一个优化的CPU设计!Xtensa Processor Generator——一个使用方便的,基于图形界面的CPU设计配置工具。

Software Development Environment:自动生成基于GNU的tool chain,包括 GNU C/C++ 编译器,汇编器,连接器,调试器,软件性能分析工具,指令级模拟器与基本的 C 运行时库;优化的编译器;支持片上多处理器的指令级模拟器及基本开发库。

总之,Xtensa 提供的服务很全。