Xilinx的FPGA硬件设计一——电源篇

FPGA最小系统说白了就是设计一个最小系统,其可以作为日后一系列产品的基础,一是可以加快开发流程,二是可以降低开发难度,本次选用的芯片是Xilinx(赛灵思)的7系列(ARTIX)的FPGA。

FPGA的外设是可编程实现的,所以如串口、SPI、IIC等这些标准接口没有固定的外设接口,其完全可以在逻辑中编写,因此在本方案中不涉及,只是针对FPGA最小系统和常用的外设工作所必要的资源进行设计如电源、Flash、JTAG等。

下图为FPGA最小系统框图,包括:电源、QSPI-FLASH、JTAG、时钟、ADC(本次不涉及,可以无视)。其中电源和时钟是整个系统最为重要部分,电源为系统提供动力,时钟为系统提供时序基础。

本博客所选用型号的是XC7A75TFGG484,其与XC7A50TFGG484、XC7A35TFGG484在硬件上是完全兼容(PIN对PIN),它们只是在资源上的丰富程度不一样,其他的都一样。

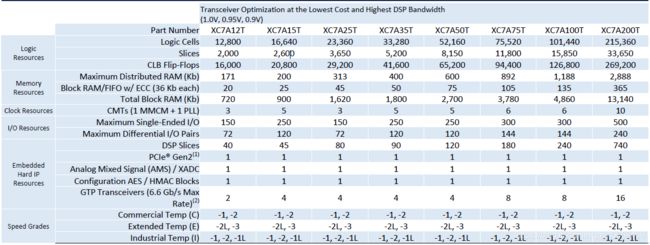

ARTIX系列FPGA引脚相同其硬件设计都一样,如下图所示200T的资源最多其中CLB可达269200,75为94400,详细资源见下图,虽然本方案基于75设计但不是仅针对75而是整个ARTIX系列都通用。

电源是整个板卡的动力因此在方案中首先要统计出需要用到多少器件和每个器件的功耗,累加计算出整个板卡的总功耗,一般是按70%---80%的效率设计整个电源方案。

本方案中用到的器件主要有:FPGA、FLASH。查看FPGA电源特性手册《DC and AC Switching Characteristics》知FPGA不同电源需要的功耗不同。

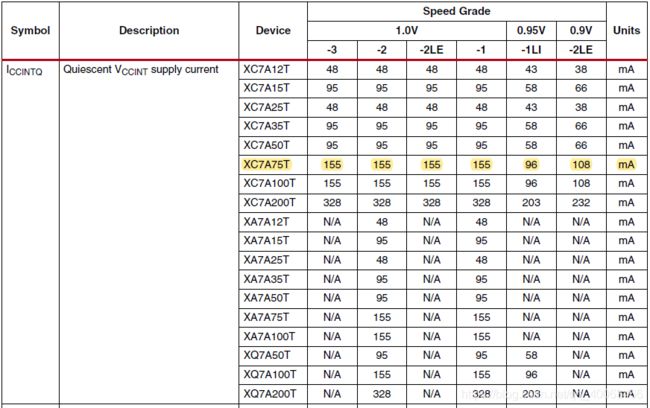

如下图所示,75系列内核电流在不同速度等级下电流不同,但最高为155mA。

如下图所示,75系列RAM电流在不同速度等级下电流相同,为4mA。

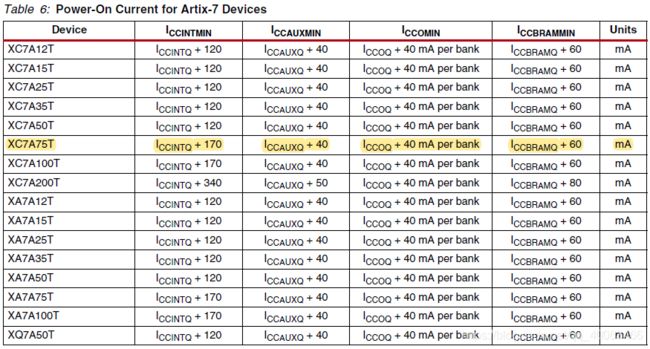

如下图所示,75系列FPGA在上电过程中电流要比在正常工作中要大很多,因此为了保证FPGA能够正常启动提供的电流必须大于启动电流,具体各个电源所增加的电流可以看下图。

同理查看各个芯片的数据手册查看其最大工作电流,其具体统计如下表所示:

| 序号 |

型号 |

厂家 |

名称 |

数量 |

电流(A) |

功耗(W) |

||

| 3.3V |

1.8V |

1.0V |

||||||

| 1 |

XC7A75TFGG484 |

Xilinx |

FPGA |

1 |

(0.004+0.04)*5 |

0.036+0.04 |

(0.155+0.17) +(0.004+0.06) |

1.26 |

| 2 |

N25Q128 |

Micron |

Flash |

1 |

0.02 |

|

|

0.066 |

| 4 |

TPS51200DRCR |

TI |

电源 |

1 |

- |

- |

|

|

| 5 |

TLV62130RGT |

TI |

电源 |

4 |

- |

- |

|

|

| 6 |

统计总功耗 |

- |

- |

- |

0.24 |

0.076 |

0.389 |

1.326 |

| 7 |

按效率80%计算 |

- |

- |

- |

- |

- |

- |

1.8 |

相对于单片机功能强大的CPU和FPGA是对上电时序(上电顺序和时间)是有较强要求的,否则会烧毁芯片或者芯片无法正常工作,同理本方案的FPGA有上电时序要求。

ARTIX系列FPGA所包含的电源有:VCCINT(内核电源);VCCBATT(加密内存供电电源);VCCAUX(辅助电源);VCCAUX_IO(辅助IO电路电源);VCCBRAM(逻辑模块RAM);VCCO_0(配置BANK供电电源);VCCO_14、VCCO_15(外设电源),其中每个BANK的电压可以不同,可以是1.5V、1.8V、2.5V或3.3V。

如下图所示ARTIX系列FPGA所包含的电压名称和功能如下图所示。

如下图所示,FPGA官方推荐上电时序为:VCCINT--->VCCBRAM--->VCCAUX(VCCBATT)--->VCCO;下电时序则与上电时序相反为:VCCO--->VCCAUX(VCCBATT)--->VCCBRAM--->VCCINT。

如果VCCINT和VCCBRAM的供电电压一样,那么他们是可以同时上电的,若VCCAUX和VCCO也具有相同的供电电压,那么他们也可以同时上电,若VCCBATT用到(即需要掉电保存数据)外接纽扣电池,若没有用到则可以接地或者和VCCAUX用同一电源。

对于高速BANK(HR I/O BANK)和BANK0配置电压VCCO为3.3V时VCCO和VCCAUX的电压差不能能超过2.625V,不然器件会烧坏。

FPGA的PCIE接口(BNAK-216)相对于其他BANK为独立模块,为了获得GTP最小上电电流,其上电时序为VCCINT->VMGTAVCC->VMGTAVTT或VMGTAVCC->VCCINT->VMGTAVTT,其中VMGTAVCC和VCCINT可以用同一电源。

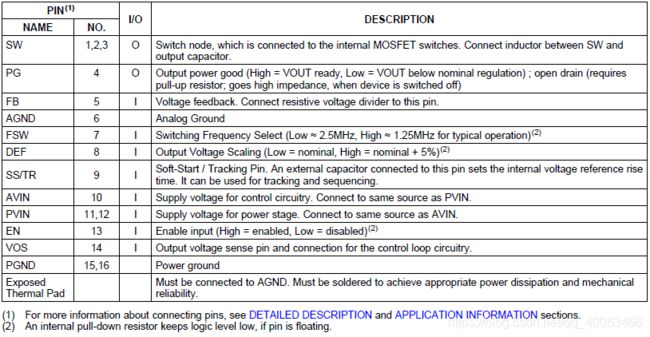

根据对整个板卡功耗的统计,电源芯片选用TI的TLV62130RGT其具有宽输入电压范围(4V—17V)和可调节输出电压(0.9V-5V)并具有高达3A的输出电流能力,其引脚定义如下图所示。

根据上面对FPGA的电源作用和上电时序说明,现板卡电压供电方案如图九所示,首先是经过LDO芯片将总电压降到内核电压,当内核电压稳定后通过PG引脚控制下一级电源上电以此类推。

经过上面的分析和设计知道,要想FPGA能够正常工作需要注意它的上、下电时序和电源功耗,因此在设计中务必要保证这两点。

当然,现在已经有一整套基于FPGA的电源方案,即将FPGA所需电源都集成在一个芯片上如:LTM4644IY其包含所有FPGA所需电源。

好了,就先写这么多吧,剩下的留着下次写,哈哈哈哈~~~~~~~。