AXI_05 AXI_FULL_IP的设计与验证

由于该系列文章阅读有顺序性,所以请跳转至该系列文章第一篇从头开始阅读,并按照文章末尾指示按顺序阅读,否则会云里雾里,传送门在此: https://blog.csdn.net/qq_33486907/article/details/88289714 《AXI_01 《AXI总线系列文章》由来》

目录

1. AXI_FULL_IP

1.1 AXI_FULL_MASTER_IP设计

1.1.1 STEP1: 利用向导建立一个axi_full_master的IP核模板

1.1.2 STEP2: 在AXI模板中制定用户逻辑

1.1.3 STEP3: 配置IP核

1.2 AXI_FULL_SLAVE _IP设计

1.2.1 STEP1: 利用向导建立一个axi_full_slave的IP核模板

1.2.2 STEP2: 配置IP核

1.3 AXI_FULL_MASTER_IP 与 AXI_FULL_SLAVE_IP的联合仿真验证

1.3.1 STEP1: 搭建仿真工程

1. AXI_FULL_IP

前面文章的内容阐述了AXI_LITE总线的主从设备,以及对应的验证示例。已知AXI_LITE总线只能承担起轻量级的数据传输,数据量较大时还是要使用全功能的AXI总线才行,本节内容将围绕如何建立全功能AXI总线主控制器AXI_FULL_MASTER_IP展开。

1.1 AXI_FULL_MASTER_IP设计

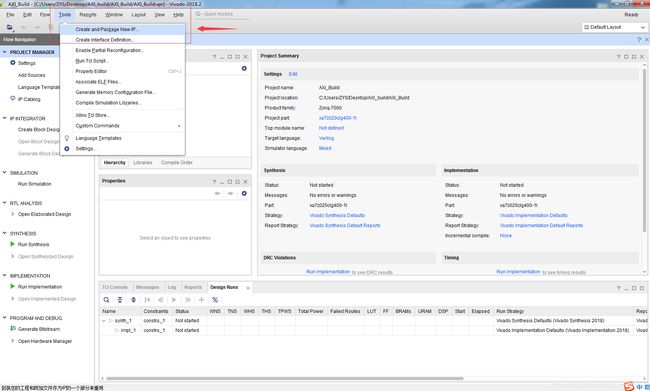

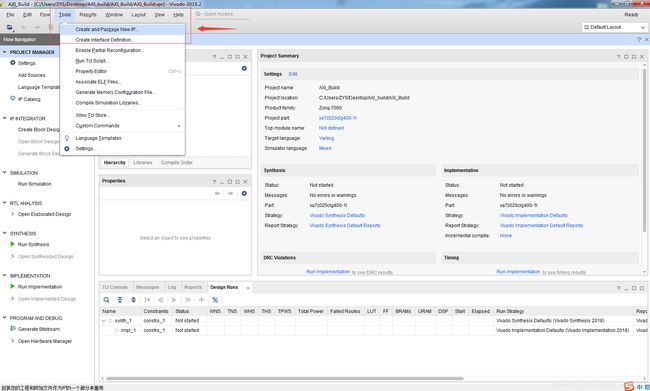

再次打开AXI_LITE_SLAVE_IP中建立的空白工程AXI_Build,来建立axi_lite_mater的自定义IP核。

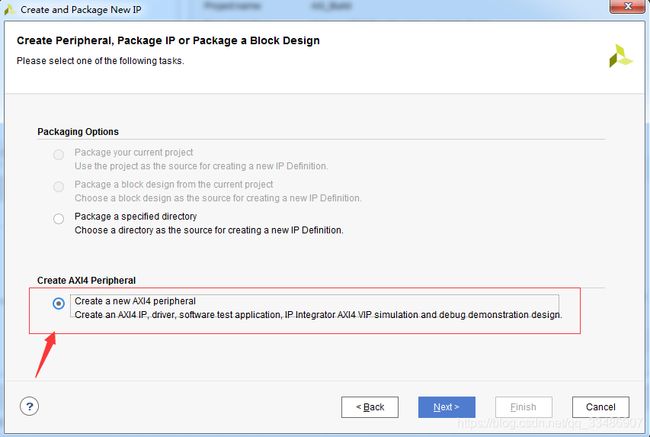

1.1.1 STEP1: 利用向导建立一个axi_full_master的IP核模板

随后将打开一个基于AXI_FULL总线的IP核模板工程,可以在该模板工程下对工程的功能进行修改; 模板中给出以先进行连续寄存器写操作,紧接着在进行读操作的例子,并且没有用户端口,所以要使用必须对IP进行修改,达到读写操作可通过用户端口控制的效果;

1.1.2 STEP2: 在AXI模板中制定用户逻辑

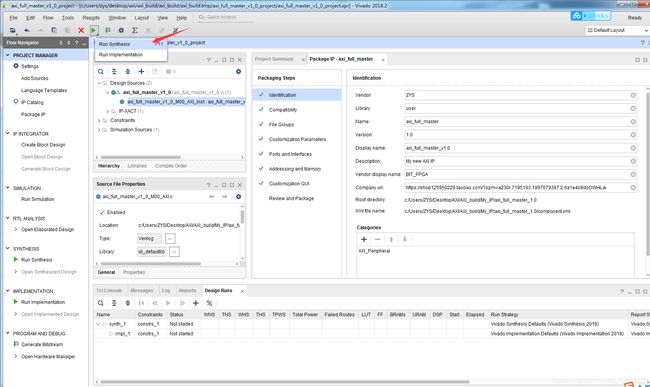

这里要逻辑功能修改为使用用户端口可控的AXI_FULL主设备,具体添加的代码就不再这里给出了,可以打开对应的IP核文件进行查看,添加的代码会在文件中进行明确的注释;把要添加的代码添加完成以后,运行一下run synthesis综合一下看看有没有错误;

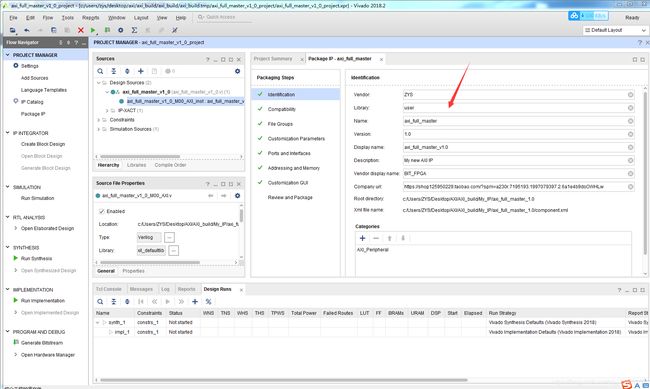

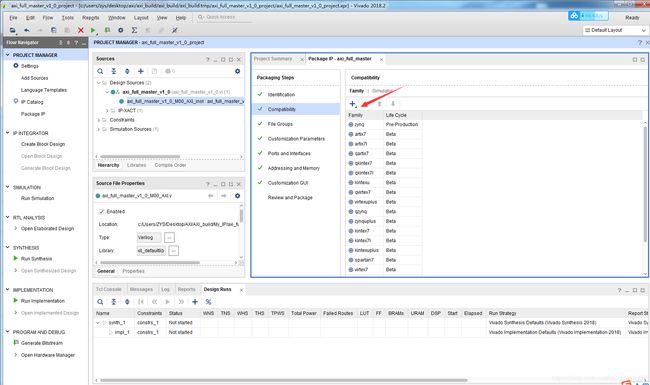

1.1.3 STEP3: 配置IP核

添加所有系列,以支持在所有器件上使用;

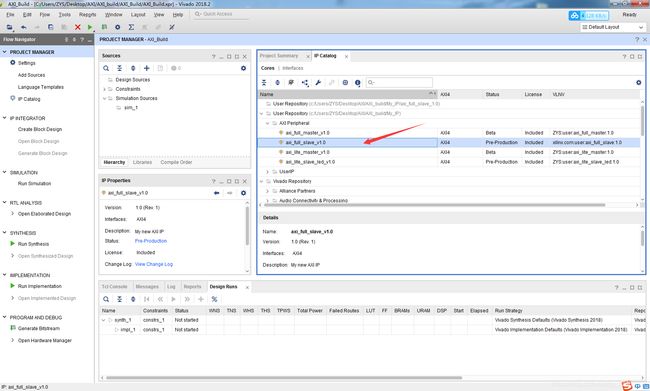

其余步骤不再赘述,请参考前面的文章;之后可以在IP Catalog中看到这个IP核了,如下图:

1.2 AXI_FULL_SLAVE _IP设计

为了验证AXI_FULL_MASTER IP核的设计的正确性,使用向导生成一个AXI_FULL_SLAVE_IP,进行联调测试;

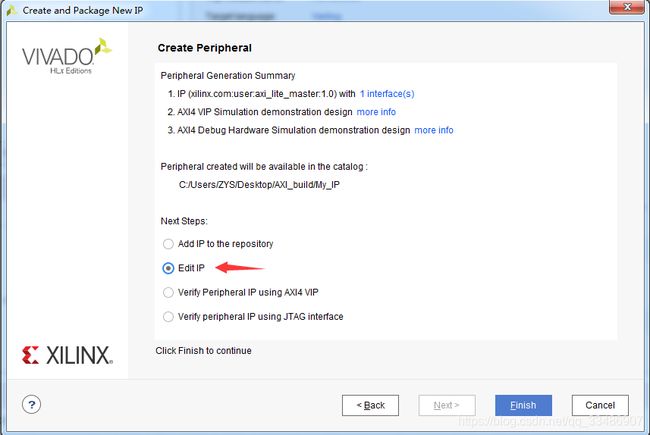

1.2.1 STEP1: 利用向导建立一个axi_full_slave的IP核模板

随后将打开一个基于AXI_FULL总线的IP核模板工程,该工程无需修改;

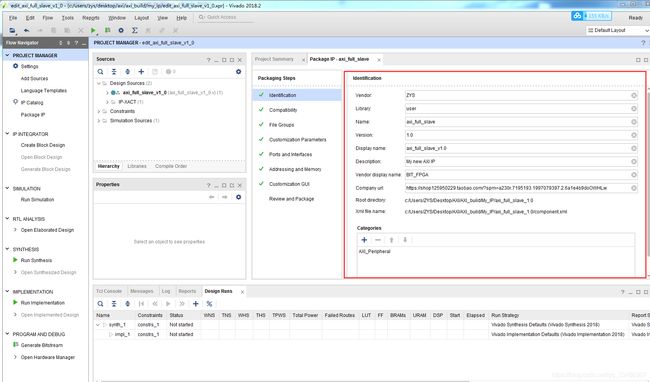

1.2.2 STEP2: 配置IP核

添加所有系列,以支持在所有器件上使用;

其余步骤不再赘述,请参考前面文章的步骤;之后可以在IP Catalog中看到这个IP核了,如下图:

1.3 AXI_FULL_MASTER_IP 与 AXI_FULL_SLAVE_IP的联合仿真验证

1.3.1 STEP1: 搭建仿真工程

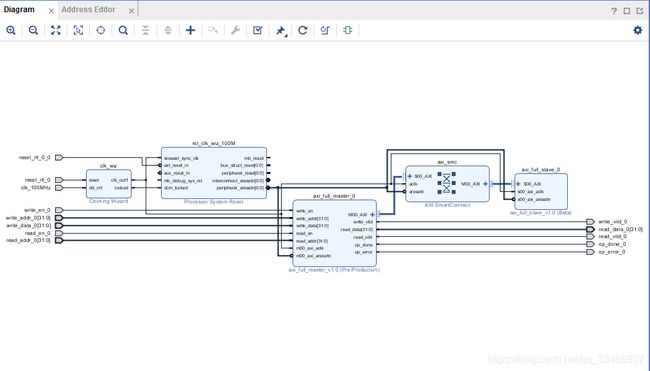

建立一个工程命名为axi_full_simulate,工程建立完毕以后,如下图所示:

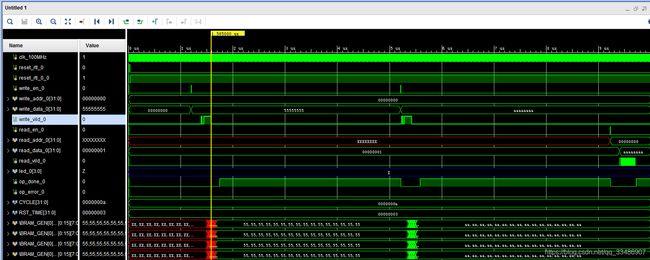

具体细节和仿真代码,可在实际工程中查看。现在给出仿真结果:

从仿真结果可以看出,主设备往从设备的进行了两次突发写操作,每次突发长度为16个数据;后进行了一次长度为16的突发读操作,数据分别为0x5555_5555 0xAAAA_AAAA;

至此标准的AXI总线IP核就设计完毕了; 后面还有一种AXI_Stream总线会单独章节输出。

不要急着跑,干货在后面,下一篇文章传送门在此: AXI_Stream等我写完了再发布

本篇IP核源码工程和验证工程传送门在此,扫一扫获取下载链接:

![]()

或直接点击下载链接:https://item.taobao.com/item.htm?spm=a1z38n.10677092.0.0.22131debncNwzA&id=588531553802