1、sdc文件也是要添加到Quartus 软件中,这样在执行Read SDC File命令时才能读到相应的文件。

2、在TimeQuest打开的条件下,重新编译工程之后要Update Timing Netlist,这样TimeQuest分析器会得到最新的

网表文件进行时钟分析。

转载地址http://www.cnblogs.com/pejoicen/p/4194380.html

PLL时钟约束

# Uncommenting one of the following derive_pll_clocks lines

# will instruct the TimeQuest Timing Analyzer to automatically

# create derived clocks for all PLL outputs for all PLLs in a

# Quartus design.

# If the PLL inputs are constrained elsewhere, uncomment the

# next line to automatically constrain all PLL output clocks.

derive_pll_clocks

# If the PLL inputs are not constrained elsewhere, uncomment

# the next line to automatically constrain all PLL input and

# output clocks.

# derive_pll_clocks -create_base_clocks

方法 1 – 自动创建基时钟和 PLL 输出时钟

这一方法使您能够自动地约束 PLL 的输入和输出时钟。ALTPLL megafunction 中指定的

所有 PLL 参数都用于约束 PLL 的输入和输出时钟。自动更新了 ALTPLL megafunction

的修改。当创建 PLL 的输入和输出时钟时,不必跟踪 PLL 参数的更改或指定正确的值。

为了自动约束所有输入和输出 , 要将 derive_pll_clocks 命令和 -create_base_clocks

选项一起使用。基于 PLL 的 MegaWizard TM Plug-In Manager 例化,TimeQuest

analyzer 确定正确的设置。

例

derive_pll_clocks -create_base_clocks

方法 2 – 手动创建基时钟和自动创建 PLL 输出时钟

通过这种方法 , 可以手动约束 PLL 的输入时钟并且使 TimeQuest analyzer 能够自动

约束 PLL 的输出时钟。除此之外 , 与 ALTPLL megafunction 中指定的输入时钟频率相

反,您可以指定一个不同的输入时钟频率。通过使用 ALTPLL megafunction 中指定的

参数自动创建 PLL 输出时钟。您可以尝试不同的输入时钟频率 , 同时保持相同的 PLL

输出时钟参数。

1 确保指定的所有输入时钟频率与当前配置的 PLL 相兼容。

可以将此方法与 derive_pll_clocks 命令一起使用并且手动创建 PLL 的输入时钟。

例

create_clock -period 10.000 -name clk [get_ports {clk}]

derive_pll_clocks

方法 3 – 手动创建基时钟和 PLL 输出时钟

通过这种方法 , 可以手动约束 PLL 的输入时钟和输出时钟。指定了所有的 PLL 参数并

且参数值可以不同于 ALTPLL megafunction 中指定的参数值。除此之外 , 您可以尝试

各种 PLL 输入和输出频率以及参数。

您可以将该方法与 create_clock 和 create_generate_clock 命令的组合一起使用。

例

create_clock -period 10.000 -name clk [get_ports {clk}]

create_generated_clock \

-name PLL_C0 \

-source [get_pins {PLL|altpll_component|pll|inclk[0]}] \

[get_pins {PLL|altpll_component|pll|clk[0]}]

create_generated_clock \

-name PLL_C1 \

-multiply_by 2 \

-source [get_pins {PLL|altpll_component|pll|inclk[0]}] \

[get_pins {PLL|altpll_component|pll|clk[1]}]

时钟约束出错

Warning (332174): Ignored filter at SDC1.sdc(1): CPU_clk could not be matched with a port

![]()

Warning (332049): Ignored create_clock at SDC1.sdc(1): Argument

![]()

Warning (332060): Node: SYS_clk was determined to be a clock but was found without an associated clock assignment.

没有对时钟进行约束设置

Node:

CAUSE: This can be caused in two ways: 1) A clock assignment was determined to be invalid, so its source objects no longer have a clock associated with them. 2) When analyzing the netlist, the node was found feeding a clock port with no other clocks feeding it.

ACTION: Use the derive_clocks command to automatically find all clock nodes in the design. Also, for any clocks that were ignored, review the warning or error message associated with the command to prevent the clock from being ignored.

Timequest timing analyzer使用方法

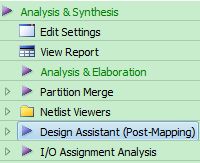

步骤1:执行初始编译

在应用时序约束设计之前,通过表1创建一个初始数据库。初始数据库从设计的post-map结过中生成。

表 1-1. 执行初始编译 (1)

| Quartus II软件GUI |

命令行 |

| 在Processing菜单上,指向Start,点击Start Analysis & Synthesis。 |

输入: quartus_map filtrefr |

表 1-1注释:

-

quartus_map用于创建一个post-map数据库。

-

Analysis & Synthesis阶段生成post-map数据库。

-

您也可以为初始数据库创建一个post-fit网表。不过,创建一个post-map网表耗时较少,并且用于本教程的例子已经足够了

步骤2:运行TimeQuest Timing Analyzer

通过表 2-1中的程序,运行TimeQuest Timing Analyzer来创建和验证所有时序约束和例外。此命令将打开TimeQuest shell。

表 2-1. 运行TimeQuest Timing Analyzer

| Quartus II软件GUI |

命令行 |

| 在Tools菜单中,单击TimeQuest Timing Analyzer。 |

输入: quartus_sta –sr project_open fir_filter -revision filtrefr |

1 当您直接从Quartus II软件中运行TimeQuest Timing Analyzer时,当前工程将会自动打开。如果使用GUI,那么当出现下面的消息时,请选择No:

"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist. Would you like to generate an SDC file from the Quartus Settings File?"

步骤3:创建一个Post-map时序网表

在指定时序要求之前,请创建一个时序网表。您可以从post-map或post-fit数据库中创建一个时序网表。在这一步骤中,通过表 3-1中的程序,从"步骤1:执行初始编译"中创建的post-map数据库中创建一个时序网表。

表 3-1. 创建一个Post-Map时序网表

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Netlist菜单上,点击Create Timing Netlist。 出现 Create Timing Netlist对话框。 2.在Input netlist中,选择Post-Map。 3.点击OK。 |

输入:create_timing_netlist –post_map |

1 您不能在Tasks面板中使用Create Timing Netlist命令来创建一个post-map时序网表。默认情况下,Create Timing Netlist需要一个post-fit数据库。

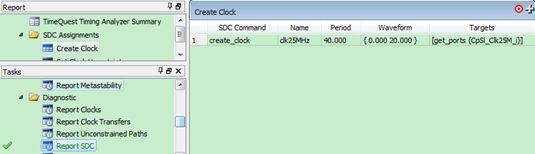

步骤4:指定时序要求

在设计中定义时钟。每个时钟的属性列表请参考表 4-1。

表 4-1.设计中的时钟

| 时钟端口名称 |

要求 |

| Cpsl_Clk25M_i |

50/50占空比的25 MHz |

在设计中创建时钟并通过表 4-2中的程序分配正确的时钟端口。要了解关于TimeQuest Timing Analyzer所支持的约束的详细信息,请参考Quartus II 手册 第3卷中的TimeQuest Timing Analyzer章节。

表 4-2. 创建时钟并分配时钟端口

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Constraints菜单中,点击 Create Clock。出现Create Clock对话框。对25 MHz时钟指定参数。单击RUN。 |

输入: #create the 25 MHz (20 ns) clock create_clock –period 20 [get_ports Cpsl_Clk25M_i] |

| 2. 在Constraints菜单中,点击Drive PLL clocks。出现Drive PLL clocks对话框,前面指定了PLL基时钟,什么都不选直接单击RUN即可。 |

1 默认情况下,如果未使用-waveform选项,那么create_clock命令假设50/50的占空比。

f 要了解关于创建不同占空比时钟的详细信息,请参考Quartus II手册 第3卷中的TimeQuest Timing Analyzer章节。

完成表 4-2中显示的程序后,时钟定义完成。

步骤5:更新时序网表(timing Netlist)

在您创建时序约束或例外后,通过表 5-1中的程序,对时序网表进行更新,将所有时序要求应用到时序网表(新的clk和clkx2时钟约束)。

1 只要应用了新的时序约束,就必须对时序网表进行更新。

表 5-1. 更新时序网表(Timing Netlist)

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Update Timing Netlist命令。 |

输入:update_timing_netlist

|

步骤6:保存Synopsys Design Constraints(SDC)文件

在为设计指定时钟约束并更新时序网表后,您可以通过表 6-1中的程序来选择创建SDC文件。通过TimeQuest Timing Analyzer GUI或者在控制台(console)中指定的约束不会自动保存。

1 如果您在设计流程中无意覆盖任何约束,那么请使用这个初始SDC文件来恢复所有约束。初始SDC文件可作为包含设计的原始约束和例外的"golden" SDC文件。

表 6-1. 保存SDC文件

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Tasks面板中,双击Write SDC File命令。出现Write SDC File对话框。 2.在File Name栏输入名称。 |

输入:write_sdc -name.sdc r |

新的.sdc文件包含"步骤4:指定时序要求"中定义的时钟约束。Write SDC File命令可以覆盖任何现有的SDC文件。当这种情况出现时,新的SDC文件没有保持顺序或注释。因此,Altera建议单独保存利用文本编辑器可以手动编辑的一个golden SDC文件。这使您能够根据自身的规范输入注释并组织文件。

步骤7:对初始时时序网表生成时序报告

通过表 7-1中的程序定义的时钟,在指定时序约束和更新时序网表后,生成时序报告,这验证了时钟被正确地定义并应用到正确的节点。TimeQuest Timing Analyzer提供易于使用的报告生成命令,使您能够验证设计中的所有的时序要求。

表 7-1. 保存SDC命令

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Report SDC命令。 |

输入:report_sdc |

图 13生成SDC约束报告(SDC Assignments Report)

SDC Assignments报告了在指定设计中包含的所有时序约束和例外。生成两个报告:一个用于时钟和一个用于时钟组。

可以用表 7-2中的程序生成一个报告,来总结设计中所有的时钟。

表 7-2. 生成报告时钟报告(Report Clocks Report)

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Report Clocks命令。 |

输入:report_clocks |

![]()

图 14时钟报告

通过表 7-3中的程序,使用Report Clock Transfers命令生成一个报告来验证所有的时钟到时钟传输都是有效的。这种报告包含设计中所有的时钟到时钟传输。

表 7-3. 生成报告时钟传输(Report Clock Transfers)

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Report Clock Transfers命令。 |

输入:report_clock_transfers |

![]()

图 15时钟传输报告(Clock Transfers Report)

本环节只是告诉这个部分伪路径可以作为例外不进行分析。实际的时序要在做设计时保证其正确。So,不再详细描述,以后可能会补充。

Clock Transfers报告表明在clk(源时钟)和clkx2(目的时钟)之间存在跨时钟域路径。共有16条路径,其中clk为源节点提供时钟,clkx2为目的节点提供时钟。

在fir_filter设计中,不必分析clk至clkx2的时钟传输,因为它们是忽略路径。通过表 7-4中的程序声明clk至clkx2的路径为伪路径。当完成该程序后,TimeQuest Timing Analyzer表明Clock Transfers报告是过时的。

表 7-4. 声明伪路径

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Clock Transfers报告中,在From Clock列选择clk。 2.右击并选择Set False Paths Between Clock Domains。这个命令表明将所有由clk驱动的源寄存器到由clkx2驱动的目的寄存器之间的路径设为伪路径。 |

输入: set_false_path -from [get_clocks clk] \ -to [get_clocks clkx2] r |

1 另外,也可以使用set_clock_groups命令来声明两个时钟域之间的路径为伪路径。例如,set_clock_groups -asynchronous -group [get_clocks clk] -group

[get_clocks clkx2]。该命令表明clk到clkx2以及clkx2到clk的所有路径为伪路径。此方法是优选的。

由于您添加了一个新的时序约束,通过表 2-14中的程序更新时序网表(timing netlist)。

表 2-14. 更新Timing Netlist

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Update Timing Netlist命令。 |

输入:update_timing_netlistr |

在GUI中输入set_false_path后,所有生成的报告面板上都标有"Out of Date",这表明报告面板不包含反映TimeQuest Timing Analyzer中当前状态的约束或者例外的结果。要更新报告面板,必须重新生成所有的报告。

在命令行,重新输入命令。在GUI中,右击报告面板列表中任何过时(out-of-date) 的报告,并选择Regenerate或Regenerate all。

更新时序网表后,通过表 2-15中的程序验证时钟到时钟传输已经被声明为伪路径。

表 2-15. 验证使用Report SDC命令

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Report SDC。 |

输入:report_sdcr |

图 2-4显示了新的SDC Assignments报告。

![]()

图 2-4中显示的报告表明时钟约束和伪路径是正确的。

使用Report Clocks和Report Clock Transfers命令来验证这两个时钟已经从分析中移除了。图 2-5显示了Clock Transfers报告。

步骤8:保存约束到SDC文件

在指定设计中所有的时钟约束和伪路径后,通过表 8-1中的程序将时序约束和例外保存到SDC文件。

表 8-1. 保存约束到SDC文件

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Tasks面板中,双击Write SDC File。出现Write SDC File对话框。 2.在File name栏,输入-name.sdc. |

输入:write_sdc -name.sdc |

1 这一过程覆盖之前所创建的filtref.sdc文件。如果通过Write SDC File命令覆盖SDC,那么在新的SDC文件中移除了定制的格式和注释。

.sdc 文件包含时钟约束和伪路径例外。

步骤9:执行Timing-Driven编译

保存约束到SDC文件后,在设计上运行一个全编译以优化布线,从而符合约束。不过,在开始全编译之前,通过表 9-1中的程序将SDC添加到工程中。

表 9-1. 添加SDC文件到工程中

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Project菜单中,点击Add/Remove Files In Project。出现Add/Remove Files In Project对话框。 2.通过浏览来选择.sdc。 3.点击OK。 |

输入: set_global_assignment -name SDC_FILE \ -name.sdc |

将SDC添加到工程后,通过表 9-2中的程序,在设计上运行一个全编译。

表 9-2. 运行一个全编译

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Processing菜单中,点击Start Compilation。 |

输入:quartus_sh --flow compile -name |

完成编译后,TimeQuest Timing Analyzer在Compilation Report中生成时钟建立和时钟保持的检查总结报告。

步骤10:在TimeQuest Timing Analyzer中验证时序

要获得指定路径中详细的时序分析数据,请查看TimeQuest Timing Analyzer中的时序分析结果。

1 完全执行布线布局功能(place-and-route)后,运行"步骤2:运行TimeQuest Timing Analyzer"中所介绍的TimeQuest Timing Analyzer。生成一个post-fit时序网表,通过表 10-1中的程序,读取SDC文件并更新时序网表来生成关于最新编译的报告。

表 10-1. 生成关于Latest Compilation的报告

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击所需报告的命令。例如:Report All Summaries。 |

输入: create_timing_netlist read_sdc filref.sdc update_timing_netlistreport_clocks create_timing_summary -setup create_timing_summary -hold create_timing_summary -recovery create_timing_summary -removal report_min_pulse_width -nworst 10 |

1 当双击其中一个报告命令时,Create Timing Netlist、Read SDC和Update Timing Netlist命令依次在Tasks面板中执行,自动生成时序网表。

时钟建立检查确保每个寄存器至寄存器的传输不违反SDC指定的时序约束。通过表 10-2中的程序,生成一个时钟建立总结,对设计中的所有时钟进行检查,来验证没有出现违规。

表 10-2. 生成时钟设置总结检查(Clock Setup Summary Check)

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击 Report Setup Summary。 |

输入:create_timing_summary –setup |

![]()

Summary (Setup)报告

1 clkx2时钟没有出现在Summary (Setup)报告中,这是因为clk和clkx2之间所有的时钟路径已经声明是伪路径。此外,fir_filter设计不包含任何寄存器到寄存器的路径,其中目的寄存器路径由clkx2来驱动。

Summary (Setup)报告中的Slack列表明clk能满足约束,并有11.588 ns的余量。End Point TNS列是指定时钟域中所有的总负裕量(TNS)的总和。使用这个值来测量指定时钟域中失败路径的总数。

生成Summary (Setup)报告后,通过表 2-21中的程序,在设计中生成一个时钟保持检查总结。

表 10-3. 生成Summary (Hold) Report

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Report Hold Summary。 |

输入:create_timing_summary –hold r |

![]()

图 16Summary (Hold)报告

Summary (Hold)报告表明clk时钟节点符合时序约束,并有0.661 ns的余量。在执行全编译之前,通过表 10-4中的程序指定所有的时序约束和例外。这样可以确保 Fitter优化设计中的关键路径。

您可以使用Report Unconstrained Paths命令来验证已经约束fir_filter设计中的所有路径。

表 10-4. 指定时序约束和例外

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 在Tasks面板中,双击Report Unconstrained Paths。 |

输入:report_ucp r |

![]()

图 17Unconstrained Paths总结报告

Unconstrained Paths总结报告表明有大量的未约束路径,并详细介绍了这些路径的类型。

要充分约束此设计,利用由TimeQuest Timing Analyzer所提供的整套SDC约束。要充分约束fir_filter设计,约束所有的输入和输出端口。使用Set Input Delay和Set Output Delay对话框,或set_input_delay和set_output_delay约束来指定输入和输出延迟值。

由于附加约束应用于设计,通过文本编辑器(例如:inout_delay.sdc)创建仅包含输入和输出约束的额外SDC。添加表 10-5所示的输入和输出延迟分配到"步骤8:保存约束到SDC文件"创建的新SDC中。

表 10-5. 输入和输出延迟分配

| The TimeQuest Timing Analyzer GUI |

The TimeQuest Timing Analyzer Console |

| 1.在Constraints菜单中,点击Set Input Delay。出现Set Input Delay对话框。 2.输入以下内容: Clock name: clk Delay value: 2 Targets: [get_ports {d[0] d[1] d[2] d[3] \ d[4] d[5] d[6] d[7] newt reset}] 3.在Constraints菜单中,点击Set Output Delay。出现Set Output Delay对话框。 4.输入以下内容: Clock name: clk Delay value: 1.5 Targets: [get_ports {yn_out[0] yn_out[1] \ yn_out[2] yn_out[3] yn_out[4] yn_out[5] \ yn_out[6] yn_out[7] yvalid follow}] |

要约束输入端口,输入: set_input_delay -clock clk 2 \ [get_ports {d* newt reset}] r 要约束输出端口,输入: set_output_delay -clock clk 1.5 \ [get_ports {yn_out* yvalid follow}] r |

在读取包含输入和输出延迟约束的SDC后,所有设计中的端口应该都加上了约束。

1 记住读取新的约束后更新时序网表。要了解更多信息,请参考"步骤5:更新时序网表(Timing Netlist)"。要验证所有设计中的端口都已经加上了约束,重新生成Unconstrained Paths Summary 报告。

![]()

图 18重新生成Unconstrained Paths Summary报告

结论

通过表 10-6中的程序,对设计的时钟或节点生成特定的时序检查报告。表 10-6中的程序生成一个报告,其中clk驱动目的寄存器,并且目的寄存器为acc:inst3|result,报告10条最差路径。

表 10-6. 生成Report Timing报告

| TimeQuest Timing Analyzer GUI |

TimeQuest Timing Analyzer Console |

| 1.在Tasks面板中,双击Report Timing。出现Report Timing 对话框。 2.输入以下内容: To Clock: clk To: acc:inst3|result* Report number of paths: 10 3.剩下其它的栏使用默认的设置。 |

输入: report_timing -to_clock clk -to / acc:inst3|result* -setup -npaths 10 |

图 2-10显示了Report Timing报告。

![]()

使用Tasks面板中的Report Top Failing Paths命令来生成一个报告,该报告详细介绍了设计中的最差的失败路径。

根据Quartus_II_TimeQuest说明书_CH.pdf修改而成,因原教程使用的工程quartus中lisence不支持器件。

结论

您创建新的约束或例外,基于新的约束或例外重新运行Quartus II Fitter来优化设计。设计上的多个迭代对于完成所需的结果是必要的。