MIPS指令 MIPS架构

华中科技大学 - 计算机组成原理

华中科技大学 - 计算机硬件系统设计

Microprocessor without Interlocked Pipleline Stages

无内部互锁流水级的微处理器

- 属于RISC

MIPS指令格式

R型指令

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

|---|---|---|---|---|---|

| 000000 | Rs | Rt | Rd | shamt | funct |

| 第一源操作数 | 第二源操作数 | 目标操作数,保存结果 | 在移位指令中使用 | 指定指令的具体功能 |

三寄存器R型指令

add

| 000000 | Rs | Rt | Rd | 00000 | 100000 |

|---|

sub

| 000000 | Rs | Rt | Rd | 00000 | 100010 |

|---|

and

| 000000 | Rs | Rt | Rd | 00000 | 100100 |

|---|

or

| 000000 | Rs | Rt | Rd | 00000 | 100101 |

|---|

xor

| 000000 | Rs | Rt | Rd | 00000 | 100110 |

|---|

两寄存器R型指令

sll(逻辑左移)

| 000000 | 00000 | Rt | Rd | 偏移量 | 000000 |

|---|

srl(逻辑右移)

| 000000 | 00000 | Rt | Rd | 偏移量 | 000010 |

|---|

sra(算术右移)

| 000000 | 00000 | Rt | Rd | 偏移量 | 000011 |

|---|

单寄存器R型指令

jr(寄存器跳转)

| 000000 | Rs | 00000 | 00000 | 00000 | 001000 |

|---|

R型指令中的无条件分支指令:jr,jalr

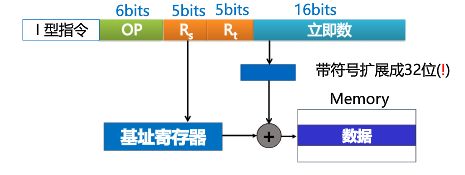

I型指令

| 6 bits | 5 bits | 5 bits | 16 bits |

|---|---|---|---|

| OP | Rs | Rt | |

| 标识操作功能 | 第1个源操作数 | 目的寄存器编号 | 第2个源操作数 |

双目运算、LOAD/STORE:Rs和立即数是源操作数,Rt为目标操作数

条件转移:Rs、Rt均为源操作数

面向运算的I型指令

addi

| 001000 | Rs | Rt | imm |

|---|

andi

| 001100 | Rs | Rt | imm |

|---|

ori

| 001101 | Rs | Rt | imm |

|---|

xori

| 001110 | Rs | Rt | imm |

|---|

addi的立即数扩展为符号扩展

(若为负数高16位补1)

其他三条进行0扩展

(高16位补0)

面向访存的I型指令

lw(从存储器读数据)

| 100011 | Rs | Rt | imm |

|---|

sw(把数据保存到存取器)

| 101011 | Rs | Rt | imm |

|---|

面向数位设置的I型指令

lui(把立即数加载到寄存器的高16位)

| 001111 | 00000 | Rt | imm |

|---|

面向条件转移的I型指令

beq(寄存器相等则转移)

| 000100 | Rs | Rt | imm |

|---|

bne(寄存器不相等则转移)

| 000101 | Rs | Rt | imm |

|---|

I型指令中的有条件分支指令:beq, bne, bgtz( > 0 ), bgez( >= 0 ),bltz( < 0 ), blez( <= 0 )

J型指令

| 6 bits | 26 bits |

|---|---|

| OP | 立即数 |

| 跳转目标地址的部分地址 |

j(无条件跳转)

| 000010 | address |

|---|

jal(调用与联接)

| 001100 | address |

|---|

类似于X86架构的CALL。jal要保存返回地址

J型指令的无条件分支指令:j, jal

MIPS寄存器

在R和I型指令格式中,寄存器操作数字段均为5位,可编号32个寄存器

| 寄存器名 | 寄存器编号 | 说明 |

|---|---|---|

| $s0 | 0 | 保存固定的常数0 |

| $at | 1 | 汇编器的临时变量 |

| $v0 - $v1 | 2 - 3 | 字函数调用返回结果 |

| $a0 - $a3 | 4 - 7 | 函数调用参数1-3 |

| $t0 - $t7 | 8 - 15 | 临时变量,函数调用时不需要保存和恢复 |

| $s0 - $s7 | 16 - 23 | 函数调用时需要保存和恢复的寄存器变量 |

| $t8 - $t9 | 24 - 25 | 临时变量,函数调用时不需要保存和恢复 |

| $k0 - $k1 | 26 -27 | 中断、异常处理程序使用 |

| $gp | 28 | 全局指针变量(Global Pointer) |

| $sp | 29 | 堆栈指针变量(Stack Pointer) |

| $fp | 30 | 帧指针变量(Frame Pointer) |

| $ra | 31 | 返回地址(Return Address) |

另外还有

- 32个32位单精度浮点寄存器f0 - f31

- 2个32位乘、商寄存器Hi和L0:运算乘法时分别存放64位乘积的高、低32位; 除法时分别存放余数和商

浮点寄存器和乘商寄存器没有编号,对程序员来说是透明的

MIPS寻址方式

MIPS32指令集中不单设寻址方式说明字段

- R型指令:由OP和funct字段共同隐含说明(R型指令字段全为0,需要结合funct字段表示)

- I、J型指令:由OP字段隐含

立即数寻址

immediate addressing

寄存器直接寻址

register addressing

add $t0,$s1,$s2 ;($t0 = $s1 + $s2)

基址寻址

使用通用寄存器作为基址寄存器,以立即数作为偏移量,立即数带符号扩展为32位,和基址寄存器的值一起得到主存地址

使用基址寻址的指令:lw, sw, lh, sh, lb, lbu等

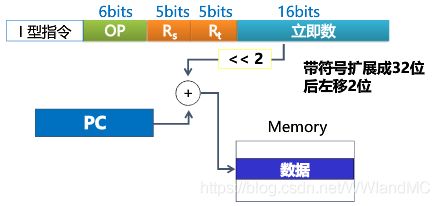

相对寻址

PC的值和偏移量相加得到主存地址,以立即数为偏移量。立即数带符号扩展为32位并左移2位再和PC的内容相加

PC的值会被修改为相加结果

使用相对寻址的指令:beq, bne

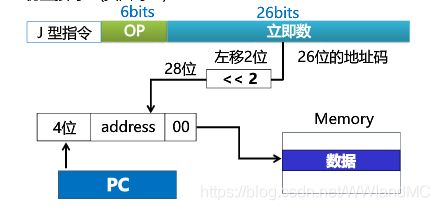

页面寻址

26位的地址码左移2位变为28位,作为地址的低28位,PC的值会被修改

高4位是PC改变后的值(取出指令后PC自动增加)

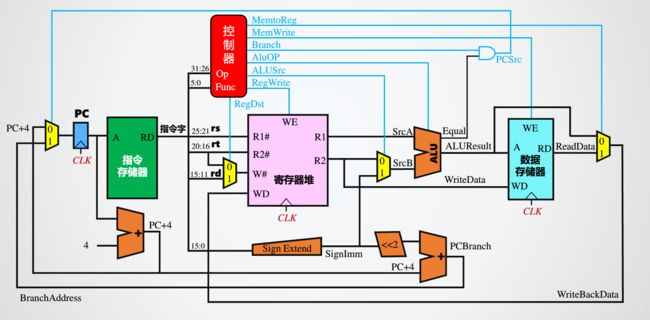

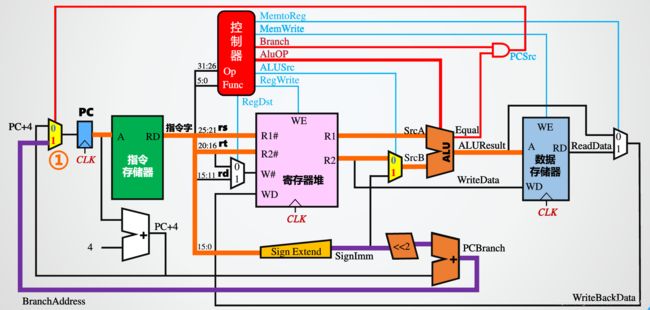

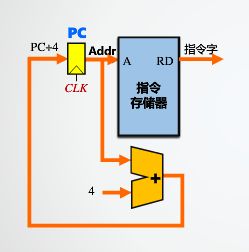

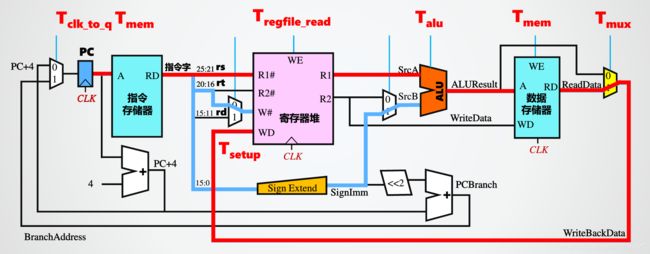

单周期MIPS架构

取指Dp

由于需要在一个周期内完成取指译码执行的过程,不设置AR,DR,IR。

取指令和取操作数要同时完成,为了避免访存冲突将程序和数据分开存放(哈佛结构):

- 指令Cache

- 数据Cache

ALU和PC累加器分开

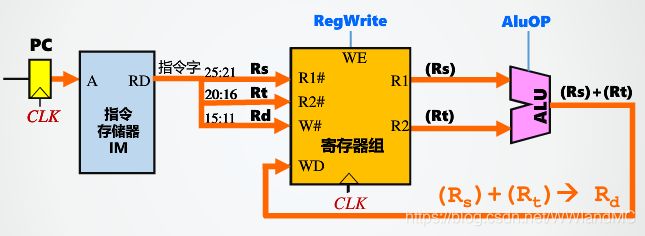

R型指令数据通路

- 以PC的内容访问IM,解析指令字段,分出3个寄存器编号

- 以寄存器编号访问寄存器堆

- 输出两路寄存器值,根据AluOP信号运算

- 当时钟到来,给出RegWrite,将结果写入寄存器堆

寄存器堆要支持两路读和一路写

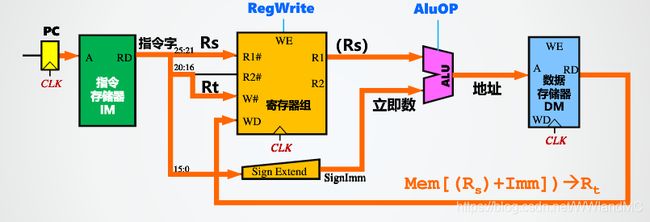

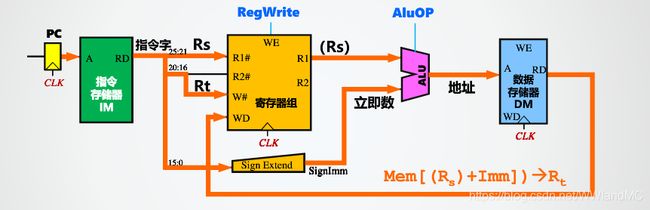

I型指令数据通路

- 以PC的内容访问IM,解析指令字段,分出2个寄存器编号和立即数字段

- 以寄存器编号访问寄存器堆

- 立即数字段进行符号扩展单元,扩展为32位

- 输出一路寄存器值,和立即数相加得到DM地址

- 经过一个存储器延迟,数据到达WD端

- 时钟到来写入寄存器堆

单周期MIPS数据通路

beq数据通路的建立

J型指令的数据通路建立

需要增加JUMP控制信号,PC输入增加一个跳转地址

单周期MIPS控制器

单周期架构下,无时序逻辑

| 输入 | 输出 |

|---|---|

| OP + funct | 多路选择器选择信号 |

| 寄存器写使能信号 | |

| 内存访问控制信号 | |

| 运算器控制信号 | |

| 指令译码信号 |

单周期MIPS关键路径

lw的最长路径

时钟周期 = Tclk_to_Q + Tmem + Tregfile_read + Talu + Tmem + Tmux + Tsetup

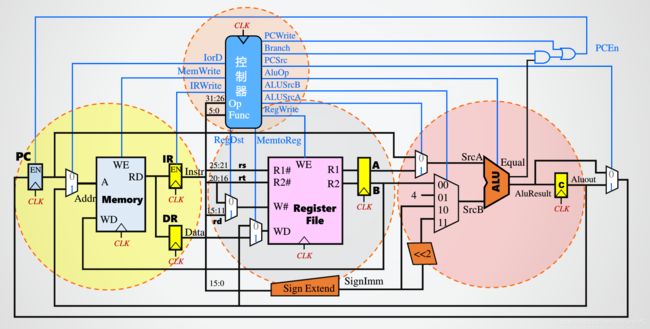

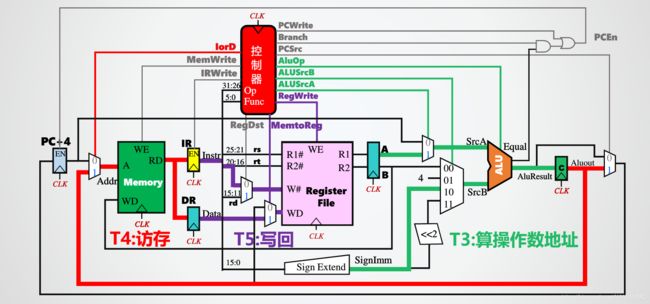

多周期MIPS架构

不区分指令和数据存储器(冯诺依曼结构),功能部件分时使用

时钟周期变小,传输通路变短

功能部件输出端增加寄存器锁存数据

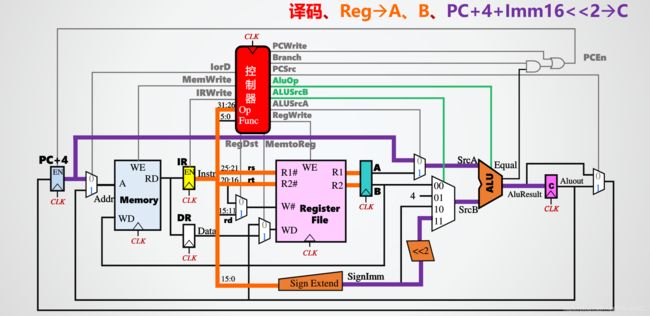

多周期MIPS CPU数据通路

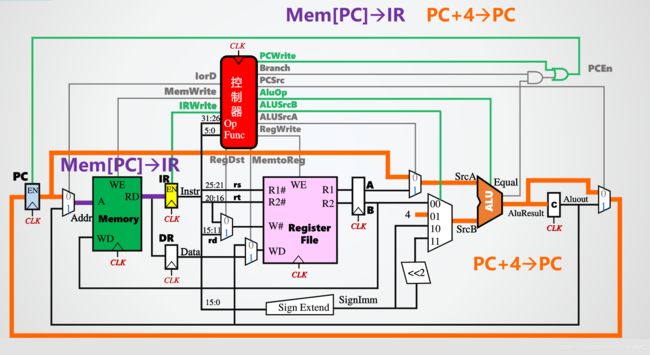

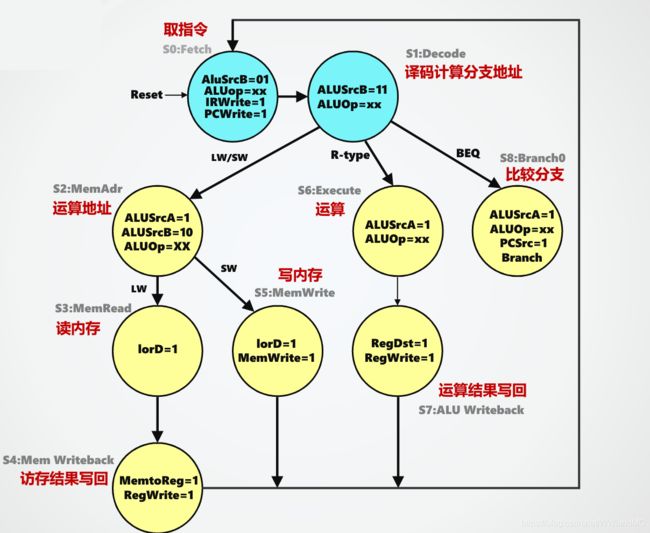

取指令T1

- PC的内容传输到ALU的输入端和

- ALUSrcB信号选择4传输到ALU的输入端

- AluOP信号选择运算方式

- 时钟到来,在PCWrite信号的配合下结果送回PC

根据PC的内容从主存取指令

- 给出IRWrite信号,时钟到来时PC值写入IR锁存,同时PC原有的值更新为PC+4

取指令T2

- 将IR的内容送入控制器产生控制信号

- 计算条件分支转移的地址(图紫色部分)

时钟到来,取出的数据锁存在AB

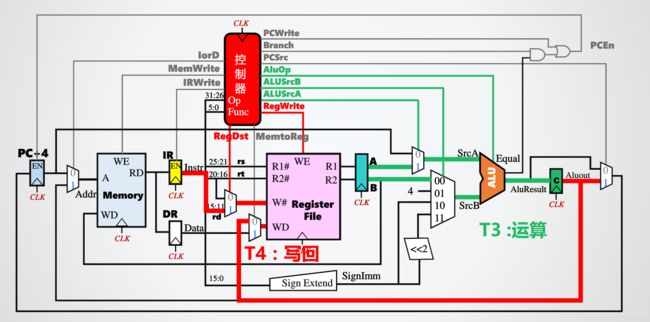

R型指令执行T3-T4

- 给出AluOP和ALUSrcA、ALUSrcB信号,完成信号

- 时钟到来C更新

- C的内容输出,在RegDst和RegWrite信号配合下,写回寄存器堆

lw执行T3-T5

4. A和立即数相加计算操作数地址,时钟到来结果锁存在C

5. 将C的内容传输到主存,时钟到来数据锁存在DR

6. DR的内容写入寄存器堆(IR给出目标寄存器编号)

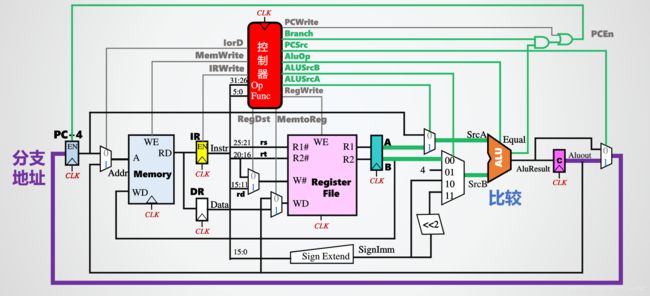

beq执行T3

- AB内容传输到ALU的输入端,进行比较,相等在给出equal信号,与branch信号与后输入到PC作为写使能

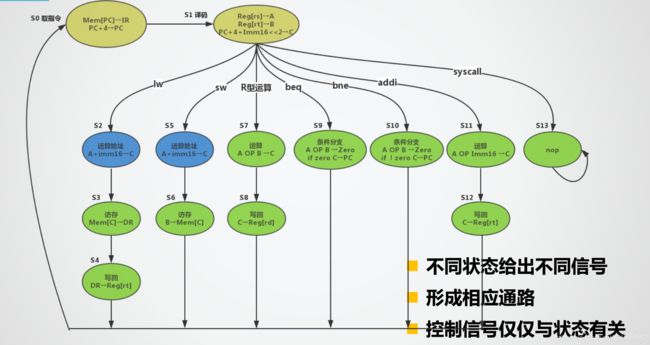

多周期状态转换图

多周期MIPS CPU控制器

| 输入 | 输出 |

|---|---|

| OP + funct | 多路选择器选择信号 |

| 时钟信号 | 寄存器写使能信号 |

| 复位信号 | 内存访问控制信号 |

| 运算器控制信号 | |

| 指令译码信号 |