SpaceCube v3.0下一代高性能处理器平台架构

大致翻译论文:《SpaceCube v3.0 NASA Next-Generation High-Performance Processor for Science Application》

英语小白,自己学习,大神勿喷!

摘要

航空电子面临许多重大的挑战,在危险的环境中需要操作方便,需要满足高性能的处理需求同时需要满足尺寸、重量和功耗的限制。为了驱动将来空间处理系统的革命,板级系统需要更灵活、低成本、稳定。为了给各种任务和器件提供一个稳定的解决方案,美国航天宇航局戈达德宇宙飞行中心的科学数据处理部门,首创了一种混合的处理方案,将商用器件和辐射加固方法结合,实现一种新的能够发挥CPUs、DPSs和FPGA的最佳性能的架构。这种混合方法是通过SpaceCube系列处理器卡来实现的,SpaceCube家族的最新成员,SpaceCube v3.0,将作为未来任务的下一个进化步骤,允许设计和软件的原型,并提供一个灵活、成熟的体系结构,该体系结构在发布时也准备采用经过辐射加固的高性能航天计算(HPSC)芯片。本文介绍了SpaceCube v3.0 SpaceVPX Lite (VITA 78.1) 3U-220mm形状因子处理器卡的设计方法、分析和性能。

1 引言

由于小型卫星社区的贡献,获得诸如地球观测图象等空间资源的机会迅速增加,如今,NASA面临的挑战是实现一个“平衡计划”,管理不同贸易空间之间的需求和资金,比如;大小不同的任务、延申操作和新的任务、传统方法和新方法。然而,即使有了这些困难的程序性决策,强调交叉技术,可以给所有主题和领域提供好处。航空电子技术是其中的交叉技术之一,是航空航天中关键的电子技术。在下一代科学和国防任务中,航天器、航空电子设备和科学数据处理系统必须提供先进的处理能力,以支持各种计算密集型任务,包括快速处理来自传感器的大容量数据(例如:雷达、高光谱相机),为自主行动的单个或星座航天器计算解决方案,并为实时/近实时数据产品生成和压缩嵌入复杂的算法。

对科学的重大需求,最近在2018年国家科学院太空研究委员会地球观测十年调查中得到了体现,这项调查强调新的平台应当支持新的传感器实现更高的分辨率,更短的时间间隔,提高精度。“所有的这些关键要素时用于下载和处理不断增长的数据流的基础架构” 下一代国防对机载计算的需求最近在Blackjack“Pit Boss”边缘处理节点[5]的复杂程序目标中得到了证明。”Pit Boss”强调复杂的人工智能算法,激增的卫星星座可以自主地执行任务、收集信息、处理、利用和传播多传感器数据到不同的全球位置。

在科学和国防方面,美国国家航空航天局(NASA)和美国空军研究所(AFRL)共同认识到,提高航天飞行计算能力是太空任务的天然“技术倍增器”。 通过机构间的合作,AFRL和NASA对计算机架构进行了广泛的研究,以满足未来任务的飞行计算需求。如前所述,下一代任务将要求小型卫星提供更有能力的处理解决方案,同时也要满足成本和可靠性的限制。这个考虑将在文献[7]中详细描述。但总而言之,空间系统必须应对各种挑战,包括危险空间环境中的操作弹性,以及满足应用程序性能需求,同时要满足尺寸、重量和功率(交换)要求。因此,为了推动未来空间处理的革命,机载系统需要更灵活、更经济、更健壮。

为了解决平台的局限性,开发了SpaceCube系列处理器卡,以便在功率、大小、可靠性、成本和数据处理能力(用于航天器、航空电子设备和仪器处理)之间提供适当的系统平衡。SpaceCube v2.0(文献[8])处理器系统较传统的抗辐射(rad-hard)飞行处理器系统有显著改进; 然而,新兴科学任务的处理需求超过了它的能力。传感器能力的增加加上数据下行限制将不断推动这些任务需要更高的处理能力。这种对更多星载处理能力的渴望导致了SpaceCube v3.0的发展,与其他飞行单板计算机相比,它表现出10-100倍或更多的令人印象深刻的性能提升。SpaceCube v3.0处理器卡和盒级架构是一种灵活的、模块化的、兼容的解决方案,适用于不同大小的航天器。

本文介绍了SpaceCube v3.0 (SCv3.0)处理器卡的设计方法和主要特点。论文其余部分的组织如下,在第二部分中,我们将介绍启用程序的背景以及与SCv3.0开发相关的关键概念。第三部分描述了整个SpaceCube家族的设计方法;在第四部分,我们介绍了处理器卡的硬件架构设计。第五部分介绍了机械设计,在第六节中,我们描述了散热方案。最后,第七部分是结束语和未来计划。

2 背景

本节简要介绍可用的计算性能,此外,SpaceCube相关的简要描述,以及即将推出的HPSC处理器芯片[9]的概述,这是与SpaceCube的设计开发相辅相成的。航空计算性能就处理能力而言,传统的抗辐射处理器通常比商用设备落后几代。一个空间级处理器的研究(文献[10])提供了不同设备之间的性能对比,并强调了几个最先进的抗辐射处理器和SpaceCube v2.0中特色的Virtex-5之间的性能差异。图1展示了这些结果,并在理论上包括了SpaceCube v3.0中比较的新设备的性能。图1显示的这些设备的每秒千兆操作(GOPS)是对数级的,Xilinx设备在SpaceCube系列的显著的表现得比最先进的抗辐射处理器要好得多。

图1:空间设备每秒千兆操作的对数尺度比较

UltraScale和MPSoC是基于[10]现有数据的估计,新的指标正在进行中,但目前还没有。高性能航天计算(HPSC)由于需要一种比BAE RAD750具有更高的计算性能和功率效率的新型抗辐射航天飞行计算系统,AFRL和NASA早在2013年4月就建立了联合合作关系。这一合作伙伴共同发布了一份名为《下一代空间处理器(NGSP)分析程序》的广泛的机构公告(BAA),该公告将征集承包商和供应商为高性能航天计算(HPSC)项目[6]提出一种用于多核飞行的、抗辐射的通用计算机的架构设计。自制定以来,HPSC项目合同被授予波音公司,在2021年4月提供这些抗辐射的多核计算处理器或芯片。SpaceCube家族的最新成员,SpaceCube v3.0将作为即将到来的任务的下一个进化步骤,允许设计和软件的原型,并提供一个灵活和成熟的体系结构,准备在HPSC发布时采用它。这项工作是互补的,因为SCv3.0处理器卡中包含的MPSoC(多处理器系统上的芯片)以四核ARM Cortex-A53为核心,他将会提供和HPSC相似的计算性能,但是时针对于那些短期内需要更多性能或者需要更低成本的任务。

2.1 SpaceCube 传统

SpaceCube是NASA戈达德太空飞行中心(GSFC)开发的基于现场可编程门阵列(FPGA)的机载科学数据处理系统。SpaceCube项目的目标是在降低相对功耗和成本的同时,大幅提高机载计算能力。SpaceCube的概念始于2006年,最初由内部研发(IRAD)项目资助。通过一些原型演示和提案努力,SpaceCube计划是得到了学技术办公室资助,为各种应用开发处理器提供解决方案。到目前为止,不同版本的SpaceCube已经在许多成功的任务中飞行,包括HST-SM4、SMART、MISSE-7/8、STP-H4/H5、RRM3,以及最近的STP-H6/CIB和NavCube (STP-H6/XCOM)。最初从2006年到2009年开发的SpaceCube版本被称为SpaceCube v1.0(文献[11]。从那时起,SpaceCube的设计经历了更多的迭代开发和部署。SpaceCube v2.0(文献[8])已经商业化,可以作为一种现成的太空解决方案从Genesis工程解决方案购买,称为GEN6000,SpaceCube v2.0也适用于文献[12]中描述的其他应用和任务。最后,SpaceCube v2.0的立方体卫星形状因子版本被开发出来,命名为SpaceCube v2.0 Mini,它在STP-H5上飞行,并在[13]中详细描述。

3 SpaceCube方法

为了给各种任务和器件提供一个稳定的解决方案,美国航天宇航局戈达德宇宙飞行中心的科学数据处理部门,首创了一种混合的处理方案,将商用器件和辐射加固方法结合,实现一种新的能够发挥CPUs、DPSs和FPGA的最佳性能的架构。这种混合方法是通过SpaceCube数据处理器家族实现的,如前所述,该家族已经有了很长的传承。除了混合架构设计外,SpaceCube方法还包含了在卡片和盒子设计级别上的可靠性和可配置性的几个设计原则。

3.1 可靠的监控

SpaceCube强调与Xilinx设备最大的兼容性;然而,自从这些器件越来越容易受辐射的影响,SpaceCube整合了一个更强的抗辐射装置作为监视器。SpaceCube v1.0和SpaceCube v2.0采用了Cobham Aeroflex UT6325抗辐射FPGA,而SpaceCube v3.0则使用了Microsemi - RTAX FPGA。这些可靠的监控器充当Xilinx配置的健康监视器,可以从内存中触发回滚或重新配置。为了减轻配置单事件扰动(SEUs),监视器或Xilinx FPGAs本身可以执行配置监视和擦除。根据监视器的配置,刷洗以可编程的速率(盲刷洗)或在检测到错误(回读)时发生。该体系结构提供了一种可靠的外部控制Xilinx配置数据的方法。

3.2 质量部分选择

正如美国国家航空航天局的小型卫星可靠性倡议[14]所指出的,将商用部件纳入飞行航空电子系统对设计者来说可能是一个挑战,因为虽然商用和汽车级(强于工业级)部件的使用降低了成本,但许多现成的商用部件可能没有任何筛查或辐射测试的传统。由于新板级设计师和供应商的增加, 这需要满足小型卫星空间生态系统中不断增长的需求, 许多商业上可用的设计是在没有考虑辐射或部件可靠性的情况下开发的, 经进一步分析,这可能不适用于高价值科学任务。航天飞机的方法首先是在可行的地方选择符合美国宇航局标准的飞行部件。然而,当需要更新的部件或组件来推动前沿开发时,就会包括它们,通过严格的内部NASA GSFC部件控制板进行筛选和选择,降低确定和设计系统的风险。部件控制委员会的专家协助航天飞机开发小组进行部件鉴定程序,并根据任务需要进行选择性辐射测试。

3.3 模块化

最初的SpaceCube v1.0设计基于自定义堆叠连接器架构。虽然有一些优势,SpaceCube v1.0中使用的自定义叠加连接器方法引入了更多的信号不连续,影响信号的完整性,:而且卡之间只支持较少的点对点连接,因为所有在卡片之间路由的大头针必须包含在单个连接器的大头针计数中。SpaceCube v2.0设计聚合在支持行业标准背板风格的接口上,与其他系统和商业设计提供更多兼容性,背板设计可以很容易地扩展到其他额外的卡,并且不像原来的SpaceCube v1.0堆叠架构,卡可以很容易地进出系统。

3.4 Xilinx设备及智能系统设计

SpaceCube的关键基础时可重构的Xilinx的FPGA,SpaceCube方法的原理是使用最新的耐辐射(即易受辐射引起的故障影响,但不受辐射引起的破坏性故障影响)处理元素,以获得它们在性能、交换和可购性方面的优势。然后,为了解决可靠性和辐射方面的问题,接受这些设备将会出现的故障,并通过系统设计策略来减轻其后果。生成的平台本质上是可重构的,为应用程序设计人员提供了一个灵活的系统,支持快速开发并可用于多个任务。这种可重新配置的能力允许SpaceCube改变其功能,并支持不同任务阶段的不同角色。

3.5 自定义任务特定的IO卡支持

SpaceCube箱式处理系统通常支持由电源卡、处理器卡和带有附加卡槽的背板组成的基本,配置。为了避免昂贵的一次性航空电子系统,SpaceCube方法重用了基础系统的硬件架构,并整合了一个任务唯一的IO接口卡。SpaceCube是可重构的,因此硬件设计通过重新配置处理器卡上的底层可编程元件,使其与应用独特的IO卡相连接,以适应新的系统需求。在[12]中描述了用于SpaceCube v2.0系统的这种方法的示例。

4 硬件体系结构

SCv3.0的设计独特地引入了高容量FPGA、高性能SoC(系统芯片)和可靠的FPGA监控器的组合。本节介绍SCv3.0处理器卡的体系结构和关键特性。

4.1 高层次设计

SpaceCube v3.0是SpaceVPX Lite (VITA 78.1) [15] 3U-220mm外形因素卡,具有两项核心技术,将Xilinx Kintex UltraScale (20nm FPGA)与Xilinx Zynq MPSoC(四核64位ARM Cortex-A53、双核Cortex-R5、16nm FinFET+ FPGA)相结合,提供强大的固定逻辑处理器和大量可重构逻辑FPGA资源。Kintex UltraScale FPGA和Zynq MPSoC是可在飞行中重新配置的,允许极端的适应性,以满足动态任务目标,而抗辐射监控器提供可靠的操作和监控。主要组件的高级框图如图2所示

图2:SpaceCube v3.0处理器卡高层框图

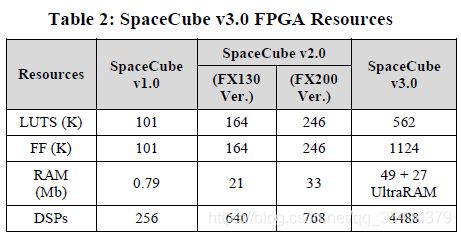

SCv3.0的体系结构在将算法移植和映射到设计上是通用的,因为它们既可以受益于Kintex超尺度FPGA的可重构结构,也可以受益于Zynq MPSoC中的高性能ARM处理器。如在文献[16]所示,混合架构有利于算法加速,因为算法的顺序流或控制流部分可以在四核处理器上快速有效地实现,而其他面向数据流的算法是高度并行的,或由计算量很大的迭代操作组成,可以在Kintex UltraScale和Zynq MPSoC的FPGA结构中加速。与SpaceCube v2.0 (IBM PowerPC440)中的嵌入式处理器相比,Zynq MPSoC多核处理器(ARM Cortex-A53)提供了巨大的速度提升。核心基准是由由嵌入式微处理器基准测试协会开发的性能测试基准,旨在取代过时的Dhrystone基准。表1显示SpaceCube处理器使用的处理器架构的CoreMark分数,并进一步强调从SpaceCube v2.0到SpaceCube v3.0的显著计算裕度增长。此外,与Virtex-5 FPGA相比,Kintex UltraScale FPGA设备在性能和FPGA资源方面都有了显著的提升。表2显示可用于整个SpaceCube处理器代的FPGA逻辑资源的比较

SCv3.0处理器卡具有一个扩展卡选项/插件模块连接器,允许紧密耦合的、任务唯一的卡被开发并直接连接到处理器卡,如果任务无法支持航空电子设备盒的配置,该功能允许任务开发人员根据需要扩展系统,而不必提供或开发单独的I/O卡。这个扩展卡接口利用了VITA 57.4 FPGA夹层卡Plus (FMC+)[17]行业标准,该标准为测试和开发提供了灵活性,现有的商用卡已经符合该标准。FMC+与标准FMC保持向后兼容性,然而,它也突破了大量的千兆收发(MGT)接口,这些接口使用JESD204B标准,可以与多个千兆样本ADC/DACs连接。这些ADC/DACs对于实现激光雷达、雷达、通信和其他应用程序至关重要。然而,SpaceCube v3.0扩展卡并不局限于FMC+尺寸,如果需要,还可以接受更大的扩展卡。合并的任务扩展卡允许SCv3.0处理器卡作为一个强大的仪器处理器来完成许多角色,因此ADC转换器、DAC转换器、千兆以太网、1553、额外的协处理器等等都可以直接连接到该卡上。

对于内存存储资源,这三个fpga都有一个用于非易失性存储的附加闪存。与防辐射监视器(RHM)相连的NAND闪存存储配置文件,使防辐射监视器能够配置和清除Kintex UltraScale FPGA。每个连接到Kintex UltraScale FPGA和MPSoC的NAND闪存存储软件应用程序、FPGA配置文件和其他应用程序数据。然而,Kintex UltraScale NAND闪存的设计目的是优化写吞吐量,由于用户可以将传感器和高通量仪器集成到该设备。Kintex UltraScale FPGA和Zynq MPSoC都附加了DDR3 (x72位宽,533 MHz) SDRAM易失性存储器,为高性能处理提供了重要的带宽。Kintex UltraScale附有两个DDR3,Zynq MPSoc的ARM侧附有一个DDR3,所选的存储器有一个额外的字节来支持EDAC(错误检测和校正),以缓解空间操作的辐射。这些内存可以用于操作系统存储,还可以通过缓冲图像、仪器数据和中间产品来支持实时应用程序数据处理。Xilinx FPGAs是低成本、耐辐射的元件; 然而,剩下的系统是用美国国家航空航天局合格的飞行部件设计的。然而,剩下的系统是用美国国家航空航天局合格的飞行部件设计的。如第3节所述,为了监视Xilinx设备,体系结构包括一个抗辐射微半RTAX FPGA来减轻整个系统的辐射影响。抗辐射监控器通过多种方法提供辐射环缓解和系统监控。监视器可以配置Kintex UltraScale FPGA多达64个独特的配置文件和擦洗配置内存,以纠正任何错误。这些配置文件也可以通过地面命令更新到监视器。它还使用错误检测和冗余副本来减轻存储在外部非易失性内存中的Xilinx配置文件的辐射扰动。:此外,它还使用看门狗计时器监视Zynq MPSoC处理器、Kintex UltraScale FPGA和扩展卡上的任何协处理器的健康状况。

该系统经过精心设计,使抗辐射监控器先通电,然后控制众多的Xilinx FPGA电压轨的电源顺序。:此外,RHM监控板上的每个电压轨和关键电力轨上的电流,以帮助故障检测。这使得Xilinx FPGAs可以在本地进行电力循环,以清除任何辐射引起的故障。由于这一功能,即使在Xilinx FPGAs处于无电源状态时,防辐射监视器也可以响应地面命令,并且不需要对整个卡进行电源循环。防辐射监控器也有一个空间线(SPW)路由器,它通过背板和前面板连接器从外部连接,并连接到Kintex UltraScale和Zynq MPSoC。该功能允许航天器直接与防辐射监控器和Xilinx FPGAs通过相同的接口进行通信。

SpaceCube v3.0在管理数量、路由和太空飞行性能方面有着显著的表现。无论是Kintex UltraScale FPGA还是Zynq MPSoC,都有几十个千兆收发器(MGT)在Zynq MPSoC、Kintex UltraScale FPGA、背板连接器和扩展卡连接器之间相互连接。这些收发器允许在短时间内交换大量数据,同时最小化用于路由资源的印刷电路板(PCB)区域。由于辐射效应的缓解需要Zynq MPSoC,SCv3.0处理器卡的预期系统架构部署是将高速传感器或仪器接口集成到Kintex UltraScale,在通过这个高带宽(8x MGT通道)接口将数据传输到Zynq之前,它将执行重要的预处理,以便进行更高阶的处理或附加的流水线算法阶段。此外,SCv3.0处理器卡还包括一项创新技术,允许MGT差分对可选路由到不同的目的地。

VPX背板连接器为高密度连接器,提供3.3V、5V、+/-12V电源轨,背板连接器I/O包括千兆收发接口、LVDS和GPIO。VPX连接器允许比典型的飞行连接器更快的信号速率。最后,SpaceCube v3.0处理器卡还具有一个37针的Nano连接器、一个21针的Nano连接器和一个提供调试和飞行互连的85针的Nano连接器。图3中显示了主互连的高级视图

4.2 HPSC集成

如第二部分所述,由GSFC、AFRL和JPL联合开发的HPSC rad-hard-by-design manycore处理器是SpaceCube v3.0处理器卡的一个变体,在设计中取代Zynq MPSoC。为了更直接地集成HPSC和SpaceCube v3.0,当chiplets可用时,一个计划在扩展槽中的FMC+卡将被开发出来,如图2所示。

4.3 器件选择

如前所述,SCv3.0处理器卡具有两个复杂的Xilinx设备,即Kintex UltraScale和Zynq MPSoC。根据SpaceCubeX项目[18]的结果,SpaceCube团队在最终确定这些设备的选择之前进行了一次彻底的设计交易。之所以选择Kintex UltraScale,主要是因为Xilinx致力于将其设计的第一个20nm FPGA产品用于空间应用,该产品使用XQRKU60器件。这一决定与[19]和[20]对该设备的几次辐射测试提供的令人信服的结果相一致,对于第二个设备,之所以选择Zynq MPSoC,是因为Xilinx最初建议将ZU19EG作为[21]中的空间级设备进行支持,然而,[22]、[23]等辐射测试报告显示该设备存在单事件闭锁,进一步的细节不能透露;有人提出了一些缓解方案,其中一些已经被纳入到设计中,以允许MPSoC能够在某些用例中进行空间操作。此外,从NASA的战略角度来看,围绕ARM Cortex-A53进行设计的经验教训将有益于未来的HPSC。

5 结构设计

机械设计是使高性能处理系统能够在空间环境中运行的系统设计的一个关键方面。SpaceCube系统使用先进的设备并施加网格阵列密度,这在为航天应用获得合适的机械和包装设计的过程中提出了各种挑战。卡模块(图4)安装到插件式底盘上,可容纳220mm长的卡,符合space VPX标准中的大多数准则。卡模块配备了坚固的,固定的硬件安装在前面板。所述专用硬件提供了插入和提取底盘组件的双重功能。该设计适应了几个卡保持器的使用:那些直接安装到模块(卡阀或楔形锁)和那些直接安装到底盘,如楔形保持器)。卡的螺距是可配置的,根据应用需要的夹层卡在模块的次要方面,并根据电子器件的功耗。没有夹层的基线设计符合SpaceVPX Lite标准中主要侧固定器的1.2英寸间距选项。较高的耗散选项,包括夹层卡有1.5英寸的间距。

机械框架和前面板结构使SpaceCube v3.0符合行业领先的MIL-STD规范和NASA指南,包括GSFC-STD-7000,用于正弦振动、随机振动、准静态、冲击、热真空和热循环。分析成功地验证了该模块能够通过14.1 GRMS 3-sigma和50g,该框架采用紧固结构制成的耐用数控加工6061-T6铝。所有的紧固件都是不锈钢的,所有的螺纹孔都有自锁,不锈钢插入物能够承受剧烈的振动、冲击和多次插入/提取循环。该设计采用多种热设计方案来散热。

6 散热设计

这种传导冷却,电子封装装配设计提供了一个可靠的和轻量级的处理器系统,以满足严格的重量要求,并在恶劣,崎岖和有限的环境中执行在太空,军事和航空应用。为了达到工艺性能、PWB布局IPC-6012DS 3/A级要求、高密度PWB上组件的装配和环境性能目标之间的最佳平衡,进行了多项热、结构和热机械分析和贸易研究。主要的驱动程序是热设计实现。多功能加劲肋框架是解决热、结构设计问题的机构。:与其它热设计特性一起,它作为一种有效的无源热设计解决方案和从PWB到卡扣的主要热通道。对于典型的用例,SCv3.0处理器卡的功耗范围为22.6到45.8 W,根据50W最坏情况设计的分析表明,使用热设计解决方案可以使所有组装的组件满足额定结温。假设卡模块安装在标准的铝电子机箱中,只控制55C的底座,则进行分析,如图5所示。

7 本文小结

SpaceCube v3.0处理器卡是太空飞行计算能力的进化进步,这种新颖的设计集成了两个复杂的、高性能的Xilinx设备和一个抗辐射监视器,以提供卓越的性能和可靠性。本设计遵循SpaceCube设计方法,充分利用了SpaceCube v2.0的多年开发经验。因此,这种新的处理器卡将为科学和国防任务中的下一代需求提供一个处理解决方案。最后,经验教训和设计实现经验可以用于在未来的设计迭代中合并HPSC片段,或者作为一个独立的扩展卡。

8 未来规划

SpaceCube v3.0处理器卡原型将于2019年10月面世。此外,这个设计已经被用于构SpaceCube v3.0迷你处理器卡,它将SCv3.0功能的一个子集转移到一个1U立方体的形状因子卡上。