【操作系统】

文章目录

- 1. CPU

- 2. 中断

1. CPU

CPU(Central Processing Unit)中央处理器,是计算机的运算核心和控制核心。

【CPU 组成部件】

CPU 由控制部件、运算器(ALU)、高速缓冲存储器(Cache)、状态总线(Bus)组成。CPU 和 内部存储器(Memory)、输入/输出(I/O)设备 合称计算机三大核心部件。

- 控制部件(Control unit):主要是负责对指令译码,并且发出为完成每条指令所要执行的各个操作的控制信号。控制器本身不执行程序命令,只是指挥系统其他部分执行。

- 运算器 / 算术逻辑运算单元(ALU,Arithmetic Logic Unit):执行所有定点或浮点算术运算、逻辑运算、移位操作,地址运算和转换。

- 寄存器:寄存器是位于 CPU 内部的特殊存储单元。存储在寄存器的数据的存取比存储在其它内存单元(如 RAM、ROM)的数据的存取要快。寄存器部件包括通用寄存器、专用寄存器和控制寄存器。通用寄存器又可分定点数和浮点数两类,它们用来保存指令执行过程中临时存放的寄存器操作数和中间(或最终)的操作结果。

【CPU 工作过程】

CPU 的基本工作是执行存储的指令序列,即程序。程序的执行过程实际上是不断地取出指令、分析指令、执行指令的过程。

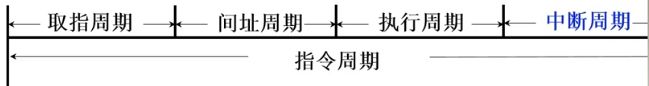

在取指周期后,需要判断是否有间址周期,如果没有就进入到了执行周期,在执行周期过程中,需要判断有没有中断程序,如果有,就响应中断:保存断点,生成中断服务程序入口,硬件关断点;如果没有,就进入下一个取指周期。

【各种周期的含义】

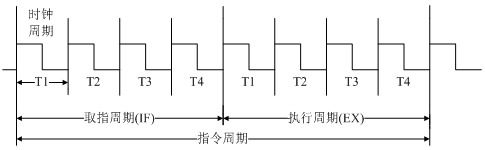

1. 指令周期:CPU 每取出并执行一条指令所需的全部时间,即 CPU 完成一条指令的时间。指令周期的长短与指令的复杂程度有关。一条完整的指令包括 取指周期、间址周期、执行周期、中断周期。

2. 机器周期(CPU 周期):CPU 访问一次内存所花的时间较长,因此 CPU 周期定义为 从内存读取一条指令字的最短时间。

3. 时钟周期:通常称为节拍脉冲或 T 周期。时钟周期是处理操作的最基本时间单位,由机器的主频决定。

4. 周期之间的关系:

- 一个指令周期 = 若干个 CPU 周期

- 一个 CPU 周期 = 若干个时钟周期

采用定长CPU周期的指令周期示意图:

任何一条指令,它的指令周期至少需要两个 CPU 周期,而复杂指令的指令周期则需要更多的 CPU 周期。这是因为,一条指令的取出阶段需要一个 CPU 周期时间,执行阶段也需要至少一个 CPU 周期时间。

参考:CPU的工作过程

【操作系统将指令交给 CPU 的执行过程】

CPU 执行指令的 5 个阶段:取指令(IF),指令译码(ID),执行指令(EX),访存取数(MEM),结果写回(WB)。

- 取指令(Instruction Fetch,IF):CPU 根据程序计数器 PC 中的值从主存中读取指令,送到指令寄存器,同时形成后继指令的地址(PC 根据指令字长度自动递增)。

- 指令译码(Instruction Decode,ID):将指令寄存器中的指令操作码取出后进行译码,分析指令性质,识别区分出不同的指令类别以及各种获取操作数的方法。

- 执行指令(Execute,EX):完成指令所规定的各种操作,具体实现指令的功能。

- 访存取数(Memory,MEM):根据指令需要,有可能要访问主存读取操作数,此时会根据指令地址码,得到操作数在主存中的地址,并从主存中读取该操作数用于运算。

- 结果写回(Write Back,WB):把执行指令阶段的运行结果数据“写回”到某种存储介质中,比如 CPU 的内部寄存器或主存中。

补充:指令周期可以分为取指周期、间址周期、执行周期、中断周期。其中间址周期和中断周期不一定有。

间址周期:当遇到间接寻址的指令时,由于指令字中只给出操作数有效地址的地址,因此,为了取出操作数,需先访问一次存储器,取出有效地址,然后再访问存储器,取出操作数。间址周期是取出操作数的有效地址,而执行周期是取出操作数,并执行指令。

中断周期:当 CPU 采用中断方式实现主机与 I/O 交换信息时,CPU 在每条指令执行阶段结束前, 都要发中断查询信号以检测是否有中断请求。如果有请求,CPU 就要进入中断响应阶段,又称中断周期。在这一阶段,CPU 必须将程序断点保存到存储器中。

【CPU 指令集】

指令集(指令系统)是 CPU 中用于计算和控制计算机系统的一套指令的集合,可以分为复杂指令集和精简指令集两部分。指令系统的设计和机器的硬件结构有关。。

常见指令集有:

- Intel 的 x86 系列,SSE 系列

- AMD 的 x86,x86-64,3D-Now!(主要用于 3D 游戏),3D-Now!+

目前通用 PC 都是 x86 架构的,其基本指令集一样,但是扩展指令集可能不同(比如 AMD 和 Intel 两家)。还有些专用 CPU 的基本指令集也和通用 PC 的 CPU 指令集不一样。

2. 中断

引入中断机制,可以实现多道程序的并发执行,提高了系统资源的利用率。中断是多程序并发执行的前提条件。

中断是 CPU 对系统发生的某事件做出的一种反应。CPU 会暂停正在执行的程序,保存现场后去执行相应的处理程序,处理完该事件后再返回中断处继续执行原来的程序。

操作系统其实是“中断驱动”的,发生中断时,CPU 从用户态进入核心态,使操作系统获得计算机的控制权。另外,用户态到核心态的转换是通过中断机制实现的,且中断是唯一途径。而核心态到用户态的切换是通过执行一个特权指令,将程序状态字(PSW)标志位设置未用户态。

中断分类:

- 外中断(中断):由 CPU 外部事件引起,比如 I/O 中断(IO设备处理已完成,希望处理机能向IO设备发送下一个请求)、时钟中断(固定时间片已到)。

- 内中断(异常/陷入):由 CPU 内部事件引起,比如程序出错,地址越界、浮点溢出。外中断和内中断的区别就是信号的来源。

- 系统调用:用户在程序中调用操作系统所提供的一些子功能。

中断处理方式: 中断处理 = 中断响应(硬件实施) + 中断处理(软件实施)

- 屏蔽中断:当处理机正在处理一个中断时,将屏蔽掉所有的中断,即处理机对任何新到的中断请求,都暂时不予理睬,而让他们等待,直到处理机已完成本次中断的处理后,处理机再去检查是否有中断发生。若有,再去处理新到的中断,若无,则返回被中断的程序,在该方法中,所有中断都按顺序依次执行,优点是简单,但不适合用于对实时性要求较高的中断请求。

- 嵌套中断:设置了中断优先级的系统中,当同时有多个不同优先级的中断请求时,CPU 优先响应最高优先级的中断请求。高优先级的中断请求可以抢占正在运行的低优先级中断的处理机。

中断处理过程:

- 每个指令执行完后,CPU 都会检测是否有未响应的外中断信号;

- 如果检测到外中断信号,则保护被中断进程的 CPU 环境(如程序状态字 PSW,程序计数器、各种寄存器);

- 根据中断信号类型转入相应的中断处理程序,进行中断处理;

- 恢复 CPU 的现场并退出中断,返回原进程继续执行。

(1)进程1在用户态运行了一段时间后,CPU会接收到计时部件(操作系统内核的时钟管理部件)发出的中断信号,表示进程1已经用完了一个时间片,CPU会切换到核心态,把CPU的使用权限交还给操作系统,操作系统内核就会对刚才的中断进行处理,操作系统知道进程1的时间片用完,就需要切换进程,在完成切换进程的一系列工作后,操作系统又会将CPU的使用权交还给用户进程。

(2)接着进程2拿到CPU执行权就会在用户态下执行,进程2执行一段时间后,进程2发出系统调用(内中断信号),请求输出,主动要求操作系统介入工作,CPU会立即切换到核心态,把CPU的使用权限交还给操作系统,操作系统内核接管进程2系统调用请求,调用IO设备开始输出工作,然后操作系统交还CPU执行权,IO设备也会并行执行,进程2需要等待IO操作完成,所以进程1拿到CPU执行权开始运行。当执行一段时间后,IO操作完成,IO设备向CPU发送一个中断信号,此时CPU由用户态再次转换为核心态,对刚才的中断信号处理,由于IO操作完成,所以操作系统知道进程2可以恢复运行了,以完成后续工作,所以操作系统再次交还CPU执行权,让进程2再次运行。

中断信号由外部设备发起,准确来说是由外部设备的控制器发起,因为外部设备本身并不能发起信号。比如网卡设备,网络数据包到达网卡,网卡的控制器就向IO APIC发送中断信号,IO APIC把信号发送给本地APIC,本地APIC把信号传送给CPU,如果根据当时情况,要处理这个中断,就保存当时的运行上下文,切换到中断上下文中,根据IDT查找对应的处理函数进行处理。处理完成后,需要恢复中断之前的状态。

- 以上实例参考:操作系统中断

- 中断硬件实现参考:详解操作系统中断