《Windows CE嵌入式开发入门——基于Xscale架构》第1章 GPIO和中断控制器

GPIO(General-Purpose I/O,通用输入/输出)的数量和功能以及中断控制的能力是处理器功能强弱的体现,PXA255处理器的GPIO以及中断控制器提供了丰富的资源,增加了系统设计的灵活性。

1.1 GPIO

PXA255处理器提供了81个GPIO引脚,同时提供了27个寄存器来控制这些引脚的工作方式和状态。这27个寄存器控制了引脚的输出/输入方向、引脚状态以及引脚的附加功能(关于引脚的附加功能将在后文讲解)。此外,这些GPIO中的一部分引脚还具有将处理器从睡眠中唤醒的功能。

对于不使用的GPIO引脚来说,如果将它们设置成输出状态,可以降低系统的电源消耗。

1.1.1 GPIO操作(GPIO operation)

当GPIO引脚被设置成输入状态时,可以作为中断输入引脚使用。在系统复位后,所有81个GPIO引脚都被设置成输入状态。

当GPIO引脚被设置成输出状态时,可以通过向引脚赋值来决定引脚电平的高低。向GPSR寄存器输出1代表高电平,向GPCR寄存器输出1代表低电平。

从GPIO引脚状态寄存器(GPLR)读取数据,可以获得当前引脚的状态。同时引脚还提供了上升沿和下降沿探测寄存器,读这些寄存器数据将能获得在引脚上发生的是上升沿还是下降沿。

1.1.2 GPIO附加功能(Alternate Function)

多数GPIO都有附加的功能,例如,充当串口的输出/输入、LCD控制器的数据通道口等。这些功能的实现和硬件的设计相关。表1-1给出了各个GPIO引脚的附加功能。需要注意的是,即便使用附加功能,仍然需要适当地设置引脚的相关寄存器。

表1-1 PXA255 GPIO引脚的附加功能

| 引脚 |

附加功能名称 |

附加功能任务 |

AF编码 |

来 源 单 元 |

信 号 描 述 |

| GP1 |

GP_RST |

ALT_FN_1_IN |

01 |

时钟和电源管理单元 |

GP_reset信号发生后,处于低电平状态 |

| GP6 |

MMCCLK |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC时钟 |

| GP7 |

48MHz clock |

ALT_FN_1_OUT |

01 |

时钟和电源管理单元 |

48MHz时钟输出信号 |

| GP8 |

MMCCS0 |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC片选0 |

| GP9 |

MMCCS1 |

ALT_FN_1_OUT |

01 |

MMC片选1 |

|

| GP10 |

RTCCLK |

ALT_FN_1_OUT |

01 |

系统集成单元 |

实时时钟(1Hz) |

| GP11 |

3.6MHz |

ALT_FN_1_OUT |

01 |

时钟和电源管理单元 |

3.6MHz晶振频率输出 |

| GP12 |

32kHz |

ALT_FN_1_OUT |

01 |

32kHz输出 |

|

| GP13 |

MBGNT |

ALT_FN_2_OUT |

10 |

内存控制器 |

内存判别器,判别外设是否被允许接入系统总线 |

| GP14 |

MBREQ |

ALT_FN_1_IN |

01 |

内存控制器可选总线的主要请求 |

|

| GP15 |

nCS_1 |

ALT_FN_2_OUT |

10 |

片选1,低电平有效 |

|

| GP16 |

PWM0 |

ALT_FN_2_OUT |

10 |

PWM0输出 |

|

| GP17 |

PWM1 |

ALT_FN_2_OUT |

10 |

PWM1输出 |

|

| GP18 |

RDY |

ALT_FN_1_IN |

01 |

外部总线就绪 |

|

| GP19 |

DREQ[1] |

ALT_FN_1_IN |

01 |

外部DMA请求 |

|

| GP20 |

DREQ[0] |

ALT_FN_1_IN |

01 |

外部DMA请求 |

|

| GP23 |

SCLK |

ALT_FN_2_OUT |

10 |

SSP串行端口 |

SSP时钟 |

| GP24 |

SFRM |

ALT_FN_2_OUT |

10 |

SSP帧 |

|

| GP25 |

TXD |

ALT_FN_2_OUT |

10 |

SSP发送 |

|

| GP26 |

RXD |

ALT_FN_1_IN |

01 |

SSP接收 |

|

| GP27 |

EXTCLK |

ALT_FN_1_IN |

01 |

SSP ext_clk |

|

| GP28 |

BITCLK |

ALT_FN_1_IN |

01 |

AC97控制单元 |

AC97比特时钟信号 |

| BITCLK |

ALT_FN_2_IN |

10 |

I2S控制器 |

I2S比特时钟信号 |

|

| BITCLK |

ALT_FN_1_OUT |

01 |

I2S比特时钟信号 |

||

| GP29 |

SDATA_IN0 Unit |

ALT_FN_1_IN |

01 |

AC97控制器 |

AC97 Sdata_in0信号 |

| SDATA_IN |

ALT_FN_2_IN |

10 |

I2S控制器 |

I2S Sdata_in信号 |

|

| GP30 |

SDATA_OUT |

ALT_FN_1_OUT |

01 |

I2S控制器 |

I2S Sdata_out信号 |

| SDATA_OUT |

ALT_FN_2_OUT |

10 |

AC97控制器 |

AC97 Sdata_out信号 |

|

| GP31 |

SYNC |

ALT_FN_1_OUT |

01 |

I2S控制器 |

I2S同步信号 |

| SYNC |

ALT_FN_2_OUT |

10 |

AC97控制器 |

AC9同步信号 |

续表

| 引脚 |

附加功能名称 |

附加功能任务 |

AF编码 |

来 源 单 元 |

信 号 描 述 |

| GP32 |

SDATA_IN1 |

ALT_FN_1_IN |

01 |

AC97控制器 |

AC97 Sdata_in1信号 |

| SYSCLK |

ALT_FN_1_OUT |

01 |

I2S控制器 |

I2S系统时钟 |

|

| GP33 |

nCS[5] |

ALT_FN_2_OUT |

10 |

内存控制器 |

片选5,低电平有效 |

| GP34 |

FFRXD |

ALT_FN_1_IN |

01 |

UARTs |

FFUART接收信号 |

| MMCCS0 |

ALT_FN_2_OUT |

10 |

MMC控制器 |

MMC片选0 |

|

| GP35 |

CTS |

ALT_FN_1_IN |

01 |

UARTs |

FFUART无发送数据 |

| GP36 |

DCD |

ALT_FN_1_IN |

01 |

FFUART数据装载探测 |

|

| GP37 |

DSR |

ALT_FN_1_IN |

01 |

FFUART数据设置就绪 |

|

| GP38 |

RI |

ALT_FN_1_IN |

01 |

FFUART Ring Indicator |

|

| GP39 |

MMCCS1 |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC片选1 |

| FFTXD |

ALT_FN_2_OUT |

10 |

UARTs |

FFUART传输数据 |

|

| GP40 |

DTR |

ALT_FN_2_OUT |

10 |

UARTs |

FFUART数据终端就绪 |

| GP41 |

RTS |

ALT_FN_2_OUT |

10 |

FFUART发送请求 |

|

| GP42 |

BTRXD |

ALT_FN_1_IN |

01 |

UARTs |

BTUART接收数据 |

| HWRXD |

ALT_FN_3_IN |

11 |

HWUART |

HWUART接收数据 |

|

| GP43 |

BTTXD |

ALT_FN_2_OUT |

10 |

UARTs |

BTUART发送数据 |

| HWTXD |

ALT_FN_3_OUT |

11 |

HWUART |

HWUART发送数据 |

|

| GP44 |

BTCTS |

ALT_FN_1_IN |

01 |

UARTs |

BTUART无数据发送 |

| HWCTS |

ALT_FN_3_IN |

11 |

HWUART |

HWUART无数据发送 |

|

| GP45 |

BTRTS |

ALT_FN_2_OUT |

10 |

UARTs |

BTUART请求发送数据 |

| HWRTS |

ALT_FN_3_OUT |

11 |

HWUART |

HWUART请求发送数据 |

|

| GP46 |

ICP_RXD |

ALT_FN_1_IN |

01 |

红外端口 |

ICP接收数据 |

| RXD |

ALT_FN_2_IN |

10 |

UARTs |

STD_UART接收数据 |

|

| GP47 |

TXD |

ALT_FN_1_OUT |

01 |

UARTs |

STD_UART发送数据 |

| ICP_TXD |

ALT_FN_2_OUT |

10 |

红外端口 |

ICP发送数据 |

|

| GP48 |

nPOE |

ALT_FN_2_OUT |

10 |

内存控制器 |

外接卡输出使能 |

| HWTXD |

ALT_FN_1_OUT |

01 |

HWUART |

HWUART发送数据 |

|

| GP49 |

nPWE |

ALT_FN_2_OUT |

10 |

内存控制器 |

外接卡写使能 |

| GP50 |

HWRXD |

ALT_FN_1_IN |

01 |

HWUART |

HWUART数据接收 |

| HWCTS |

ALT_FN_1_IN |

01 |

HWUART |

HWUART无数据发送 |

|

| GP51 |

nPIOW |

ALT_FN_2_OUT |

10 |

内存控制器 |

外接卡I/O写操作 |

| HWRTS |

ALT_FN_1 OUT |

01 |

HWUART |

HWUART请求发送数据 |

续表

| 引脚 |

附加功能名称 |

附加功能任务 |

AF编码 |

来 源 单 元 |

信 号 描 述 |

| GP52 |

nPCE[1] |

ALT_FN_2_OUT |

10 |

内存控制器 |

外接卡地址空间使能 |

| GP53 |

nPCE[2] |

ALT_FN_2_OUT |

10 |

外接卡地址空间使能 |

|

| GP53 |

MMCCLK |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC时钟 |

| GP54 |

MMCCLK |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC时钟 |

| GP54 |

nPSKTSEL |

ALT_FN_2_OUT |

10 |

内存控制器 |

外接卡区域socket片选信号 |

| GP55 |

nPREG |

ALT_FN_2_OUT |

10 |

内存控制器 |

26外接卡地址第26位 |

| GP56 |

nPWAIT |

ALT_FN_1_IN |

01 |

外接卡地址空间等待信号 |

|

| GP57 |

nIOIS16 |

ALT_FN_1_IN |

01 |

内存控制器 |

I/O总线地址宽度 |

| GP58 |

LDD[0] |

ALT_FN_2_OUT |

10 |

LCD控制器

|

LCD数据引脚0 |

| GP59 |

LDD[1] |

ALT_FN_2_OUT |

10 |

LCD数据引脚1 |

|

| GP60 |

LDD[2] |

ALT_FN_2_OUT |

10 |

LCD数据引脚2 |

|

| GP61 |

LDD[3] |

ALT_FN_2_OUT |

10 |

LCD数据引脚3 |

|

| GP62 |

LDD[4] |

ALT_FN_2_OUT |

10 |

LCD数据引脚4 |

|

| GP63 |

LDD[5] |

ALT_FN_2_OUT |

10 |

LCD数据引脚5 |

|

| GP64 |

LDD[6] |

ALT_FN_2_OUT |

10 |

LCD数据引脚6 |

|

| GP65 |

LDD[7] |

ALT_FN_2_OUT |

10 |

LCD数据引脚7 |

|

| GP66 |

LDD[8] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚8 |

| MBREQ |

ALT_FN_1_IN |

01 |

内存控制器 |

候选总线主请求 |

|

| GP67 |

LDD[9] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚9 |

| MMCCS0 |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC片选0 |

|

| GP68 |

MMCCS1 |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC片选1 |

| LDD[10] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚10 |

|

| GP69 |

MMCCLK |

ALT_FN_1_OUT |

01 |

MMC控制器 |

MMC_CLK |

| LDD[11] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚11 |

|

| GP70 |

RTCCLK |

ALT_FN_1_OUT |

01 |

系统集成单元 |

实时时钟(1Hz) |

| LDD[12] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚12 |

|

| GP71 |

3.6MHz |

ALT_FN_1_OUT |

01 |

时钟和电源管理单元 |

3.6MHz晶振时钟 |

| LDD[13] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚13 |

|

| GP72 |

32kHz |

ALT_FN_1_OUT |

01 |

时钟和电源管理单元 |

32kHz时钟 |

| LDD[14] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚14 |

|

| GP73 |

LDD[15] |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD数据引脚15 |

| MBGNT |

ALT_FN_1_OUT |

01 |

内存控制器 |

|

续表

| 引脚 |

附加功能名称 |

附加功能任务 |

AF编码 |

来 源 单 元 |

信 号 描 述 |

| GP74 |

LCD_FCLK |

ALT_FN_2_OUT |

10 |

LCD控制器 |

LCD帧时钟 |

| GP75 |

LCD_LCLK |

ALT_FN_2_OUT |

10 |

LCD扫描行时钟 |

|

| GP76 |

LCD_PCLK |

ALT_FN_2_OUT |

10 |

LCD像素时钟 |

|

| GP77 |

LCD_ACBIAS |

ALT_FN_2_OUT |

10 |

LCD AC Bias |

|

| GP78 |

nCS[2] |

ALT_FN_2_OUT |

10 |

内存控制器 |

片选2,低电平有效 |

| GP79 |

nCS[3] |

ALT_FN_2_OUT |

10 |

内存控制器 |

片选3,低电平有效 |

| GP80 |

nCS[4] |

ALT_FN_2_OUT |

10 |

内存控制器 |

片选4,低电平有效 |

| GP81 |

NSSPSCLK |

ALT_FN_1_IN |

01 |

Network SSP |

NSSP串行时钟为输入 |

| NSSPSCLK |

ALT_FN_1_OUT |

01 |

NSSP串行时钟为输出 |

||

| GP82 |

NSSPSFRM |

ALT_FN_1_IN |

01 |

NSSP帧为输入 |

|

| NSSPSFRM |

ALT_FN_1_OUT |

01 |

NSSP帧为输出 |

||

| GP83 |

NSSPTXD |

ALT_FN_1_OUT |

01 |

NSSP发送 |

|

| NSSPRXD |

ALT_FN_2_IN |

10 |

NSSP接收 |

||

| GP84 |

NSSPTXD |

ALT_FN_1_OUT |

01 |

NSSP发送 |

|

| NSSPRXD |

ALT_FN_2_IN |

10 |

NSSP接收 |

PXA255的GPIO主要功能框架如图1-1所示。

图1‑1 PXA255 GPIO功能框架

1.1.3 GPIO寄存器定义(如表1-2)

有27个寄存器来控制GPIO引脚,这些引脚可以分为以下几类:

n 3个引脚状态寄存器(GPLR);

n 6个引脚输出状态寄存器(GPSR、GPCR);

n 3个引脚方向寄存器(GPDR);

n 6个选择上升沿或者下降沿被捕获的控制寄存器(GRER & GFER);

n 3个显示被选择边沿被触发的状态寄存器(GEDR);

n 6个决定引脚是否为普通GPIO的寄存器。

表1‑2 PXA255 GPIO寄存器定义

| 寄存器类型 |

寄存器功能 |

GPIO |

GPIO |

GPIO |

GPIO |

GPIO |

GPIO |

| GPLR |

监视引脚状态 |

GPLR0 |

GPLR1 |

GPLR2 |

|||

| GPSR |

控制输出引脚状态 |

GPSR0 |

GPSR1 |

GPSR2 |

|||

| GPCR |

GPCR0 |

GPCR1 |

GPCR2 |

||||

| GPDR |

设置引脚方向 |

GPDR0 |

GPDR1 |

GPDR2 |

|||

| GPER |

边沿探测 |

GRER0 |

GRER1 |

GRER2 |

|||

| GFER |

GFER0 |

GFER1 |

GFER2 |

||||

| GEDR |

边沿类型探测 |

GEDR0 |

GEDR1 |

GEDR2 |

|||

| GAFR |

设置可选功能 |

GAFR0_L |

GAFR0_U |

GAFR1_L |

GAFR1_U |

GAFR2_L |

GAFR2_U |

1.GPIO Pin-Level寄存器(GPLR0、GPLR1、GPLR2)

这些寄存器中包含了引脚电平的信息,其中每个位都代表了一个引脚的电平状态。GPLR0[31:0]寄存器对应GPIO[31:0]这32个引脚,同样GPLR1[31:0]对应GPIO

[63:32]、GPLR2[16:0]对应GPIO[80:64]。这些寄存器是只读的,并且不受数据传输方向的干扰。

GPLR0位定义如表1-3所示。

表1‑3 GPLR0位定义

| 位 号 |

名 称 |

描 述 |

| <31:0> |

PL[x] |

GPIO Pin Level ‘x’(x = 0 to 31) |

GPLR1位定义如表1-4所示。

表1‑4 GPLR1位定义

| 位 号 |

名 称 |

描 述 |

| <31:0> |

PL[x] |

GPIO Pin Level ‘x’(x = 32 to 63) |

| <31:0> |

PL[x] |

0–引脚为低电平 |

GPLR2位定义如表1-5所示。

表1‑5 GPLR2位定义

| 位 号 |

名 称 |

描 述 |

| <31:21> |

— |

被保留 |

| <20:0> |

PL[x] |

GPIO Pin Level ‘x’(x = 64 to 80) |

2.GPIO引脚方向寄存器(GPDR0、GPDR1、GPDR2)

GPDR0、GPDR1和GPDR2这3个寄存器控制了引脚的数据传送方向。如果相应的位被设置成1,则代表该引脚为输出引脚。GPDR2[31:17]是被保留的,必须写入0。在系统启动或者复位后,所有引脚都为输入方向,因此保留位不必修改。

3.GPIO Pin Output Set Registers (GPSR0、GPSR1、GPSR2)and Pin Output Clear Registers(GPCR0、GPCR1、GPCR2)

当一个GPIO引脚被设置成输出方向时,引脚的状态可以通过设置GPSR或者GPCR来更改。如果要输出高电平,则需要向GPSR中的特定位写入1,要清除时,则需要向GPCR中的特定位写入1。GPSR和GPCR都是只写的寄存器。向这两种寄存器的任何位写入0都不会带来任何实际效果。

4.GPIO上升沿探测寄存器(GRER0、GRER1、GRER2)和下降沿探测寄存器(GFER0、GFER1、GFER2)

每一个GPIO都可以被设置来探测并且记录边沿的触发。如果探测到相应的边沿被触发,则相关的寄存器就会被置位。利用这个机制,可以来处理中断。

5.GPIO边沿探测状态寄存器(GEDR0、GEDR1、GEDR2)

GEDR0、GEDR1和GEDR2中一共有81位来对应81个引脚。当GFER或者GRER中设置的边沿被探测到之后,这个寄存器中的相应位就被置位。

当GEDR中的位被设置成1后,需要用户手动通过写状态寄存器来清除该位。GEDR被置1后,可以产生一个中断。在所有81个引脚中,任何一个引脚的边沿探测记录都将引起同一个中断。

6.GPIO附加功能寄存器(GAFR0_L、GAFR0_U、GAFR1_L、GAFR1_U、GAFR2_L、GAFR2_U)

GAFR0_L、GAFR0_U、GAFR1_L、GAFR1_U、GAFR2_L、GAFR2_U对应了81个GPIO引脚。每个GPIO都可以被配置成通用GPIO引脚或者3个附加的输入功能或者3个附加的输出功能。当然,要使用附加的输入功能,引脚必须被配置成输入方向。

这些寄存器中,每两个位为一组,对应一个GPIO引脚:

n 00代表通用GPIO功能;

n 01代表附加输入功能(ALT_FN_1_IN)或者附加输出功能(ALT_FN_1_OUT);

n 10代表附加输入功能(ALT_FN_2_IN)或者附加输出功能(ALT_FN_2_OUT);

n 11代表附加输入功能(ALT_FN_3_IN)或者附加输出功能(ALT_FN_3_OUT)。

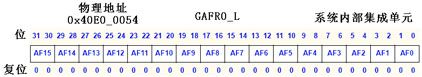

GAFR0_L的定义如图1-2与表1-6所示。

图1-2 GAFR0_L

表1-6 GAFR0_L定义

| 位 号 |

名 称 |

描 述 |

| <31:0> |

AF[x] |

GPIO引脚可选功能选择位。每一对位都决定了一个GPIO引脚的类型: |

GAFR0_U的定义如图1-3与表1-7所示。

图1-3 GAFR0_U

表1‑7 GAFR0_U定义

| 位 号 |

名 称 |

描 述 |

| <31:0> |

AF[x] |

GPIO引脚可选功能选择位。每一对位都决定了一个GPIO引脚的类型: |

1.2 中断控制器

中断控制器控制了处理器上的所有外部中断,并且保存了一级中断源的信息。它记录了一个中断是属于IRQ还是FIQ。在PXA255中,除了FIQ以外的所有中断都处于同一中断级别。

1.2.1 中断控制器操作

PXA255的中断处理操作由两层结构组成。

第一级中断处理能定位中断设备,这些设备的中断必须已经被使能(Interrupt Controller Control Register ICCR)或者在中断掩码寄存器Interrupt Controller Mask Register(ICMR)中没有被屏蔽掉。第一级中断处理由以下寄存器控制。

n Interrupt Controller Pending寄存器(ICPR):记录系统中所有活动的中断。

n Interrupt Controller IRQ Pending寄存器(ICIP):记录系统活动的所有IRQ中断,而Interrupt Controller Level寄存器(ICLR)可以通过编程向ICIP产生中断,然后由ICIP向系统产生一个IRQ。

n Interrupt Controller FIQ Pending寄存器(ICFP):记录系统活动的所有FIQ中断。Interrupt Controller Level寄存器(ICLR)可以通过编程向ICFP发送中断,然后由ICFP产生FIQ。

第二级中断处理使用产生中断源设备(产生一级中断的外围设备)中的中断寄存器。二级中断的处理信息将为中断处理状态提供额外的记录,并且在中断服务例程中将被使用到。总体来说,二级中断之间采用“或”的方式产生一级中断。通常产生中断的源设备可以避免通过读取两个寄存器的值就可以进行判断,即通过在IRQ的情况下可以读取ICIP寄存器、在FIQ的情况下可以读取ICFP寄存器来确定产生中断的源设备,然后再通过读取设备中的状态寄存器来确定具体调用哪个中断处理程序。处理器在空闲的状态下,当ICCR寄存器中的对应位为0时,ICMP中的掩码将被忽略,任何中断都能将处理器从空闲状态中唤醒。如果ICCR寄存器中的对应位为1,则视ICMP中的掩码来决定中断是否能被处理器处理。ICCR复位值都为0。

PXA255的中断控制器结构如图1-4所示。

图1‑4 PXA255中断控制器结构

1.2.2 中断控制器寄存器定义

中断控制器包含以下寄存器:

n Interrupt Controller IRQ Pending寄存器(ICIP);

n Interrupt Controller FIQ Pending寄存器(ICFP);

n Interrupt Controller Pending寄存器(ICPR);

n Interrupt Controller Mask寄存器(ICMR);

n Interrupt Controller Level寄存器(ICLR);

n Interrupt Controller Control寄存器(ICCR)。

系统复位后,FIQ和IRQ中断默认关闭,并且所有中断控制器的寄存器都被清零。中断必须有软件控制才能使用。

1.Interrupt Controller Mask寄存器(ICMR)

ICMR寄存器有22个中断屏蔽位,屏蔽位决定pending interrupt bit是否能产生中断。当pending interrupt bit为1时,只有当ICMR的屏蔽位为1时,产生的中断才能被处理器处理。而在空闲状态下,ICMR的启用必须先将ICCR[DIM]设置为1,否则任何产生的中断都将被处理器处理。

ICMR在系统复位后被清零,这意味着所有的中断都被屏蔽,然后必须由软件来重新配置ICMR。

ICMR的定义如图1-5与表1-8所示。

图1-5 ICMR

表1‑8 ICMR定义

| 位 号 |

名 称 |

描 述 |

| <31:8> |

IM[x] |

中断屏蔽,x为8~14或者17~31位 |

| <7:0> |

- |

保留 |

2.Interrupt Controller Level寄存器(ICLR)

ICLR寄存器决定pending interrupt位是否产生FIQ或者IRQ中断。如果中断挂起位没有被屏蔽掉,那么将根据ICLR中相应位来决定产生中断的类型。如果中断被屏蔽,则ICLR中相应的位就无效。ICLR在系统复位后被清零,然后必须由软件来重新配置ICMR。

ICLR的定义如图1-6与表1-9所示。

图1-6 ICLR

表1‑9 ICLR定义

| 位 号 |

名 称 |

描 述 |

| <31:8> |

IL[x] |

中断级别,x为8~14或者17~31位 |

| <7:0> |

- |

保留 |

3.Interrupt Controller Control寄存器(ICCR)

ICCR寄存器,各个位为Disable Idle Mask(DIM)标记,如图1-7所示,它决定了处理器在空闲状态下中断掩码是否有效。

ICCR的定义如图1-7与表1-10所示。

图1-7 ICCR

表1‑10 ICCR定义

| 位 号 |

名 称 |

描 述 |

| <31:1> |

- |

保留 |

| <0> |

D|M |

关闭空闲掩码 |

4.Interrupt Controller IRQ Pending寄存器(ICIP)和FIQ Pending寄存器(ICFP)

ICIP和ICFP寄存器包含了22个中断位,如图1-8和图1-9所示,这些位表明外设是否已经产生中断。在中断服务例程中读取这两个寄存器的值,就可以判别发生中断的设备,进而读取设备上的寄存器。在寄存器ICIP中,每个位都是这两个寄存器相应位的或运算后的结果,它们是只读的。

ICIP的定义如图1-8与表1-11所示。

图1-8 ICIP

表1‑11 ICIP定义

| 位 号 |

名 称 |

描 述 |

| <31:8> |

IP[x] |

IRQ挂起位,x为8~14或者17~31 |

| <7:0> |

- |

保留 |

CIFP的定义如图1-9与表1-12所示。

图1-9 ICFP

表1‑12 ICFP定义

| 位 号 |

名 称 |

描 述 |

| <31:8> |

FP[x] |

FRQ挂起位,x为8~14或者17~31 |

| <7:0> |

- |

保留 |

5.Interrupt Controller Pending寄存器(ICPR)

ICPR是一个32位只读寄存器,它显示了系统中活动的所有中断。这些位不会被ICMR影响。

在图1-10中所示是ICPR对应的二级中断的产生设备。ICPR的定义如表1-13所示。

图1-10 ICPR

表1‑13 ICPR定义

| 位 号 |

名 称 |

描 述 |

| <31> |

IS31 |

RTC警报匹配寄存器中断挂起 |

| <30> |

IS30 |

RTC Hz时钟时间片寄存器中断挂起 |

| <29> |

IS29 |

OS时钟匹配寄存器3中断挂起 |

续表

| 位 号 |

名 称 |

描 述 |

| <28> |

IS28 |

OS时钟匹配寄存器2中断挂起 |

| <27> |

IS27 |

OS时钟匹配寄存器1中断挂起 |

| <26> |

IS26 |

OS时钟匹配寄存器0中断挂起 |

| <25> |

IS25 |

DMA通道服务请求寄存器中断挂起 |

| <24> |

IS24 |

SSP服务请求中断挂起 |

| <23> |

IS23 |

MMC状态探测中断挂起 |

| <22> |

IS22 |

FFUART传输/接收/错误中断挂起 |

| <21> |

IS21 |

BTUART传输/接收/错误中断挂起 |

| <20> |

IS20 |

STUART传输/接收/错误中断挂起 |

| <19> |

IS19 |

ICP传输/接收/错误中断挂起 |

| <18> |

IS18 |

I 2C 服务请求中断挂起 |

| <17> |

IS17 |

LCD控制服务请求中断挂起 |

| <16> |

IS16 |

网络SSP服务请求中断挂起 |

续表

| 位 号 |

名 称 |

描 述 |

| <15> |

- |

保留 |

| <14> |

IS14 |

AC97中断挂起 |

| <13> |

IS13 |

I2S中断挂起 |

| <12> |

IS12 |

PMU中断挂起 |

| <11> |

IS11 |

USB服务中断挂起 |

| <6:0> |

- |

保留 |