Verilog中的逻辑运算符与按位运算符的区分

我们在写Verilog的时候经常会用到的是低电平复位问题,例如:

always@(posedge clk or negedge rst_n) begin

if(~rst_n) ...;

else ...;

end由于rst_n是一位的,所以使用逻辑非!,或者是按位非~,效果是一样的,但是如果遇到的是向量呢?

逻辑非和按位非就不能混用了。包括逻辑或||,按位或|等。

二者之间的长相区别很明显,按位操作一般只有单个符号,例如:&,|,而逻辑是双的,如:&&,||。

下面给出一个例子:

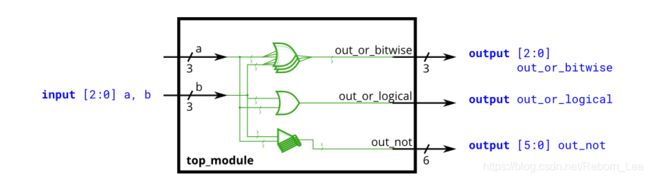

Bitwise vs. Logical Operators

a和b是输入,out_or_bitwise和out_or_logic分别是按位或与逻辑或的结果。

out_not是a和b的按位取反,b在高位。

写出代码如下:

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not = {~b, ~a};

endmodule