北京大学《计算机组成》陆俊林

目录

-

- 冯诺依曼结构

- 计算机结构模型

-

-

- 1. 模型机的控制器

- 2. 模型机的运算器

- 3. 模型机的存储器

-

- 指令执行过程

- MIPS指令集

-

-

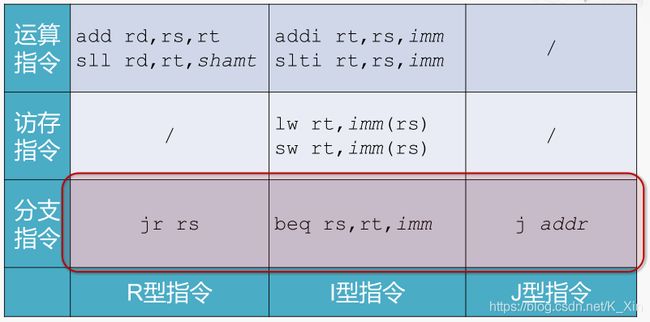

- 1. R型指令(Register)

- 2. I型指令(Immediate)

- 3. 分支指令(Branch)

-

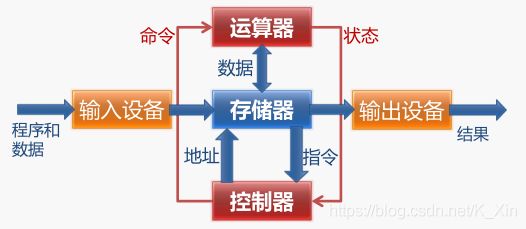

冯诺依曼结构

(1) 计算机应由运算器、控制器、存储器、输入设备和输出设备共5个部分组成

(2) 数据和程序均以二进制代码形式不加区别地存放在存储器中,存放位置由存储器的地址指定

(3) 采用 “存储程序” 工作方式,即计算机在工作时能够自动地从存储器中取出指令加以执行

计算机结构模型

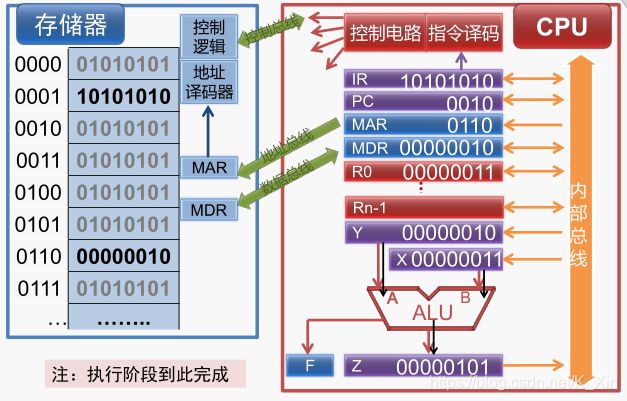

1. 模型机的控制器

(1) 指令寄存器 IR 存放正在执行或即将执行的指令,程序计数器存 PC 存放“下一条指令的存储单元地址”,具有自动增量计数的功能

(2) 存储器地址寄存器 MAR 存放需要读或写的存储单元的地址,存储器数据寄存器 MDR 存放需要读取或即将写入存储单元的数据

(3) 指令译码部件对 IR 中的指令进行译码,以确定IR中存放的是哪一条指令,控制电路根据指令产生控制信号,在时序脉冲的同步下控制各个部件的动作

2. 模型机的运算器

(1) R0 ~ Rn-1 是 n n n 个通用寄存器,用于临时存放数据。数据可能来自存储器,也可能来自其它通用寄存器或 ALU 的输出

(2) 核心部件 ALU 用于完成算术运算和逻辑运算。X、Y、Z作为ALU 的数据暂存器,可视为 ALU 的一部分,X、Y 中的数据在 ALU 中进行运算,将运算结果送到 Z,运算结果的状态(零/正负/进位/溢出)送到 F。

3. 模型机的存储器

(1) 控制总线负责传递读、写、完成等控制信号,控制逻辑负责具体执行控制信号的操作

(2) 地址总线负责传送CPU正在读或写的存储单元的地址,传送的地址会暂时保存在 MAR;数据总线负责传送CPU正在读出或即将写入存储单元的数据,传送的数据会暂时保存在 MDR。

(3) 存储单元的位宽由编址方法确定,如果存储器按字节编址,则每个存储单元存放8位二进制数。存储单元的数量由地址总线的宽度确定,如果地址总线宽度为 n n n,则存储单元的总数为 2 n 2^n 2n 个。

指令执行过程

初始状态

初始状态时,寄存器 R0 保存的内容为 00000011,程序计数器 PC 保存的下条指令地址为 0001

取指

① 控制器将指令的地址送往存储器:控制器将指令地址从 PC 通过内部总线送到 MAR,再通过地址总线送到存储器的 MAR,同时控制器向存储器发出 Read 命令

② 存储器按给定的地址读出指令内容:存储器控制逻辑收到 Read 命令,指示地址译码器翻译 MAR 中的地址,然后根据地址读取该存储单元的内容,并传送到内存数据寄存器 MDR

③ 存储器将指令送回控制器:存储器将指令从存储器 MDR 通过数据总线传送到中央处理器 MDR,并将指令通过内部总线传送到 IR 以便继续执行

译码

控制器分析指令的操作性质,将二进制指令 10101010 译码为 ADD R0 , [6],然后向有关部件发出指令所需的控制信号

执行

① 控制器从通用寄存器或存储器取出操作数:控制器根据指令 [6] 从存储单元 0110 获取数据至 MDR,然后将 R0 的内容传送至 X,MDR 的内容传送至 Y

② 控制器命令运算器对操作数进行指令规定的运算:控制器将 X 和 Y 的内容相加,输出运算结果至 Z,运算结果状态至 F

回写

将运算结果写入通用寄存器或存储器:控制器将 Z 保存的运算结果传送至 R0,指令执行完毕

MIPS指令集

MISP指令集的特点:

- 指令长度固定,简化取指操作

- 寻址模式简单,简化取数操作

- 指令数量少,功能简单,简化指令执行

- 只有 load 和 store 可以访问存储器

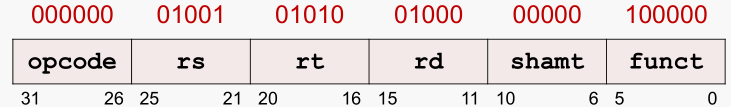

1. R型指令(Register)

rs(Source Register):通常用于指定第一个源操作数所在的寄存器编号

rt(Target Register):通常用于指定第二个源操作数所在的寄存器编号

rd(Destination Register): 通常用于指定目的操作数(保存运算结果)的寄存器编号

shamt(shift amount):用于指定移位指令进行移位操作的位数,非移位指令设为0

例:MIPS指令 add $8,$9,$10 对应的二进制代码

查询指令编码表,可知 opcode = 0 ,funct = 32,shamt = 0 (非移位指令)

根据操作指令数,可知 rd = 8(目的操作数),rs = 9(第一个源操作数),rt = 10(第二个源操作数)

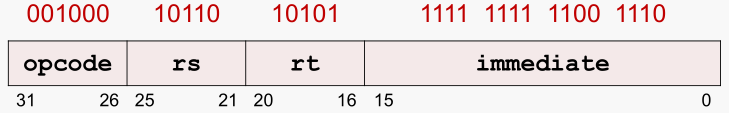

2. I型指令(Immediate)

rt(Target Register):I型指令指定用于目的操作数(保存运算结果)的寄存器编号

例:MIPS指令 addi $21,$22,-50 对应的二进制代码

查询指令编码表,可知 opcode = 8

根据操作指令数,可知 rt = 21(目的操作数),rs = 22(源操作数),immediate = -50(立即数)

3. 分支指令(Branch)

MIPS的分支指令也分为条件分支和非条件分支

条件分支:根据比较的结果改变控制流,包括两条指令beq(==)和bne(!=)

非条件分支:无条件地改变控制流,包含一条指令jump(j)