CSAPP 深入理解计算机系统 第六章存储器

6.1.1随机访问存储器

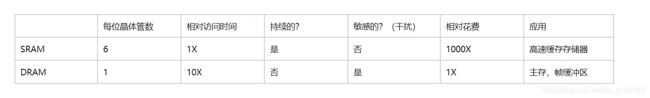

RAM分为两类:SRAM&DRAM.

速度:SRAM>>DRAM

价格:SRAM>>>DRAM

1.静态RAM(SRAM)

基本单元:双稳态的存储器单元

原理:六晶体管电路->可以无限制地保存在两个不同的电压配置或状态之一。

特点:抗干扰性强,可迅速在干扰消除时恢复稳定状态。

2.动态RAM(DRAM)

基本单元:一个电容+一个访问晶体管(电容充电-存储每位)

特点:对干扰非常敏感,电容电压被扰乱后,无法恢复。DRAM单元10-100毫秒内会失去电荷

应用:数码照相机&摄像机的传感器

计算机中处理:内存系统周期性读出,重写刷新每一位。

3.传统DRAM

组成:单元位有d个超单元组成,每个超单元由w个DRAM单元组成。存储共d*w位信息。超单元排列为r行c列的长方形,rc=d.

内存控制器工作原理:a)一次传入w位至DRAM中

b)一次从DRAM中传出w位 具体步骤:1.内存控制器发送行地址(RAS)给DRAM,再发送列地址(CAS)(DRAM先讲整行内容复制到一个内部行缓冲区,等待列命令,再把所求i,j单元内容复制到内存控制器中。)

2.DRAM把超单元的内容(i,j)传给内存控制器.

注:若要获得1,2;1,3;1,4内容,必须发送3次行地址,3次列地址,不可合并

4.内存模块

DRAM芯片封装在内存模块中,插到主板的扩展槽上。

内存模块基本思想:每个超单元存储主存的一个字节,面对相应超单元地址为(i,j)的8个超单元表示主存中字节地址为64位字。

DRAM 0 中存储第一个(低位)字节,DRAM 1 存储下一个,以此类推。

取出内存步骤:目的:取出内存地址A处的一个字

1.内存控制器将A转换为一个超单元地址(i,j),发送到内存模块

2.内存模块将i和j广播到每个DRAM中

3.每个DRAM输出它的(i,j)超单元8位内容

4.模块中电路手机输出,合并为一个64字,返回给内存控制器。

5.增强的DRAM

-

快页模式(FAST PAGE MODE)DRAM:允许对行地址的重复使用 e.g:(RAS CAS CAS CAS)连续取同一行中不同列数据

-

扩展数据输出(Extended data out)DRAM:快页模式DRAM的增强形式,允许各个CAS信号在时间上靠的紧密一些。

-

同步(Synchrounus)DRAM:常规DRAM与内存控制器通信使用异步信号,SDRAM使用外部时钟信号的上升沿替代原来控制信号。最终效果:SDRAM更快输出超单元内容。

-

双倍数据速率同步 (Double data-rate Synchrounous)DRAM:DDR SDRAM是对SDRAM的增强。

-

视频RAM:使用在图形系统的帧缓冲区。

6.非易失性存储器

断电后,DRAM,SRAM会丢失数据,非易失性(Nonvlatile memory)不会。

-

可擦写可编程ROM(Erasable progtammable rom)&电子可擦除PROM

-

闪存(flash memory)

7.访问主存:

总线:一组并行的导线,可携带地址,数据和控制信号。

总线事务:1.读事务:主存传送数据->CPU

2.写事务:CPU->主存

计算机系统配置:CPU芯片 与 I/O桥连接器的芯片组 与内存模块

6.1.2 磁盘存储

-

磁盘构造

构成:盘片——两面/表面:磁性记录材料

中央可旋转主轴5400-15000转每分钟。

磁盘表面结构:磁道同心圆,每个磁道划为一组扇区,扇区包含相等数据位,扇区间空隙:标识扇区位的格式化位。

柱面:所有盘面上到主轴中心的距离相等的磁道的集合。

2.磁盘容量

-

记录密度:磁道一英寸的段中可放入的位数

-

磁道密度:从盘片中心出发半径一英寸的段内可以有的磁道数

-

面密度:磁道密度*记录密度

字节数*平均扇区数*磁道数*表面数*盘片数

磁盘容量= ————————————————————

扇区*磁道*表面*盘片*磁盘

3.磁盘操作

读写:读/写头存储在磁盘表面的位,读写头连接在一个传动臂一端,通过半径轴前后移动。

对扇区访问时间:

-

寻道时间:移动传动臂所需的时间

-

旋转时间:读/写头定位到磁道上,等待目标扇区的第一个位旋转到读/写头的时间

-

传送时间:依赖于旋转速度和每条磁道的扇区数目。

4.逻辑磁盘块

磁盘封装中有一个小的磁盘控制器,维护逻辑块号和实际磁盘扇区之间的映射关系。

逻辑块号翻译为(盘面,磁道,扇区)三元组。

5.连接I/O设备

-

通用串行总线控制器:;连接到USB总线设备的中转机构

-

图形卡:负责代表CPU在显示器上画像素

-

主机总线适配器 将一个或多个磁盘连接到 I.O总线上,使用主机总线接口协议

6.访问磁盘

内存映射技术:地址空间中一块地址是为与I/O设备通信保留的I/O端口,设备连接到总线时,与一个或多个端口相关联。

6.1.3固态硬盘

SSD封装到I/O总线上标准硬盘插槽。一个SSD封装由一个或多个闪存芯片和闪存翻译层组成。闪存翻译层扮演磁盘控制器的

组成:由B个块的序列组成,每个块由P页组成,页的大小为512字节~4KB 块由32-128页组成,大小为16KB~512KB

-

数据以页为单位读写,只有在一页所属的块被擦除后,才可以写这一页、

-

随机写慢。-擦除需要时间较长 -写操作试图修改一个包含已经有的数据的页p,则这个块中所有带有数据的页都必须被复制到一个新的块,才能对p进行重写。

优点:1.没有移动的部件,所以随机访问时间比旋转磁盘快,能耗低。

缺点:SSD容易磨损。

6.2 局部性

-

时间局部性:被引用过一次的数据很可能在不远的将来被再次引用,是较好的时间局部性

-

空间局部性:一个内存位置被引用了,那么程序在不久的将来会引用其附近的一个内存位置。

-

局部性总结:1.重复引用相同变量的程序有良好的时间局部性。

2.对与具有步长为k的引用模式的程序,步长越小,空间局部性越好。

3.对于取指令来说,循环有好的时间和空间局部性。循环体越小,循环迭代次数越多,局部性越好。

6.3 存储器的层次结构

6.3.1 存储器层次结构中的缓存

-

存储器层次结构的中心思想:对于每个K,位于K蹭的更快更小的存储器设备作为位于K+1层的更大更慢的存储设备的缓存。层次结构中的每一层都缓存来自较低一层的数据对象。

-

存储器层析结构中缓存的一般性概念:K+1层的存储器被划分为连续的数据对象组块——块。每个块有唯一的地址或名字。

-

数据以块为传送单元,在K层与K+1层来回复制。

1.缓存命中

当程序需要K+1层中的数据对象d中,在第K层的一个块中寻找d,若d存在缓存K层中,称为缓存命中。

2.缓存不命中

第K层没有缓存数据对象d,则为缓存不命中。

此时第K层的缓存从K+1层中取出包含d的块,放入K层(若K层已满,则需覆盖一个块)。

-

牺牲块:被覆盖替换的现存块。

3.缓存不命中的种类

-

强制性不命中/冷不命中 冷缓存(cold cache):第K层缓存是空的,对任何数据对象的访问都不命中。

发生不命中,K层必须采用严格的放置策略,确定K+1层的块放在K层何处。限制性放置策略确定k+1层的块放在k层的(i mod n)中。

-

冲突不命中:限制性放置策略引起的不命中。数据对象会映射到同一个缓存块,然后缓存会一直不命中。

-

容量不命中:每个阶段访问缓存块的某个相对稳定的集合。当工作集的大小超过缓存的大小,缓存会容量不命中。(缓存太小,不能处理工作集)

4.缓存管理

存储器层次结构的本质:每一层存储设备都是较低一层的的缓存。

在一个虚拟内存的系统中,DRAM主存作为存储在磁盘上的数据块的缓存,由操作系统软件和CPU上的地址翻译硬件共同管理。

6.4 高速缓存存储器

6.4.1 通用的高速缓存存储器组织结构

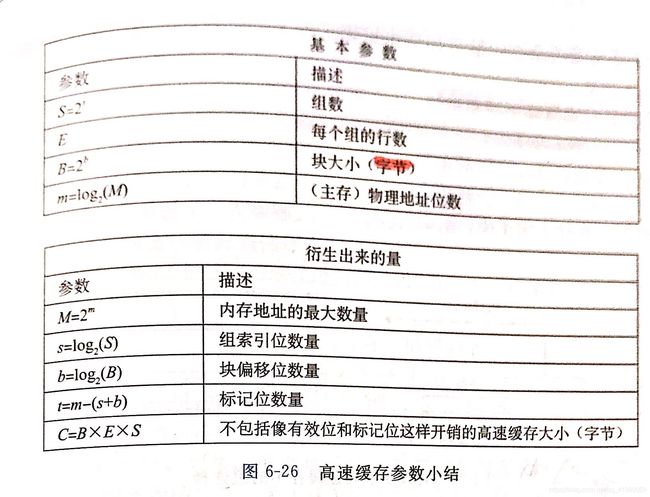

高速缓存 S=2^s个高速缓存组,每组E个高速缓存行。每行由B=2^b字节数据块组成。

一个有效位+t个标记位+B字节内容 有效位指明是否包含有意义信息,标记位为内存地址位的一个子集

高速缓存可用元祖(S,E,B,m)表示,C=S*E*B

-

S,B将m个地址位分为三个字段,地址A中s个组索引位是一个到S个组的索引,先由A中的s位得出组号,t告诉我们这个组的哪一行包含这个字,b表明在B个字节中数据块中字的偏移。

有关内存缓冲命中的 下一篇单独讲,整理太长了,贴起来好累