2020/7/12硬件学习笔记

硬件学习笔记

高频信号布线时要注意哪些问题?

1.信号线的阻抗匹配;

2.与其他信号线的空间隔离;

3.对于数字高频信号,差分线效果会更好;

**差分线:**差分信号基石驱动端发送两个两个等值、反向的信号,接收端通过比较两个电压的差值来判断逻辑状态1或者0,而承载差分信号的一对走线就称为差分走线。

差分线的优势:

a.两根差分线之间的耦合非常好,当外界存在干扰时,几乎是同时被耦合到两条线上,而接收端关心的只有两信号的差值,所以外界的共模噪声可以被完全抵消。

b.有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以互相抵消,耦合得越紧密,相互抵消的磁力线就越多,泄放到外界的电磁能量就越小。

c.时序定位准确,由于差分信号的开关变化是位于两个信号的交点,而不是普通单端信号依靠高低两个阈值电压判断,因而受工艺、温度影响小,能降低时序上的误差,同时也更适合低幅度信号的电路。

**差分线要求:**等长、等距、等线宽

等长是为了保证两个差分信号时刻保持相反极性,减少共模分量

等距是指两差分线要一直保持平行

**等长线:**等长线的作用就是让信号传输的速度一致,通常用在高速存储器的地址和数据线上,如rs485,差分线在布线时要尽可能保持等距等长。

蛇形走线

因为应用场合不同而具不同的作用:

(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如PCI-Clk,AGPCIK,IDE,DIMM等信号线。

(2)若在一般普通PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。如2.4G的对讲机中就用作电感。

(3)对一些信号布线长度要求必须严格等长,高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据)。

(4)蛇形走线在某些特殊的电路中起到一个分布参数的LC滤波器的作用。

应该在模拟Vcc和数字Vcc之间用磁珠,还是应该在模拟地和数字地之间用磁珠?

模拟VCC经过LC滤波后得到数字VCC,模拟地和数字地间用磁珠。

用磁珠或MECCA连接数字、模拟地时,是利用其频率特性,使数字地中高频成分不影响模拟地,同时保证二者电平相等。那么,0ohm电阻连接数字、模拟地有什么作用,有时还只用一小块铜连接,能分析一下吗?

磁珠的等效电路相当于带阻限波器,只对某个频点的噪声有显著抑制作用,使用时需要预先估计噪点频率,以便选用适当型号。对于频率不确定或无法预知的情况,磁珠不合。0欧电阻相当于很窄的电流通路,能够有效地限制环路电流,使噪声得到抑制。电阻在所有频带上都有衰减作用(0欧电阻也有阻抗),这点比磁珠强。铜皮类似于0ohm电阻。)

一般情况,对于电源产生部分,要用10u和0.1u的电容去耦,要同时考虑高频和低频的去耦;对于其他原件一般都是用0.1u的电容在电源部分去耦。

阻抗匹配时,若引脚给出的阻抗值为复数,即既有阻抗部分又有电抗部分,这时阻抗匹配如何做?光考虑电阻部分吗?

考虑共轭匹配,将阻抗的虚部抵消。

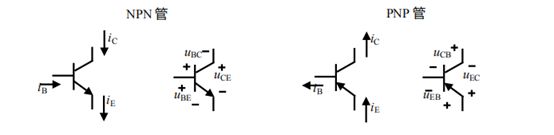

三极管整理:

电流的定义:他依从于发射极电流的方向。对NPN管,发射极电流iE是流出的,那么基级电流iB和集电极电流iC都定义为流入。相对的,对于PNP管,发射极iE是流入的,那么基级电流iB和集电极电流iC都定义为流出。

对于NPN管,基级是P型半导体,定义基级点位uB减去发射极点位uE为发射结电压,写作uBE,此值为正值才能让发射结的PN结处于正向导通状态。对于PNP管则相反,基级是N型半导体,则定义发射极电极uE减去基级电位uB为发射结电压,写作uEB,此值为正值才能让发射结处于正向导通状态。

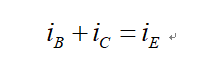

晶体管的三个管脚电流,永远满足基尔霍夫定律:

在晶体管处于放大状态下,他的集电极电流唯一受控于基极电流,而与c,e两端电压uCE无关:

无源器件

电容:

目前常用的三种电容分别为:铝电解电容、钽电容和多层陶瓷电容(MLCC)

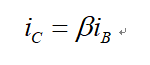

电容在开关电源设计中有多种作用:储能、滤波、补偿等。像所有实际器件一样,电容有寄生效应:有效串联电阻(ESR)和有效串联电感(ESL)。

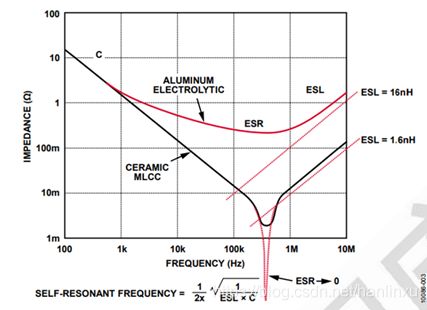

理想电容的阻抗会随着频率提高而单调下降,下图显示了两个不同100F电容的阻抗与频率的关系,一个是铝电解电容,另一种是多层陶瓷电容。在较低频率时,阻抗会随着频率的提高而单调下降,符合预期。然而由于存在ESR,再某一频率时,此阻抗会达到最小值、当频率继续提高时,电容开始表现得像一个电感,阻抗也会随之提高。阻抗与频率关系曲线称为浴盆曲线,所有实际电容都有类似行为。

多个电容并联已获得较大的电容也许是明智的,并联情况下,电容会增加,而ESR和ESL则会降低。让两个或更多电容并联,便可获得较大的电容和较低的电感和电阻,从而满足设计要求。

铝电解电容的容值大、成本低,在所有选择中,其成本比最佳,主要的缺点是ESR较大,可达数欧姆,铝电解电容还依赖于电解质,由于电解质会逐渐变干,因此寿命较短。

钽电容使用钽粉作为电介质,与同等铝电容相比,钽电容能以更小的封装提供更大的容值,不过成本较高。ESR通常在100mΩ范围内,比铝电容低。钽电容不使用液态电解质,因而寿命比铝电解型要长。由于这个原因,钽电容在高可靠性应用中很受欢迎。钽电容对浪涌电流敏感,有时需要串联电阻来限制浪涌电流。钽电容失效时可能会烧毁并冒烟。

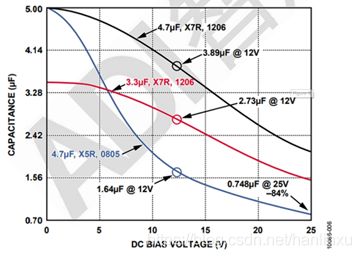

多层陶瓷电容(MLCC)提供极低的ESR(<10mΩ)和ESL(<1nH),采用小型标贴封装。MLCC最大容值可达100F,不过当=当容值大于10F时,物理尺寸和成本会增加。在使用时,应注意MLCC的电压额定值及其结构中使用的电介质,下图显示了三种不同电容的容值与施加电压的关系,结论为,X7R型电介质性能最佳,大力推荐使用。

由于电介质的压电效应,陶瓷电容对PCB振动敏感,所产生的电压噪声可能会扰乱PLL等敏感模拟电路,此类敏感应用中,不受振动影响的钽电容是更好的选择。

电感:

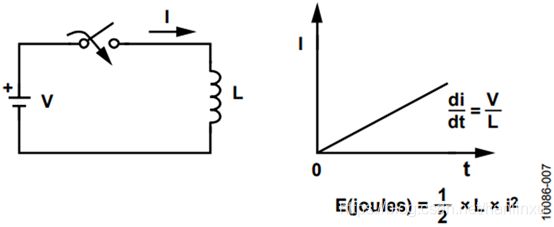

电感是磁性储能元件,通常是将线圈缠绕在磁芯上构成。电流流过电感时,会在磁芯中感生一个磁场,该磁场就是储能机制。由于电感中的电流无法立即改变,因此当把一个电压施加于电感时,电流会斜坡上升,斜率为电压/电感

除电感这一参数外,还有串联电阻(DCR)和并联电容。DCR主要是由线圈电阻引起,对电感的功率损耗计算很重要,并联电容与电感一起可能引发电感自谐振,自谐振频率可通过 计算。

电感的功率损耗会引起电感温度升高和效率降低。电感的功率损耗主要有两类,一类是DCR损耗,就是导线的I2R损耗,也称为铜损耗。另一类是铁芯损耗,铁芯损耗是铁芯内磁滞和涡电流的综合效应,但通常难以确定准确的铁芯损耗信息。

电感通常有两种铁芯材料:铁氧体和铁芯粉。铁芯粉的材料之间有气隙,导致饱和曲线比较平缓,因此,采用这种铁芯材料的电感更适合需要瞬时大电流的应用;铁氧体磁芯电感会更快速饱和,但成本和铁芯损耗较低。

低值电感的优势:

1.更低的DCR

2.更高的饱和电流

3. 更高的di/dt

4.更快的开关频率

5.更好的瞬态响应

高值电感的优势:

1.更低的纹波电流

2.更低的铁芯损耗

3.电路开关中的电流有效值更低

4.满足输出纹波要求所需的电容更低

目前电感家族中较新的成员是多层芯片电感,这种电感支持非常小的物理封装(0805),电感值目前最高可达4.7H,因此适合较高开关频率的设计,小尺寸也限制了电流处理能力(1.5A),因此不能用于较高功率的设计,与标准绕线电感相比,成本更低,尺寸更小,DCR更低。

此外,还有屏蔽电感,虽然该电感价格昂贵且饱和电流较低,但能大大降低电磁干扰(EMI)。

二极管:

肖特基二极管,它属一种低功耗、超高速半导体器件。最显著的特点为反向恢复时间极短(可以小到几纳秒),正向导通压降仅0.4V左右。其多用作高频、低压、大电流整流二极管、续流二极管、保护二极管,也有用在微波通信等电路中作整流二极管、小信号检波二极管使用。在通信电源、变频器等中比较常见。

变容二极管又称"可变电抗二极管",是利用pN结反偏时结电容大小随外加电压而变化的特性制成的。反偏电压增大时结电容减小、反之结电容增大,变容二极管的电容量一般较小,其最大值为几十皮法到几百皮法,最大区容与最小电容之比约为5:1。它主要在高频电路中用作自动调谐、调频、调相等。

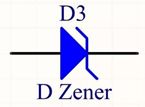

稳压二极管利用pn结反向击穿状态,其电流可在很大范围内变化而电压基本不变的现象,制成的起稳压作用的二极管。

开关电源中的“开关”一般是MOSFET,超高电压和电流设计可能会使用IGBT晶体管,MOSFET主要分为N沟道和P沟道两大类,N沟道增强型需要一个正栅极-源极电压才能导通,导通电阻低于相同大小的P沟道器件,成本更低;P沟道器件需要一个负栅极-源极电压电压才能导通,导通电阻比较大,成本略高。

在选择MOSFET时,必须注意一些关键性能参数:Rds、Vds、Vgs、Cdss、Cgs、Cgd和Pmax等。

Rds为驱动栅极时器件的导通电阻,MOSFET一个良好的特性是Rds具有正温度系数,这使得MOSFET非常适合并联使用(当其中一个并联的MOSFET的温度上升时,具有正的温度系数导通电阻也增加,因此流过的电流减小,温度降低,从而实现自动的均流达到平衡)。

Vds表示MOSFET的击穿电压,应选择大于系统电压的击穿电压额定值,击穿电压越高通常意味着成本越高,因此不需要选择额定值过大的器件。

Vgs指栅极-源极阈值电压,即使其导通所需要的电压。

未完待续/2020/0712