【黑金原创教程】【TimeQuest】【第二章】TimeQuest模型角色,网表概念,时序报告

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢!

黑金动力社区2013年原创教程连载计划:

http://www.cnblogs.com/alinx/p/3362790.html

《FPGA那些事儿--TimeQuest 静态时序分析》REV2.0 PDF下载地址:

http://www.heijin.org/forum.php?mod=viewthread&tid=22393&extra=page%3D1

第二章:模型角色,网表概念,时序报告

2.1 TimeQuest模型的努力

2.2 SDC的网表(Net Lists)基本单位

2.3 TimeQuest模型的简单实例

2.4 进一步看看TimeQuest模型如何分析时序

2.5 建立sdc文件与网表

2.6 时钟约束

2.7 时序报告

总结:

第二章:模型角色,网表概念,时序报告

2.1 TimeQuest模型的努力

我们知道TimeQuest的存在是某师兄所追求的神器,目的是要给懒人们一个解决物理时序的福利,其中最耀眼的就是TimeQuest模型。在前面笔者也曾介绍过TimeQuest模型它是什么?它基于什么?它有什么误点?”。然在这一章节当中,笔者将会讨论它是用来“干什么?”。

TimeQuest模型是用来解决两个点寄存器(节点)之间的建立关系和保持关系问题。但是在一个最简单的HDL设计,不可能仅是由两个寄存器就组成,里边可能会有“很多很多很多”对寄存器。结果TimeQuest就会用自己的时序分析模型,逐个检查“很多很多很多”对寄存器之间的“建立关系和保持关系是否合格化”。

试想看看,举例最简单的计数器设计,里边就有多少对寄存器?而且TimeQuest这个机器将会逐个去分析保持关系和建立关系,TimeQuest的行为和努力真是让笔者感动到全身扑地。好了不多废话了,进入主题吧。

2.2 SDC的网表(Net Lists)基本单位

网表 Net Lists是什么?嗯 ... 笔者真的不想用太多专业的话来讲因为太无趣了,因此我们从另一个角度去看网表。笔者喜欢把FPGA看成一座巨大的逻辑资源库,如果读者喜欢玩具的话,也可以把它看成乐高积木库,那么HDL 就是这个逻辑资源库的建模工具。

但是有一点比较不同的是,HDL是一个理想的工具,HDL的建模是软模型,然而网表就是硬模型。FPGA综合的过程就像我们日常建立机械模型那样,我们必须先在电脑上建立一个软模型。当软模型的经过电脑模拟和测试以后,那么它会成为硬模型的理想参考物,最后模型设备会根据这个软模型,把金属生肉加工成为实物。

在FPGA综合的过程中,逻辑资源之间会开始“布线”,把相关的单位连线起来。设计有多大,那么连线的数量就越多,最终这庞大的连线就成为网表。

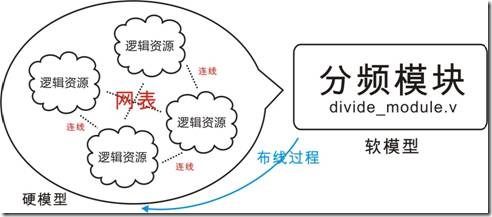

图2.2.1 布线过程·连线·网表的概念图

图2.2.1 是布线过程的概念图 ... 布线过程就是按软模型,在FPGA巨大的资源库里建立硬模型,逻辑资源之间的链接称为连线,所有连线的总和称为网表。明白了吗?对于不同的性质的网表都有不同的基本单位,对于TimeQuest 来说它是使用SDC网表。有关SDC的背景请维基百科一下 .... 它不在讨论范围之内。

SDC网表有它自己的基本单位,至于是那些基本单位呢?

| 基本单位 |

说明 |

| Cell |

SDC网表中最普遍的个体。FPGA中可以找到的寄存器呀, 片上RAM呀,PLL资源呀,硬件乘法器等逻辑资源。 |

| Pin |

Cell进出口。 |

| Net |

Pins之间的连线。 |

| Port |

顶层模块的顶层输入输出口。 |

Cell 从另一个角度来看,任何FPGA的逻辑资源都可以看成Cell。Pin是每一个Cell

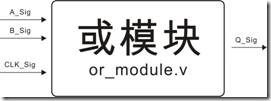

的进出口(软引脚)。Net就是连线了,最后的Port就是顶层模块的输入输出口(硬引脚)。好了,笔者就以一个 或模块 or_module.v 来解释。

图 2.2.2 或模块的建模图。

图2.2.2是一个软模块,亦即或模块的建模图,它有A_Sig,B_Sig 和CLK_Sig 输入,金额Q_Sig 输出。当这个或模块经过综合和布线以后,它会成为 ....

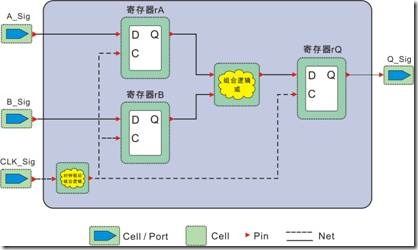

图2.2.3 布线过后的或模块

图2.2.3 是经过布线过后的或模块,每一个绿色框框都是 Cell,每一个红色箭头都是 Pin每一个连线都是 Net。但是有一点比较暧昧的就是 输入输出口,它既是Cell 也是 Port,这到底是什么一回事呢?

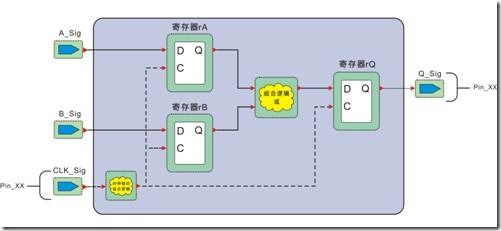

图2.2.4 配置引脚后就成为 Port

图2.2.4是从图2.2.3的基础上,将CLk_Sig和Q_Sig 配上引脚,最终造就它们都变身为Port。SDC网表的基本单位看看就好了,不要太计较它们是什么,因为它们的作用不大,不过它们又有什么作用呢?

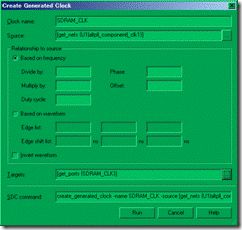

图 2.2.5 某个约束命令,基本单位的作用。

如图2.2.5所示,笔者简单举例一个约束命令,其功能先不管。基本上,基本单位的作用就是为约束命令设置 源对象(Source)或者目标对象(Targets)而已,如图2.2.5所示 ... 有一个名为 create_generated_clock 的约束命令,它约束的源对象是 pll的输出pin,亦即clk1,而约束的目前对象就是名为 SDRAM_CLK的输出port。

2.3 TimeQuest模型的简单实例

实验一: 入门实验

想了想,笔者还是用一个简单的实例来搞清楚,大体上TimeQuest 模型是如何工作 ... 这样的话,笔者也可以省下许多口水,读者认识也可以得更具体。

图 2.3.1 分频模块的建模图。

图2.3.1 是久违的建模图,它是名为 divide_module.v的分频模型,而主要功能是把 CLK_Sig 实现4分频,然后输出至Q_Sig。

1. module C1_module 2. ( 3. input CLK_Sig, 4. output Q_Sig 5. ); 6. 7. /*********************/ 8. 9. reg [2:0]C1; 10. 11. always @ ( posedge CLK_Sig ) C1 <= C1 + 1'b1; 12. 13. /***********************/ 14. 15. assign Q_Sig = C1[2]; 16. 17. /***********************/ 18. 19. endmodule

代码很简单而已,连小孩子都看懂了,读者不可能看不懂吧?看不懂的朋友自己仿真看看就好了。这个分频模块的内容也超级简单,就是把 C1[3]驱动Q_Sig(第15行)。

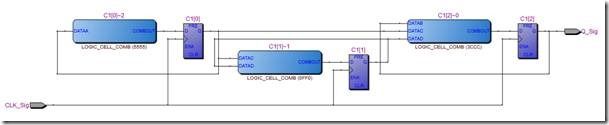

图2.3.2 TMV视图

图2.3.2 是分频模块的 Technology Mapping Viewer,关于这种视图还真的是不常用,它不过是用来分析物理时序才用得到的“理想概念视图”而已。接下来我们来看看,分配模块的里边到底有多少对寄存器(节点)需要TimeQuest去分析他们之间的建立关系和保持关系。

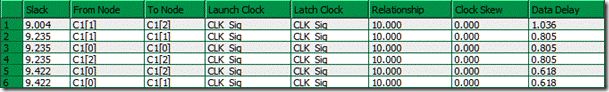

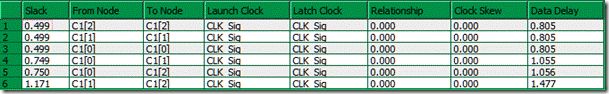

图2.3.3 六对寄存器的建立关系需要分析

图2.3.4 六对寄存器的保持关系需要分析

同学们千万不要慌图2.3.3~4的结果是如何得到的 .. 在这里,笔者只是要读者弄明白TimeQuest模型分析物理路径的大概经过而已,同学乖 ... 暂时先忍耐。

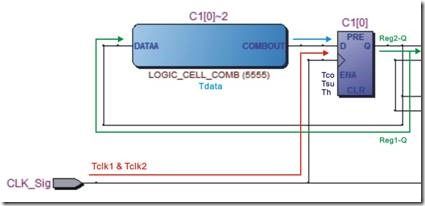

图2.3.5 第三对C1[0]~C1[0]寄存器

让我们先看第第3对,亦即C1[0] ~ C1[0]的分析经过。在此读者可能会觉得疑惑,同样都是C1[0]节点,为何建立关系和保持关系的分析过程会成立呢?读者稍微注意一下,图2.3.5的C1[0]的输出方向,除了reg2-Q以外,它还反馈给自己的reg1-Q,节点C1[0]~C1[0]也因此成立。

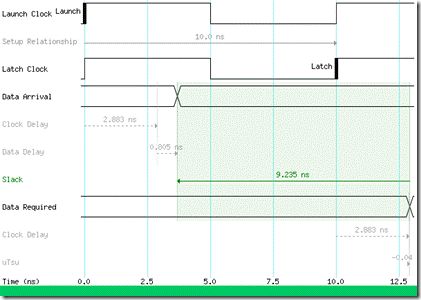

图2.3.6 把C1[0]拆开的概念图

图2.3.6是比较人性化的概念图,只要有两个寄存器(节点)那么TimeQuest模型就可以开始分析它们之间的建立关系和保持关系了。

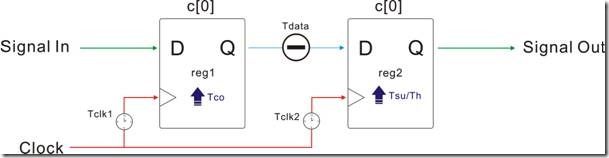

图2.3.7 第一(六)对C1[1]~C1[2]寄存器

相比之下,节点C1[1]~C1[2] 比起节点C1[0]~C[0]更容易理解。C1[1]是寄存器1的第1位,而C1[2]则是寄存器2的第2位,LOGIC_CELL_COMB 是Tdata延迟。然而其他节点也有大同小异的情形,笔者就不一一解释了,自己看着办吧。

就这样TimeQuest模型会一对一对的分析节点之间的建立关系和保持关系,一个设计里边有多少对节点,TimeQuest就分析多少对。只要所有节点没有发生违规时序(建立关系和保持关系合格,亦即建立余量和保持余量都为正值化),那么这个设计就okay了。换句话说,这个分频模块的物理时序是合格的,因为图2.3.3~4正好反馈所有节点的建立余量和保持余量都是正直。

在此有些朋友可能着急了,问道:“图2.3.3~4是如何得到的?”。安啦~朋友,前面的故事还没有说完,你这只太监怎么先着急了?不想当太监就要慢慢来 ...

在这个章节当中,笔者只是想帮读者们大概搞个明白 ... TimeQuest到底是如何使用自身的模型来进行时序分析,这些概念绝对是一个基础。有些玩TimeQuest 的朋友,根本就没有任何概念可言,有的只是纯公式而已,当然笔者并不反对纯公式的使用,只是纯公式它太无趣了,根本上也称不上学习。

不过在这章节中,笔者太感动了,TimeQuest真的是努力的孩子,如一个简单的分频模块,就有6对节点的时序需要分析,亦即C1[0]~C1[0],C1[0]~C1[1],C1[0]~C1[2],

C1[1]~C1[1],C1[1]~C1[2] 还有 C1[2]~C1[2] 。TimeQuest它都会一一去分析没对节点之间的时序。同样的,如果一个设计,里边有100对节点需要分析的话,TimeQuest也会组个去分析 ... 读者说TimeQuest是不是努力的好孩子?

2.4 进一步看看TimeQuest模型如何分析时序

笔者需要先强调一下,目前笔者还没有准备玩弄TimeQuest这个工具,反之了解TimeQuest模型才是学习TimeQuest的首要功课。笔者这种醉翁之意的心情,可能会使许多心急的朋友焦虑不安 ... 不过笔者劝告道:要玩转TimeQuest 就需要把 TimeQuest 模型每一个重要部分“窥视”清楚才行。TimeQuest模型,绝对不是网上所说的那样,几个公式,几个图像就可以解释清楚,实际上它更加神秘许多... 更加好玩。

在2.3章节中,我们知道TimeQuest模型都会逐个分析分频模块的所有节点之间的建立关系和保持关系。在这个章节当中,我们以“实际延迟”来实验看看TimeQuest如何使用模型来工作。因此故事的主角继续以 2.3章节分频模块为例。

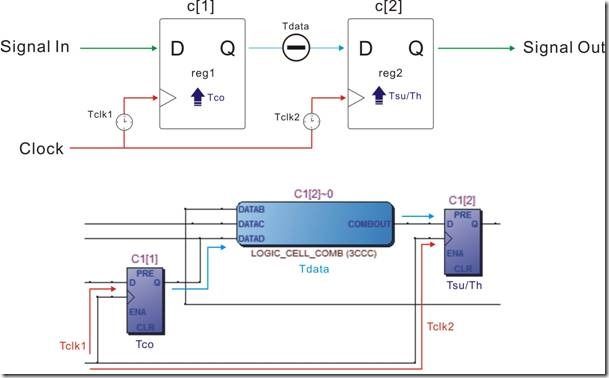

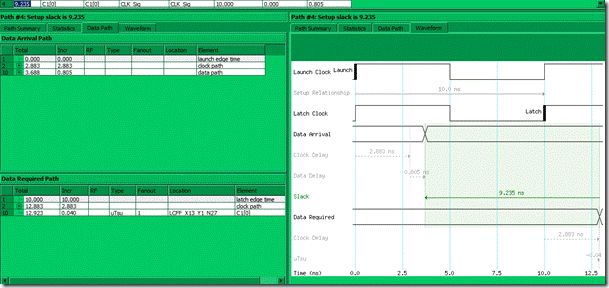

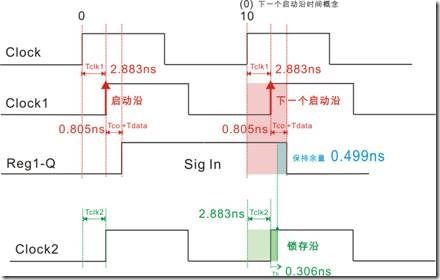

图2.4.1 节点C[0]~C[0]的物理状况(建立过程)。

图2.4.2 C1[0]~C1[0] 建立关系的分析过程。

图2.4.1是节点C1[0]~C1[0]的物理状况,而图2.4.1是该节点的建立关系过程。读者暂时把焦点放在 Data Arrival Path 那边... Clock路径亦即 Tclk1 它有2.883ns延迟 (TimeQuest都是以ns为计算单位),Data路径亦即 Tco + Tdata 它有 0.805ns延迟。

按照公式计算的话:

数据抵达时间 Data Arrival Time = 启动沿 + Tclk1 + Tco + Tdata

= 0 + 2.883 + 0.805(Tco + Tdata)

= 3.688ns

现在又把焦点放在 Data Required Path 的身上,亦即数据获取时间。锁存时间是 10ns(和理想建立关系值等价),Clock路径亦即 Tclk2它有2.883ns的延迟,uTsu就是 Tsu寄存器特性,延迟结果是 0.040ns。继续按照公式来计算的话:

数据获取时间 Data Required Time = 锁存沿(理想建立关系值)+ Tclk2 - Tsu

= 10ns + 2.883ns - 0.040

= 12.843ns

erh .... 怎么数据获取时间 Data Required Time的结果是 12.923ns 而不是 12.843ns ,这显得TimeQuest 把 Tsu加上而不是减掉?这其中发生什么事情了?是不是TimeQuest搞错了,还是笔者搞错了?不不不,谁都没有错,这个问题有许多因缘 ... 用傻瓜的话来讲,Tsu 这个延迟可有可无,实际情况上它非常接近0ns,因此 Tsu 可以小到忽略。

笔者稍微更动一下上面的计算结果:

数据获取时间 Data Required Time = 锁存沿(理想建立关系值)+ Tclk2 - Tsu

= 10ns + 2.883ns + 0.040

= 12.923ns

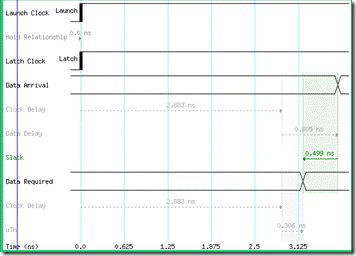

图2.4.3 节点c[0]~c[0] 波形图。

图2.4.3是TimeQuest为节点c[0]~c[0]提供的波形图,它有非常直观的效果,比笔者涂鸦更规格,真的很惭愧。这张图很容易看懂而已,读者就自己看着办吧。(注意不要过度转牛角尖关于右下角的 - 0.04 ~无视无视)。

最后再计算建立余量的结果:

建立余量 Setup Slack = 数据获取时间 - 数据抵达时间

= 12.923ns - 3.688ns

= 9.235ns

===================================================================

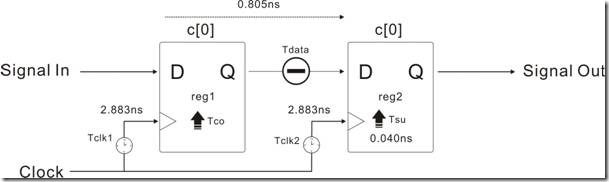

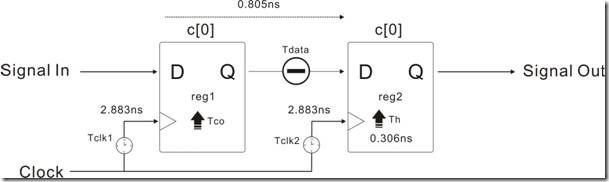

图2.4.4 节点C[0]~C[0]的物理状况(保持过程)。

图2.4.5 节点C[0]~C[0]保持关系的的分析过程。

在前面笔者曾说过TimeQuest模型中求出保持余量的有两种方法:一种是用头脑;另一种是用屁股。很不巧TimeQuest确实是使用屁股来计算,图2.4.5右边的波形图就是最好的证明。嗯 ... 读者是不是觉得很郁闷,无论怎么左看由看,感觉难看不明白?好吧,笔者再干一次善行 ...

图2.4.6 节点C[0]~C[0]保持关系的的分析过程的波形图。

图2.4.7 笔者为图2.4.6加笔的时序图。

从图2.4.6与图2.4.7的比较中,读者是否可以看出其中的跷蹊?关于这点笔者就不再解释了,自己看着办吧。好了,现在我们知道及节点C[0]~C[0]之间的理想保持关系值是 0ns,那么保持余量是:

数据抵达时间 Data Arrival Time = 启动沿 + Tclk1 + Tco + Tdata

= 0ns + 2.883ns + 0.805ns

= 3.688ns

数据获取时间 Data Required Time = 锁存沿 + Tclk2 + Th

= 理想保持关系值 + Tclk2 + Th

= 0ns + 2.883ns + 0.306ns

= 3.189ns

保持余量 Hold Slack = 数据抵达时间 - 数据获取时间

= 3.688ns - 3.189ns

= 0.499ns

除节点C[0]~C[0]以外,其他5对节点的分析过程也是大同小异。在这里,可能有些心急的同学已经耐不了性子了说,“我要用TimeQuest,我要搞TimeQuest!”。安啦安啦!下一章节开始就是了!要玩TimeQuest之前,理解一切基本的概念是必须的,读者不要问为什么笔者如此啰嗦,因为在接下来的故事当中,读者自然而然就会明白笔者的苦心。

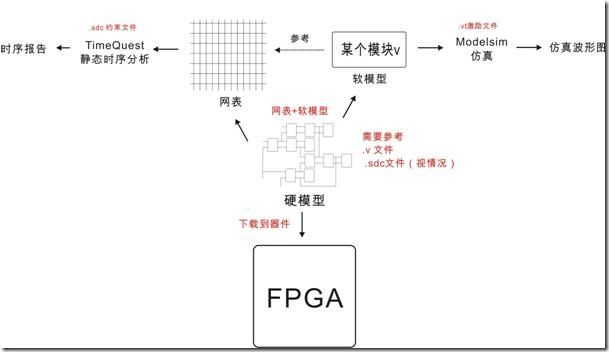

2.5 建立sdc文件与网表

有关TimeQuest工具的使用步骤,虽说网上许多版本,不过官方的阵营占大部分,方法都是见仁见智的东西,只要点到重点,什么方法都不重要。使用TimeQuest主要有两大步骤,一是配置,二是分析。

配置是指编译器的优化配置,因为不同的配置选项都会产生不同的时序结果。而TimeQuest分析,顾名思义就是使用TimeQuest分析某个设计。好了!废话还是少说,让我们开始期待已久的TimeQuest 初次之旅。

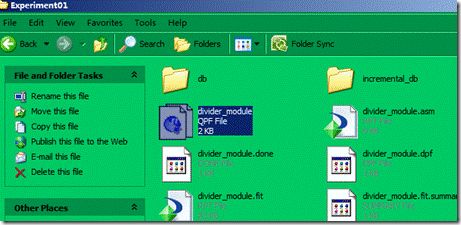

图2.5.1 打开实验一项目

首先先打开 divider_module 实验一的工程,如图2.5.1。该设计笔者已经编译过了,为了安全起见,笔者建议再编译一次。

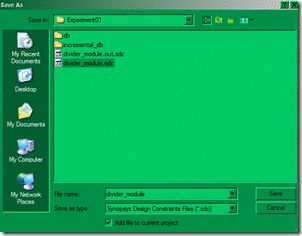

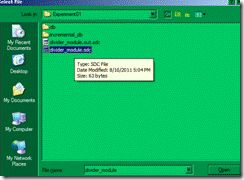

图2.5.2 建立同名sdc文件。

然后新建一个同名的SDC文件在实验一的目录下,该文件取名和实验一的项目名一样,亦即 divider_module.sdc,如图2.5.2所示。估计实验一的目录下已经有笔者原先建立好的 .sdc 文件,读者们可以删掉再建立,还是直接覆盖都行。

接下来将 divider_module.sdc 文件设置为该实验的默认sdc文件,过程如图2.5.3所示:

打开设定

选择“TimeQuest Timing Analyzer”,然后点击“...”。

将 divider_module.sdc 托载进来。

点击 Add把它添加进来。

图2.5.3 设置实验的默认sdc文件。

在这里,读者稍微注意一下 ... Quartus II 版本10之前,Classic Timing Analyzer 会作为默认的静态时序分析工具。反之10和以后的版本,TimeQuest作为默认时序分析工具。所以呀,不同的版本之间可能会有所出入,如果读者使用的Quartus II的版本是10之前的话必须将静态时序分析设置为 TimeQuest。当读者把 divider_module.sdc 文件添加进来以后,为以防万一再编译一次。

图2.5.4 打开TimeQuest

当编译完成以后,点击图2.5.4显示的“![]() ”图标,然后就会正式进入TimeQuest。

”图标,然后就会正式进入TimeQuest。

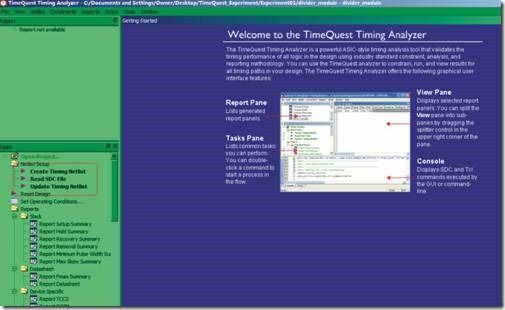

图2.5.5 TimeQuest界面

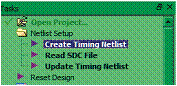

图2.5.5是TimeQuest的界面, 注意左边的红色框图吗?它是这一章节的主角了。

(一)Create Timing Netlist 说简单点就是建立网表,如果用笔者的话来说,就是软

模型 divider_module.v 开始布线,然后建立硬模型。

(二)Read SDC File 就是读取该项目中 .sdc 文件中“约束配置”。

(三)Update Timing Netlist 就是更新网表。每当我们更动过“旧网表的约束配置”,

然后我们必须再一次更新它。

关于“约束”这一词英文是 Constraint,从字面它是“什么被什么强迫或者限制”的意思。 事实上 Constraint 这一词用在TimeQuest上,没有那么黄和暴力,而且范围也很广。TimeQuest是一个工具也是一个笨蛋,宏观上“Constraint”的用意就是“告诉TimeQuest要怎么怎么干,要注意什么什么”。

| 图2.5.6 自动建立网表。 |

好了,我们要正式开始建立网表了。如图2.5.6所示,只要我们“双击”Crete Timing Netlist,那么TimeQuest就会自动建立默认网表。 但是不是所有同学都那么懒惰的 .... 除了自动建立以外,我们也可以手动建立网表。 |

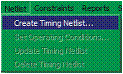

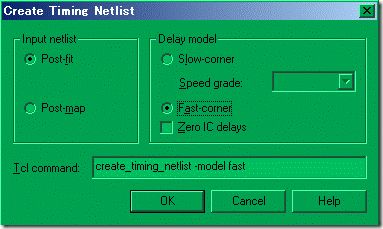

图2.5.7 手动建立网表。

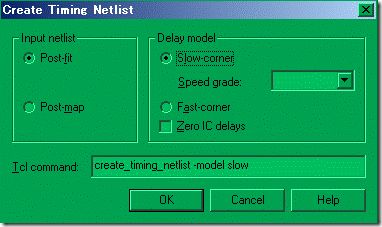

图2.5.7 是手动建立网表的经过,先是从Netlist菜单下点击 点击“Create Timing Netlist”,,如图2.5.7左图所示,然后就会自动弹出右图。右图的 Input Netlist 有 Post-fit 和 Post-map 选项,而且 Delay model 又有 Slow-corner ,Speed grade,Fast-corner 和 Zero IC delays 等选项。那么多选项,想必读者又要抓狂了,呜哇哇!

同学们千万不要慌,右图的各种选项设置会造就不同质量的网表,我们先粗略了解下各种选项字面上的意思 ...

Input netlist 字面上的意思是“输入网表”。

Post-fit 官方的定义是:

“The TimeQuest analyzer performs timing analysis on a timing netlist that contains physical synthesis optimizations and fitting”。

用傻瓜的话来讲,Post-fit网表会在建立之际会参考编译器的优化设置结果(亦即使用TimeQuest的第一步)。

Post-map 官方的定义是:

“The TimeQuest analyzer performs timing analysis on a timing netlist that contains complete synthesis information”

用傻瓜的话来讲,Post-map网表会参照综合结果而建立。结果来说,Post-map网表更接近原型(没有优化),但是post-fit更接近物理结果(有优化)。

===================================================================

Delay model 的意思如同字面上所示,亦即网表的延迟模型,用傻瓜的话来讲就是“网表的环境”。“笔者你在说什么,网表的延迟模型和网表的环境到底有什么关系?”汗!真是一群心急的孩子 ....

Slow-corner 的官方定义是:

“Uses the worst-case (slowest) timing model to compute delays depending on the speed grade of the device specified in the Speed grade list.”

worst-case字面上是指最差环境,也指极端情况。

Fast-corner 的官方定义是:

“Uses the best-case (fastest) timing model to compute delays.”

Best-case 字面上是指最好环境,也指舒适情况。

根据worst-case 与 best-case 的选择也会造就不同的质量的硬模型(网表),在此读者只要简单记住,worst-case硬模型有高保险余量高性能限制,而best-case硬模型有第保险余量低性能限制即可。如果用傻瓜的话来讲,best-case比worst-case的硬模型更接近实际的网表。

所谓的 zero_ic_delay 就是会无视一些网表基本单位的延迟。

根据上述各种设置以后,我们会得到不同质量的网表 ... 而“不同质量的网表”到底是什么一会事呢?笔者以数学的“π”为例,它的常量是 3.142,但是随着精度的不同,它的常量可以是 3.14159265358979 ,也可以是3.1415926535897932384。

不过“网表质量”的具体用意到底是什么呢?尝试想象看看 3.142的π,它可以是 3.1415,它也可以是 3.14159;换之 3.141592的π,它不可以是 3.142也不可以3.1415。

这就是“保险余量”的用意。嘛 ... 有关网表质量就先解释道这里吧,往后读者有一定的基础以后笔者会再详细讨论。

===================================================================

笔者再次强调一下,以上的内容纯属笔者自己的看法而已,至于读者信不信,就自己看着办吧。最后,至于什么样配置的网表才是最正规呢?这个是没有答案的问题!什么样的设计,就需要什么样的网表。不过对于一般实验而言,它就足够的说:

图2.5.8 够用的网表质量。

图2.5.8是够用的网表质量,这种 Create Timing Netlist的选项也是最接近 fpga的性能。

图2.5.9 默认的网表质量。

然而TimeQuest在默认下,亦即快捷双击“Create Timing Netlist”,TimeQuest会产生如图2.5.9所示的网表质量,又称默认网表。

好了,我们先闲聊一会儿让大脑放松放松 ... 在此有读者可能会问:“笔者对TimeQuest正体的约束过程,有什么样的概念呢?”嗯,虽然这是一个好问题 ... 让笔者慢慢解释吧。

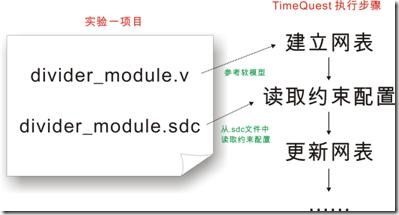

图2.5.10 TimeQuest正体的约束过程。

从图2.5.10中我们可以知道,当我们要为某一个模块(实验)执行静态时序分析(物理时序分析)的时候,我们必须先建立网表。然而在建立网表的过程,TimeQuest必须参考软模型,亦即 divider_module.v。但是网表的质量可以根据需要自行调整。接下来TimeQuest必须从 divider_module.sdc 中读取“任何的约束配置”,而“更新网表”是把“任何的约束配置”在网表生效。

在TimeQuest的一系列执行活动中,如建立网表,读取约束配置,更新网表 ...... 等等“这一切都是 TimeQuest的活动”,所谓TimeQuest的活动,它需要从项目中参考相关的内容,如图2.6.11所示。假设实验一通过时序分析,然后我们要把实验一的内容下载到开发板中 ... 这个时候我们所需要的东西也只有 .v 文件生成的硬模型而已。

用简单的话来说,当某个实验下载到开发板的时候,它有属于自己的“物理网表(硬模型)”。为了测试这个“物理网表”到底合不合格,所以我们需要用TimeQuest 这个工具“仿真”这个“物理网表”,而TimeQuest不会直接仿真“物理网表”,而是仿真不同质量的网表,又或者仿真不同质量的硬模型。

假设这个设计是发生在极端的环境里,这时候我们就要选择 worst-case 质量的网表,然后透过约束命令将各种延迟信息,时钟信息告诉TimeQuest。接着TimeQuest就会在这个模拟的环境中测试该硬模型,如果时序合格的话,那么该设计即使在极端的环境里也能正常发挥。

图2.5.11 笔者眼中的TimeQuest概念。

图2.5.11是笔者眼中的概念图,硬模型也就是某个.v 文件经过编译和综合的结果。然而一个硬模型可以分成软模型和网表。软模型可以用 Modelsim 仿真模块的功能(行为),

其中需要 .vt 文件作为激励过程;网表建立的过程中需要参考软模型;网表可以经TimeQuest计算时序,看是否合格?其中可以用 .sdc文件来“约束”网表。

在早期的实验当中,笔者通通都无视物理时序,换句话说就不把 .sdc 文件看在眼里。当Quartus II 发现某个设计如果没有被指定 .sdc 文件,那么Quartus II 就会用默认的“Classic Timing Analysis”去分析网表了(Classic Timing Analysis似乎只是在早期的Quartus II 出现--版本10.0以前)。如果时钟频率不高的话,以黑金开发板为例 -- 20Mhz,50ns的周期时间,不管有没有静态时序工具分析网表,硬模型产生的结果都“够用”了。

那些熟读过笔者笔记的家伙,间接上会明白笔者的思维和思路是非常逻辑,所使用的办法当然也是非常逻辑。在这里笔者所要强调的是,既然笔者是如此逻辑那么执行TimeQuest的步骤(过程)也要逻辑。读者竟可以的话,把 .sdc 文件看成是硬模型的激励文本,或者TimeQuest 的参考物。

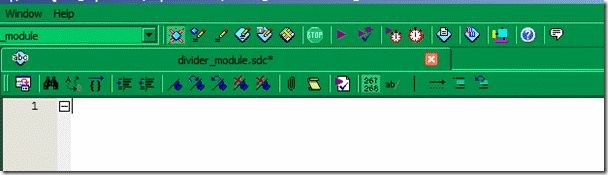

2.6 约束时钟

对TimeQuest而言,约束的大概意思是“注意什么,或者干什么”,接近的意思是“利用命令再现分析环境”有关这一点它与Modelsim非常类似,因为Modelsim是利用描述语言(其中包括验证与综合)再现仿真环境。所谓“约束时钟”就是告诉TimeQuest,某个设计“到底有什么样的时钟?”。好了,让我们开始2.5章节的实验一吧。

实验一的网表配置如下所示,这种作为没有什么特殊的意思。

create_timing_netlist -post_map -model slow -zero_ic_delays

实验一所使用的 CLK_Sig 是 100Mhz,50%占空比的典型时钟,我们有责任把这个信息告诉 TimeQuest,该过程就是俗称的“约束时钟”。

图2.6.1 打开同名sdc文件。

首先先确定在实验一的项目中TimeQuest已经被打开,然后在QuartusII中打开和实验一同名的 .sdc 文件,如图2.6.1所示。

图2.6.2 调出 create clock界面。

接着点击Edit => Insert Constraint => Create Clock ... 如图2.6.2.所示。

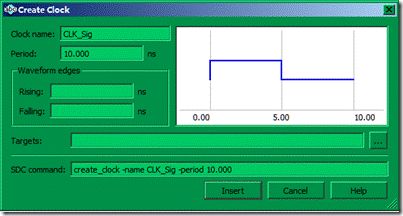

图2.6.3 Create Clock界面(时钟声明)。

然后会弹出一个 Create Clock 的窗口,在Clock name 随便输入一个名字,在这里笔者就输入 CLK_Sig,然后 Period 是 10.00ns 亦即 100Mhz频率的意思。至于Rising 和 Falling 是设置占空比,放空下是50%的占空比。完后点击 < ... > 取得 CLK_Sig对应的输入口。

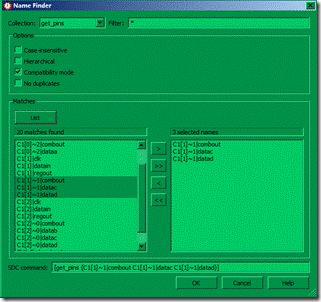

图2.6.4 寻找对应的基本单位。

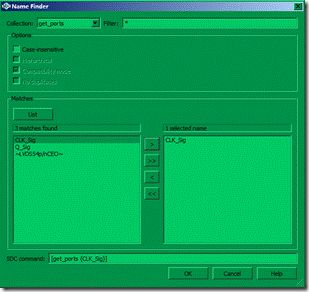

图2.6.4是经图2.6.3点击 < ... > 以后弹出的窗口。接下来我们要干的工作就是告诉TimeQuest,我们这个CLK_Sig 的目标对象是哪一个基本单位?

Collection 方面设置 get_ports亦即选择 port 基本单位。Filter < * > 表示没有过滤 ,然后点击 < List > 就会列出频模块的所有 port基本单位。 选择 CLK_Sig 然后,再点击" > " 把CLK_Sig 从左边加入右边,最后点击 < OK > 就行了。

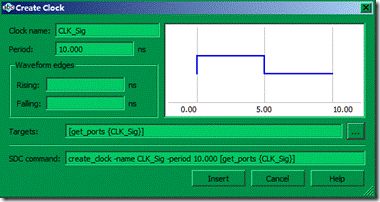

图2.6.5 对应目标为 port基本单位的 CLK_Sig。

图2.6.6 生成约束时钟的约束命令(约束代码)。

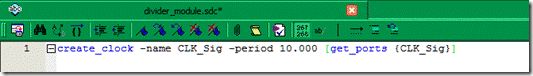

图2.6.3变成图2.6.5以后,再最后点击 < Insert > ,然后 create_clock -name CLK_Sig -period [get_ports{CLK_Sig}] 这条 SDC命令会自动添加并且显示在 Quartus II 中的 .sdc 文件里,结果如图2.6.6所示。

图2.6.7 在TimeQuest中约束时钟。

图2.6.1~6是笔者常用的方法,不过笔者也喜欢直接在 TimeQuest 中添加时钟约束,如图2.6.7所示那样,基本上过程都是一致的。

图2.6.8 在TimeQuest中保存sdc文件。

最后点击保存,这样 .sdc 文件就更新完毕,如图2.6.8所示。

图2.6.9 读取sdc文件。

接下来我们把换面切换到 TimeQuest,然后双击 Tasks 任务窗口中的 Read SDC File, 那么TimeQuest 就会从实验一中的 divider_module.sdc 文件中读取约束配置。到目前为止我们的 divider_module.sdc 仅包含如下这一个命令而已。

create_clock -name CLK_Sig -period 10.00 [ get_ports {CLK_Sig} ]

图2.6.10 更新网表。

当双点击 Read SDC File 以后,那么TimeQuest 就会知道“分频模块所使用的时钟信号 名为CLK_Sig 周期是10.00ns,而且目标对象是 CLK_Sig 这个port基本单位”。最后

双击 Update Timing Netlist 如图2.6.10所示,那么“约束时钟”的动作就会更新完毕。

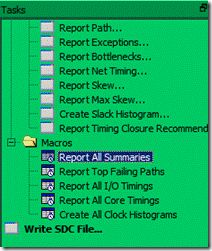

2.7 时序报告

在前一章节当中笔者为实验一约束了“100Mhz- 10ns 50%”的CLK_Sig。用另一句话来说,笔者“恐吓”TimeQuest说道:“喂!实验一的分频模块是用 10ns 50% 的CLK_Sig,而且CLK_Sig 的输入经由 CLK_Sig 输入端口”。在2.6章节的最后,我们双点击“Update Timing Netlist”过后就进入闲聊了 ...

在这一章节当中,我们的工作是要列出时序分析的结果,亦即时序报告。关于时须报告的“列出过程”都是因人而异的,这现象也常常让许多同学法问:“有没有固定的步骤?”好了,在这里就按照笔者的习惯来列出时序报告。

图2.7.1 列出时序简报。

首先需要列出所有的“时序简介”,在Task界面里双点击 < Report All Summaries > ,如图2.7.1所示,Report All Summaries 会列出所有简单的约束报告。

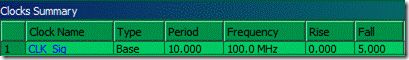

图2.7.2 时钟信号信息。

到目前为止,我们只是约束一个 CLK_Sig 而已,如图2.7.2所示。我们所约束的 CLK_Sig 是10ns 周期,50% 的占空比( Rise - 0.0 Fall - 5.0 )。因此TimeQuest已经知道该实验有一个名为 CLK_Sig周期是10ns的时钟信号。

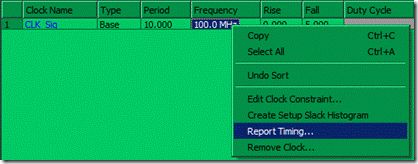

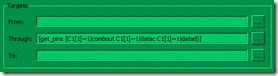

图2.7.3 调出 Report Timing界面。

接下来我们要报告出,在实验一的网表中,所有和 CLK_Sig 有关的网表基本单位。如图2.7.3所示,在CLK_Sig 的简介中,“右键点击”然后会弹出一个窗口,最后点击

< Report Timing ... > 就可以了。

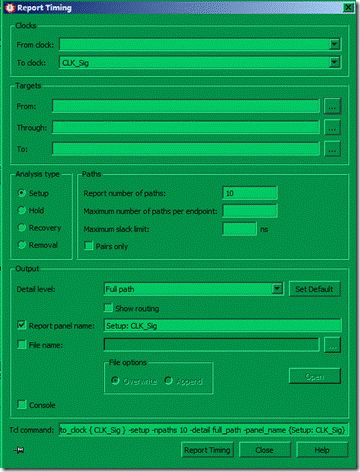

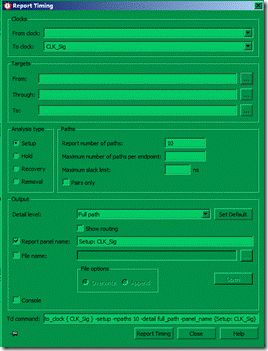

图2.7.4 Report Timing的基本界面。

图2.7.4 是 Report Timing 的基本界面,对于第一次遇见它的朋友来说,可能会吓了一跳 ... Report Timing几乎是最常用的工具之一,它主要分析 setup, hold,recovery 还有 removal等时序结果(暂时先不管 recovery 和 removal)。

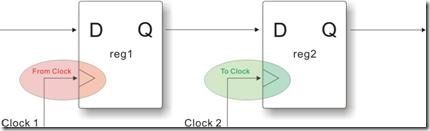

图2.7.5 From和To与基本单位。

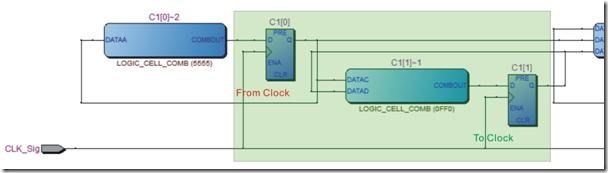

我们知道TimeQuest的模型只有在“一对节点”的情况下才能工作。From Clock 在某种意义上是指 reg1的提供时钟,亦即源时钟;反之 To Clock 在某种意义上是指 reg2的提供时钟,亦即目的时钟,如图2.7.5所示。

图2.7.6 节点C1[0]~C1[1]的from clock 与 to clock。

如果以实验1为例,在TMV视图当中,矩形中有一对节点,亦即C1[0]~C1[1](图2.7.6)。其中C1[0]是Reg1,反之C1[1]是Reg2,Reg1和Reg2它们同是使用 CLK_Sig。在这里我们需要知道一个TimeQuest的硬道理“TimeQuest模型需要一对节点才能成立”。假设笔者在 From Clocks 中输入 CLK_Sig,那么这一对节点C1[0]~C1[1] 就会被牵扯进来,同样的道理,当笔者在To Clock 中输入 CLK_Sig ,那么C1[0]~C1[1]也会被牵扯进来。

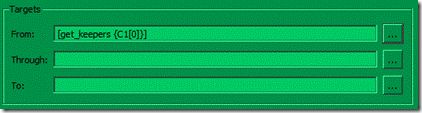

图2.7.8 target 的对应选项。

图2.7.8中的Targets有3个选项,亦即 From,Through 和 To,选项的功能如字面上的意思。Targets 是某个节点的基本单位,以实验一为例,如果笔者在 From 中输入 C1[0]如图2.7.8所示,该动作就是把 C1[0]有关联的节点都列出来 (也可以看成是把Reg1有关的“节点”都关联进来)。

图2.7.9 实验的所有节点。

图2.7.10 实验一部分节点(from 对应 c1[0])。

我们知道实验一中的分频模块,主要由6对节点组成,如图2.7.9所示。那么和C1[0] 有关联的节点如图2.7.10所示。

图2.7.11 Through的对应选线。

其外,Through的意思如字面上一般——经由,简单说就是“经过什么”。如图2.7.11所示,C1[0]~C1[1]节点之间就有 “C1[1]~1”这个组合逻辑。假设笔者在Through中输入 “C1[1]~1|combout,C1[1]~1|datac,C1[1]~1|datad”,救过就是把C1[1]~1 组合逻辑有关的节点关联进来。

图2.7.12 与C1[1]~1|combout,C1[1]~1|datac,C1[1]~1|datad有关的节点。

结果会如图2.7.12所示,与C1[1]~1 组合逻辑有关联的节点只有 C1[0]~C1[1]和C1[1]~C1[1]而已。至于To 是From的反面的意思,笔者就不详细介绍了,读者可以把它看成“把Reg2有关的节点都关联进来”。

图2.7.13 时序分析选项。

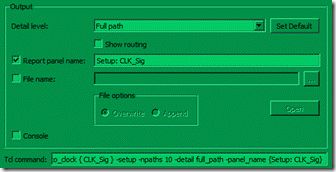

图2.7.13是Analysis type 的界面。TimeQuest的模型除了用来分析 Setup 建立关系, Hold 保持关系以外,还有 Recovery 和 Removal。Recovery /Removal 和 Setup /Hold 的差别就在于异步与同步之分,我们暂时不谈它们。假设笔者要列出(Setup)建立关系的分析结果,那么只要使能 Setup就行。

图2.7.14 output选项。

图2.7.14是Output的界面,基本上没有好介绍的,默认下就足够了。最下面的是 Tcl command命令,看看就好了不要太认真。

图2.7.15 Report Timing 界面。

再一次,笔者简单介绍一下图2.7.15当前的配置:

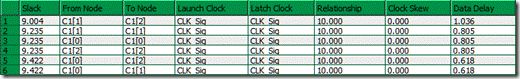

在Clocks界面中,To Clock输入了 CLK_Sig ,根据实分频模块,其中的6对节点都是使用同样的 To Clock , 换句话说就是把实验一的全部“6对节点”都关联进来;而Targets 空空如也,默认下这也表示把“所有节点”都关联进来的意思:在Analysis type 中,Setup被使能,换句话说就是分析建立关系。好了,关于 Report Timing的界面,笔者介绍得差不多了,笔者是时候点击 <Report Timing>。

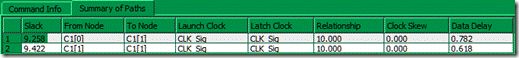

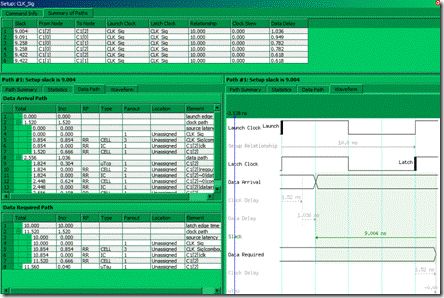

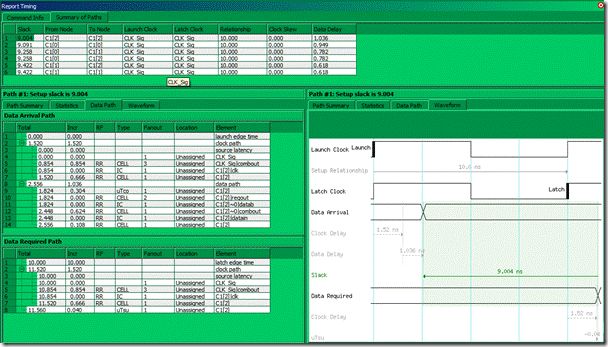

图2.7.16 详细的setup时序报告。

最后就会出现如图2.7.16所示的详细setup时序报告。

===================================================================

好了,先给自己一段消化的小时间吧 ... 基本上要列出时序报告是没有什么固定的步骤,但是对于一些懒人来说(笔者)最喜欢就是先列出“全部约束—Report All Summary”

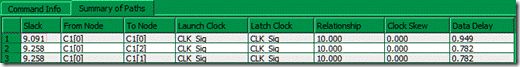

,然后再“ Report Timing”直接把 CLK_Sig 有关的节点都列出来。就这样,要报告出建立关系的结果,就在Analysis Types 中使能 setup:反之,要报告出保持关系的结果,就在Analysis Types 中使能 hold即可。

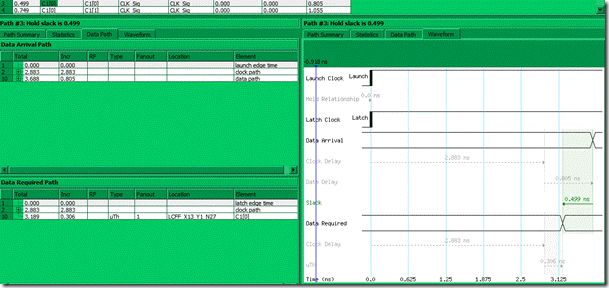

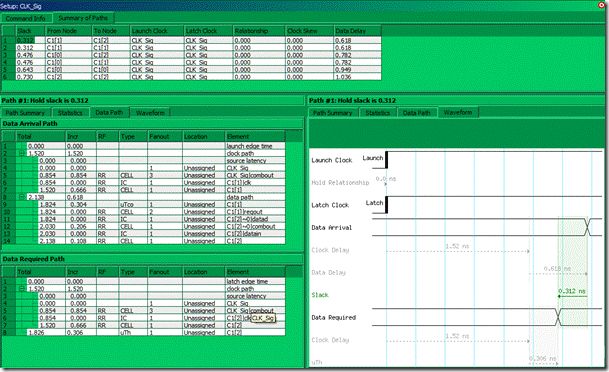

图2.7.17 详细的setup时序报告。

图2.7.18 详细的hold时序报告。

最后我们来看看实验一中的分频模块的建立关系和保持关系的时序报告,如图2.7.17~18所示,建立余量和保持余量均为正值,换句话说实验一的时序已经合格。

总结:

在这一章节当中笔者简单并且详细的讨论关于“TimeQuest如何使用自身的模型去分析时序是否合格”,“网表”,“约束”,“TimeQuest的使用步骤”和“时序报告”等概念。第二章的一切一切,笔者还是在讨论一些基本的概念而已。

在笔者的眼中,要入门TimeQuest明白一些最基本的内容是关键的部分。TimeQuest虽说它是一个笨蛋的工具,但是设计者是用什么思维去设计它,这是学习TimeQuest,也是掌握TimeQuest的重点。以前,笔者初次接触TimeQuest的时候,一直在“如何使用TimeQuest”这个大门外打转,结果笔者打圈圈3/4年。

那时候的笔者虽然知道“保持余量”的概念,但是却对求出“保持余量”的公式充满着问题 .... 因为笔者还不知道如何使用屁股去分析保持余量的公式。此外,笔者也对“TimeQuest如何用自身的模型”去分析一个设计,充满着许多问号。最后还有一个难题就是“笔者没有网表的大致定义 ”.....

“网表的定义”是把所有概念联系起来的重要“中间人”,只有知道网表的位置和定义,那么所有东西都可以串联起来了,这种感觉如同工藤新一的头部穿过电流那样。

好了,笔者不废话了,最后来个简单的总结吧:

1. 一个硬模型基本上是由网表和软模型经过编译组成的。

2. TimeQuest是一个分析网表“是否合格”的工具(读者可以看成是网表的仿真工具)。

3. 其中网表的生成需要参考软模型。

4. 网表有质量之分。

5. “约束”的定义,在这个章节当中是“告诉TimeQuest干什么,或者注意什么”。

6. TimeQuest是用模型逐个去分析所有节点之间的保持|建立关系。

7. Technology Map Viewer 和TimeQuest有关系。

8. 可以把sdc看成是硬模型的激励文本。

9. TimeQuest没有固定的使用步骤。

10. “Report Timing”是一个很好用的工具。

嗯,就是这些而已。更多有趣的内容和学习,我们下一章再见。