ENC28J60 驱动开发要点

转载

摘要:在嵌入式系统中,以太网控制器通常也是研究热点之一,MicroChip公司的ENC28J60在嵌入式系统中应用价值较高,该芯片集成了MAC控制器和PHY,使用SPI接口,适合在引脚资源比较紧张的嵌入式系统中加入以太网连接功能,本文主要介绍了MicroChip公司的ENC28J60控制器的初始化及其编程相关的注意和要点,并针对开发中可能遇到的一些问题进行了探讨。

关键字: ENC28J60编程

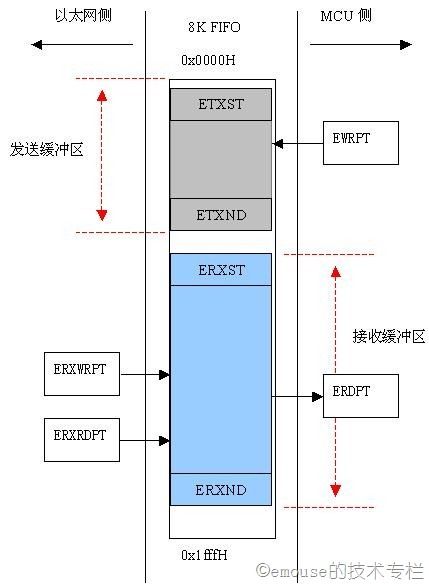

1.以太网数据缓冲区(8K)读写/地址控制REG的相关作用:

注意,这些REG除EPKTCNT外都为16bits,以太网数据缓冲区地址为:0000h~1FFFh

1).ERDPT(分为H/L两个)MCU读缓冲器指针:

--手册P28,MCU读取缓冲区数据时,每次实际读取的地址由该REG保存.

2).EWRPT(分为H/L两个)MCU写缓冲器指针:

--手册P29,MCU向缓冲区写入数据时,每次实际写入的地址由该REG保存.

3).ERXRDPT(分为H/L两个)接收读指针:

--手册P17,P33, 定义禁止接收硬件写入的FIFO 中的位置。 在正常操作中,接收硬件(指网络接口方向)将数据顺序写入,直到ERXRDPT 所指单元(不包括该单元)。注意,该REG与释放缓冲区的空间操作相关.

4).ERXWRPT(分为H/L两个)接收写指针:

--手册P17,P33, 定义接收硬件收到的数据写入的FIFO 中的具体位置。 在正常操作中,接收硬件(指网络接口方向)将数据顺序写入ERXWRPT所指单元。注意,该REG为”只读”,且与释放缓冲区的空间操作相关.

5).ETXST(分为H/L两个)发送缓区起始地址:

--手册P17,在整个以太网数据缓冲区中,定义待发送数据区的首地址

6).ETXND(分为H/L两个)发送缓区结束地址:

--手册P17,在整个以太网数据缓冲区中,定义待发送数据区的尾地址

7).ERXST(分为H/L两个)接收缓区起始地址:

--手册P17, 在整个以太网数据缓冲区中,定义接收硬件可以写入数据的缓冲区首地址.

8).ERXND(分为H/L两个)接收缓区结束地址:

--手册P17, 在整个以太网数据缓冲区中,定义接收硬件可以写入数据的缓冲区尾地址.

9).EPKTCNT(8bits)以太网数据包计数器:

--手册P43,P45,当硬件允许的时候,每次收满一个以太网数据包(>64bytes)时,EPKTCNT+1,最大值为255,此时不论缓冲是否还有空闲也不再接收数据.每次前移ERXRDPT(即释放接收缓冲区操作)后,EPKTCNT-1,最小值为0.

注意:在以上9个REG中,名称中带有”X”的规定的地址都是给以太网接收器使用的(即:从以太网一侧访问8K缓存),只有ERDPT和EWRPT是MCU通过SPI接口访问8K缓冲区用的.访问的关系如下图:

其中 ERXWRPT和 ERXRDPT可以指向同一地址,应为ENC28J60接收时会从ERXWRPT指向的地址一直写到ERXRDPT指向的地址前一个空间(即手册所谓的”不包括ERXRDPT指向的单元”).此时整个接收缓冲区全部可用.8K空间中,实际用来进行发送缓冲的空间由寄存器组ETXST和ETXND确定,实际用来进行接受缓冲的空间由寄存器组ERXST和ERXND确定.显然,8K空间中可以多余一些什么也不用的位置.

2.MII和PHY寄存器的操作:

PHY寄存器负责对PHY接口的配置,MCU不能直接从SPI接口访问这些REG,但是主控可以通过MAC组的一组特殊控制REG来访问PHY控制寄存器,MAC组中的这些特殊的控制REG即称为MII接口寄存器.

对MCU而言,不会有直接访问PHY的可能,所有的PHY操作都必须经过MII寄存器来完成.还需注意,PHY有部分为16bits,写入的时候必须先写低8bits,当写入高8bits的时候控制的设定将立即起效.

3.控制器结构和初始化过程

初始化的过程应该是:

初始化ETH组REG--->初始化MAC组REG--->通过MII初始化PHY组REG(需要查询硬件稳定)

Step1:ETH组控制寄存器初始化

1).EIE初始化

--手册P67,以太网中断允许控制

主控SPI写控制REG(WCR),发出2byte,REG地址0h1b,数据为:

0b010\11011+0bAAAAAAAA(A--8bits实际数据)

2). EIR查询

--手册P68,以太网中断状态获取

主控SPI读控制REG(RCR),发出2byte, REG地址0h1C,数据为:

0b010\11100+0bXXXXXXXX(X—为了保持SPCK发出的无效数)

读取的有效数据在SPI发送的第二个有效字节返回.

3).ESTAT查询

--手册P66,获得PHY就绪状态(以及以太网的各种错误状态)

主控SPI读控制REG(RCR),发出2byte, REG地址0h1D,数据为:

0b010\11101+0bXXXXXXXX(X—为了保持SPCK发出的无效数)

读取的有效数据在SPI发送的第二个有效字节返回.

4).ECON2初始化

--手册P16,IC节能控制,数据包指针寄存器控制

主控SPI写控制REG(WCR),发出2byte,REG地址0h1E,数据为:

0b010\11110+0bAAAAAAAA(A--8bits实际数据)

5).ECON1初始化

--手册P15,特别注意其中对BANK0~3的选择位,写不同的控制REG需要多次改变Bank0~3的选择.

--手册P16,IC节能控制,数据包指针寄存器控制

主控SPI写控制REG(WCR),发出2byte,REG地址0h1F,数据为:

0b010\11111+0bAAAAAAAA(A--8bits实际数据)

6).ERXFCON接收过滤器初始化

--手册P48,

首先需要写ECON1,选择访问Bank1,此后

主控SPI写控制REG(WCR),发出2byte,REG地址0h18,数据为:

0b010\11000+0bAAAAAAAA(A--8bits实际数据)

Step2:ETH组地址寄存器初始化

1).寄存器组ETXST和ETXND就位

--定义发送缓冲区范围

ETXSTL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h04(L),0h05(H),数据为:

0b010\00100+0bAAAAAAAA(A--8bits实际数据,ETXSTL)

0b010\00101+0bAAAAAAAA(A--8bits实际数据,ETXSTH)

ETXNDL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h06(L),0h07(H),数据为:

0b010\00110+0bAAAAAAAA(A--8bits实际数据,ETXNDL)

0b010\00111+0bAAAAAAAA(A--8bits实际数据,ETXNDH)

2). 寄存器组ERXST和ERXND就位

--定义接收缓冲区范围

ERXSTL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h08(L),0h09(H),数据为:

0b010\01000+0bAAAAAAAA(A--8bits实际数据,ERXSTL)

0b010\01001+0bAAAAAAAA(A--8bits实际数据,ERXSTH)

ERXNDL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h0a(L),0h0b(H),数据为:

0b010\01010+0bAAAAAAAA(A--8bits实际数据,ERXNDL)

0b010\01011+0bAAAAAAAA(A--8bits实际数据,ERXNDH)

3). ERXWRPT和 ERXRDPT就位

--注意其范围要随应用中定义的数据帧的大小变化,且每次处理完接收以后要操作ERXRDPT释放空间.

ERXWRPTL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h0C(L),0h0D(H),数据为:

0b010\01100+0bAAAAAAAA(A--8bits实际数据, ERXRDPTL)

0b010\01101+0bAAAAAAAA(A--8bits实际数据, ERXRDPTH)

注意:初始化时, ERXWRPTL/H一般取等于ERXSTL/H

ERXRDPTL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h0E(L),0h0F(H),数据为:

0b010\01110+0bAAAAAAAA(A--8bits实际数据, ERXRDPTL)

0b010\01111+0bAAAAAAAA(A--8bits实际数据, ERXRDPTH)

注意: ERXRDPT与ERXWRPT的差值应该大于1个以太网数据帧的长度,如果ERXRDPT=ERXWRPT则整个接收缓冲区可以连续使用.

4).根据MCU从以太网接收数据的需要,ERDPT就位

ERDPTL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h00(L),0h01(H),数据为:

0b010\00000+0bAAAAAAAA(A--8bits实际数据,ERDPTL)

0b010\00001+0bAAAAAAAA(A--8bits实际数据,ERDPTH)

5).根据MCU向以太网发送数据的需要,EWRPT就位

EWRPTL/H

主控SPI写控制REG(WCR),发出4byte,REG地址0h02(L),0h03(H),数据为:

0b010\00010+0bAAAAAAAA(A--8bits实际数据,EWRPTL)

0b010\00011+0bAAAAAAAA(A--8bits实际数据,EWRPTH)

Step3:MAC组寄存器初始化

(注意:MAC组寄存器映射在Bank2/3,访问前需要调整ECON1中的BSEL0/1)

如果初始化发生在上电复位之后,初始化前必须查询ESTAT.CLKRDY(手册P33)

MAC寄存器的初始化顺序不重要,一般按照(手册P34)说明的顺序:

1).MACON2.MARST位清0—MAC初始化退出.

主控SPI写控制REG(WCR),发出2byte,REG地址0h01(Bank2)数据为:

0b010\00001+0bAAAAAAAA(A--8bits实际数据)

2).MACON1初始化

--MARXEN位置1使能MAC接收.

--启动全双工方式,TXPAUS和RXPAUS位置1.

主控SPI写控制REG(WCR),发出2byte,REG地址0h00(Bank2)数据为:

0b010\00000+0bAAAAAAAA(A--8bits实际数据)

3).MACON3初始化

--将PADCFG.TXCRCEN.和FULDPX位置1,使能帧自动填充,使能自动CRC生成.(要注意其中FRMLNEN位的使用).

主控SPI写控制REG(WCR),发出2byte,REG地址0h02(Bank2)数据为:

0b010\00010+0bAAAAAAAA(A--8bits实际数据)

4).MACON4一般保持默认值

5).MAMXFL(16bitsREG,分为H/L两部分)就位

--确定网络帧的最大字节数(暂定义应用中的帧长度都为64bytes).

主控SPI写控制REG(WCR),发出4byte,REG地址(Bank2)0h0A(L),0h0B(H),数据为:

0b010\01010+0bAAAAAAAA(A--8bits实际数据, MAMXFLL)

0b010\01011+0bAAAAAAAA(A--8bits实际数据, MAMXFLH)

6).MABBIPG就位

--背对背包时间间隔就位,全双工时置入值固定为15h

主控SPI写控制REG(WCR),发出2byte,REG地址0h04(Bank2)数据为:

0b010\00100+0b00010101

7).MAIPGL就位

--非背对背包时间间隔就位, 全双工时置入值固定为12h(L)和0Ch(H)

主控SPI写控制REG(WCR),发出4byte,REG地址(Bank2) 0h06(L)0h07(H)

数据为:

0b010\00110+0b00010010(MAIPGLL)

0b010\00111+0b00001100(MAIPGLH)

注意:正常使用时,应该采用全双工方式,此时MACLCON1/2可保持默认值

8).MAC地址就位(映射在Bank3)

--将6字节的MAC地址写入寄存器组:MAADR0~MAADR5.

主控SPI写控制REG(WCR),发出6byte,REG地址(Bank3) 0h00~0h05数据为:

0b010\00000+0bAAAAAAAA(A--8bits实际数据,MAADR1)

0b010\00001+0bAAAAAAAA(A--8bits实际数据,MAADR0)

0b010\00010+0bAAAAAAAA(A--8bits实际数据,MAADR3)

0b010\00011+0bAAAAAAAA(A--8bits实际数据,MAADR2)

0b010\00100+0bAAAAAAAA(A--8bits实际数据,MAADR5)

0b010\00101+0bAAAAAAAA(A--8bits实际数据,MAADR4)

Step4:PHY组寄存器初始化

注意: 如果初始化发生在上电复位之后,初始化前必须查询ESTAT.CLKRDY(手册P33)

(注意:PHY组寄存器的MII接口REG映射在Bank2,访问前需要调整ECON1中的BSEL0/1)

与PHY相关的MII寄存器共有6个分别是:

MICON—手册P21,MII控制REG

MICMD—手册P21,MII命令REG

MIREGADR—手册P19,PHY访问地址REG

MIWRL/H—手册P19,PHY写数据REG高/低,注意,该REG组必须先写入L再写入H,写入H会触发MII控制事件.

MIRDL/H—手册P19,PHY读数据REG高/低.在读之前应将MICMD的MIIRD位置1,这样可以触发PHY事件且使MISTAT.BUSY=1,当MII获得了PHY值以后,MIIRD不会自动清0.所以在查询MISTAT.BUSY=0以后要手动清0.

MISTAT—手册P22,MII状态REG,反映PHY的状态,在读/写PHY之前应该先查询此REG当MISTAT.BUSY=0时才可以进行操作.

根据手册P38,一般只需要配置3个PHY模块并且要查询PHY的工作状态

1).PHCON1的手动操作

--虽然可以通过外接LED的方式确定半双工/全双工方式,但是手工设置PHCON1.PDPXMD位的值是更加安全的方法,同时也要手工修改MACON3中的FULDPX位.

--PHY地址00h,通过MII操作时,流程在手册P19

主控SPI写控制REG(WCR),发出2byte*3,给MIREGADR,MIWRL/H 3个REG

地址(Bank2)0h14(MIREGADR),0h16(MIWRL),0h17(MIWRH),数据为:

0b010\10100+0b00000000(字节1—MIREGADR的地址,字节2—写入PHCON1的地址00h)

0b010\10110+0bAAAAAAAA(字节1—MIREGADR的地址, 字节2—写入MIWRL的8bits实际数据—L字节应该是写入PHCON1的实际值)

0b010\10111+0b00000000(字节1—MIREGADR的地址, 字节2—写入MIWRH的8bits实际数据,在这里发出的数据无效,仅触发PHY事件).

写入后,MII自动触发PHY事件,MISTAT.BUSY自动置1.

2).PHLCON的设置

--根据外结LED电路的实际结构,有可能要修改这个REG.

--PHY地址00h,通过MII操作时,流程在手册P19

主控SPI写控制REG(WCR),发出2byte*3,给MIREGADR,MIWRL/H 3个REG

地址(Bank2)0h14(MIREGADR),0h16(MIWRL),0h17(MIWRH),数据为:

0b010\10100+0b00010100(字节1—MIREGADR的地址,字节2—写入PHLCON的地址14h)

0b010\10110+0bAAAAAAAA(字节1—MIREGADR的地址, 字节2—写入MIWRL的8bits实际数据—L字节应该是写入PHLCON的实际值)

0b010\10111+0b00000000(字节1—MIREGADR的地址, 字节2—写入MIWRH的8bits实际数据,在这里发出的数据无效,仅触发PHY事件).

写入后,MII自动触发PHY事件,MISTAT.BUSY自动置1.

3).PHCON2的设置

--一般全双工状态时可以保持其默认值,但是注意其中的TXDIS位可以关闭PHY的硬件发送.

主控SPI写控制REG(WCR),发出2byte*3,给MIREGADR,MIWRL/H 3个REG

地址(Bank2)0h14(MIREGADR),0h16(MIWRL),0h17(MIWRH),数据为:

0b010\10100+0b00000000(字节1—MIREGADR的地址,字节2—写入PHCON2的地址11h)

0b010\10110+0bAAAAAAAA(字节1—MIREGADR的地址, 字节2—写入MIWRL的8bits实际数据—L字节应该是写入PHCON2的实际值)

0b010\10111+0b00000000(字节1—MIREGADR的地址, 字节2—写入MIWRH的8bits实际数据,在这里发出的数据无效,仅触发PHY事件).

写入后,MII自动触发PHY事件,MISTAT.BUSY自动置1.

特别注意:PHY寄存器不能直接访问,需要通过MII寄存器的间接操作.

4).查询MISTAT状态

--主控SPI读控制REG(RCR),发出3byte, REG地址0h0A(Bank3),数据为:

0b010\01010+0bXXXXXXXX+0bXXXXXXXX(X—为了保持SPCK发出的无效数)

读取的有效数据在SPI发送的第三个有效字节返回.