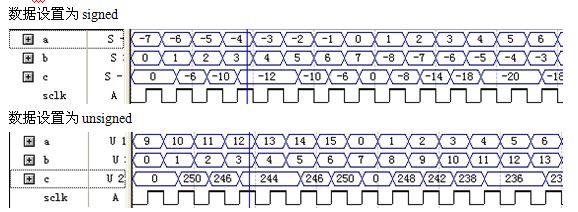

加减与有符号和无符号库

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mult_test is

port(sclk : in std_logic ;

a : in std_logic_vector(3 downto 0);

b : in std_logic_vector(3 downto 0);

c : out std_logic_vector(7 downto 0)

);

end mult_test;

architecture rtl of mult_test is

begin

process(sclk)

begin

if sclk'event and sclk = '1' then

c <= a * b;

end if;

end process;

end rtl;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity mult_test is

port(sclk : in std_logic ;

a : in std_logic_vector(3 downto 0);

b : in std_logic_vector(3 downto 0);

c : out std_logic_vector(7 downto 0)

);

end mult_test;

architecture rtl of mult_test is

begin

process(sclk)

begin

if sclk'event and sclk = '1' then

c <= a * b;

end if;

end process;

end rtl;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mult_test1 is

port(sclk : in std_logic ;

a : in std_logic_vector(3 downto 0);

b : in std_logic_vector(3 downto 0);

d : out std_logic_vector(3 downto 0)

);

end mult_test1;

architecture rtl of mult_test1 is

begin

process(sclk)

begin

if sclk'event and sclk = '1' then

d <= a + b;

end if;

end process;

end rtl;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity mult_test1 is

port(sclk : in std_logic ;

a : in std_logic_vector(3 downto 0);

b : in std_logic_vector(3 downto 0);

d : out std_logic_vector(3 downto 0)

);

end mult_test1;

architecture rtl of mult_test1 is

begin

process(sclk)

begin

if sclk'event and sclk = '1' then

d <= a + b;

end if;

end process;

end rtl;