数字系统实验—第11-12周任务(认识数据存储芯片HM62256、IP核、LPM开发流程和平台、 IIC串行总线时序分析)

数字系统实验—第11-12周任务—硬件语言描述训练3

- 任务书(18级在家实验,可能不同)

-

- 0.简介

- 1. 认识数据存储芯片HM62256、IP核、LPM开发流程和平台

-

- 实操:C级任务(80%)

- 实操:B级任务(90%)

- 实操:A级任务(100%)

- 2. IIC串行总线时序分析

-

- 实操:S级任务(110%)

- 3. 提交

- 数字系统实验——硬件语言描述训练3

-

- 一、C级任务

-

- 1、 设计HM62256测试电路并对其仿真验证

- 2、 依据上述HM62256的功能,定制开发一个1-port RAM的IP核

- 二、B级任务

-

- 1、 html文件波形分析(html波形图)

- 2、 仿真验证

- 三、A级任务

- 四、S级任务

-

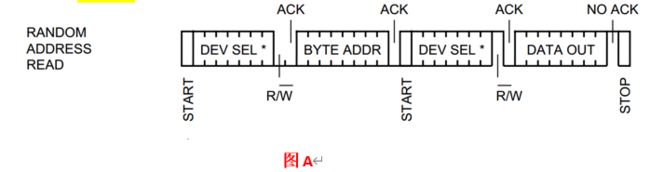

- 1、阅读AT24C02并理解图A IIC总线读取任意地址数据的时序

- 2、利用proteus仿真51单片机读取非易失存储器24C02C,掌握读写操作

- 3、对应示波器波形如下:

- 4、VHDL设计基于IIC总线的读取非易失存储器24C02C任意地址数据的接口电路

代码链接:pan.baidu.com/s/1JUZ_bwErDEXyXpPPo8H5FA

提取码:82i5

任务书(18级在家实验,可能不同)

0.简介

理解IP核和LPM库开发流程、数据存储HM62256、RAM和FIFO的IP核、分层次编写VHDL完成FPGA片内外数据存储验证。

分层次编写VHDL完成FPGA片内外数据存储,验证平台,IIC总线读写与非易失存储(可选)。

1. 认识数据存储芯片HM62256、IP核、LPM开发流程和平台

时间:

1至2周

步骤:

阅读课程平台上“VHDL语言描述训练3”,掌握LPM开发流程。

阅读理解手册HM62256.PDF中的概述、引脚定义、框图、功能表、读写操作与参数表。

课程平台上下载资料。

实操:C级任务(80%)

-

设计HM62256测试电路并对其仿真验证。

① 认真阅读HM62256的数据手册。

② 新建Proteus工程,添加器件HM62256、开关、电阻、LED_YELLOW、电源、地线、三态门74HCT244,并设计好HM62256的功能验证电路。

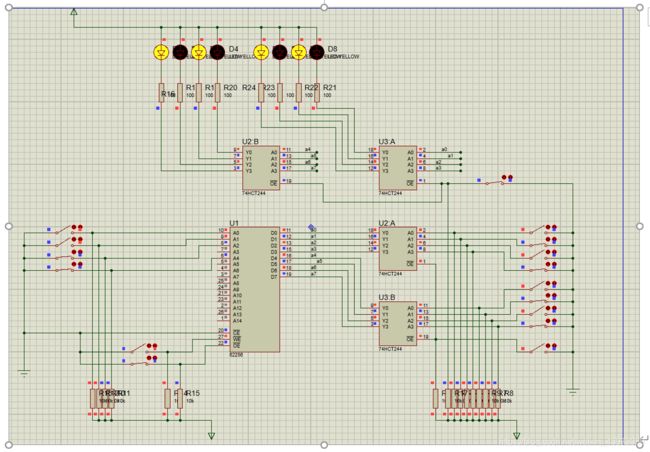

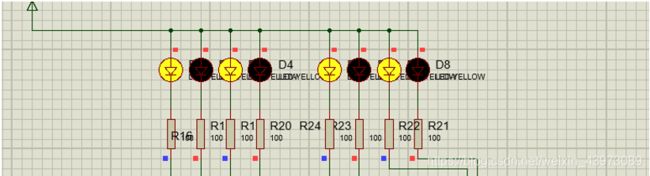

③ 参考电路如下图1

④ 仿真验证实现HM62256的读写功能,记录操作步骤和实验结果。

⑤ 测试电路设计要求:地址线4位、数据线8位,数据输出部分的总线设计。 -

阅读教材P205“参数化只读存储器”,依据上述HM62256的功能,定制开发一个1-port RAM的IP核。

① 分析并说明生成目录下的html波形报告

② 仿真验证其读写功能,记录波形图并说明。

实操:B级任务(90%)

定制异步FIFO,参数如下图所示:

要求:

① 定制时选择芯片cycloneII系列。

② 分析并说明生成目录下的html波形报告。

③ 通过新建Quartus工程(芯片EP2C5T144C8)和VWF波形输入完成仿真验证功能。

注意:输入数据D【15…0】取低4位D【3…0】即可,D【15 …4】输入全为0,不然编译报错,芯片管脚不够。

实操:A级任务(100%)

在B级任务的基础上,VHDL编程设计专门状态机与2片异步FIFO来实现乒乓操作。

要求:仿真时设置写时钟频率为40MHz(25ns),读时钟频率为10MHz(100ns)。

乒乓操作是1种常常用于数据流控制的处理技巧,通过乒乓操作可以实现低速模块处理高速数据。数据缓冲模块可以是任何存储模块,这里使用的是FIFO。但是利用2个深度短FIFO相互切换,需要设计复杂的切换控制电路来保证数据不丢失。

操作过程,仅供参考,如下:

首先对第一个FIFO进行写操作,当第一个FIFO写满之后,切换到第二个FIFO进行写操作,同时对第一个FIFO进行读操作;在第二个FIFO写满之前,第一个FIFO早已读取完毕,此时再次对第一个FIFO进行写操作,同时对第二个FIFO进行读操作,两个FIFO按照一定节拍在读写之间转换,周而复始。

2. IIC串行总线时序分析

时间:

1周

实操:S级任务(110%)

借助proteus里的AT24C02C、示波器、IIC终端, 设计单片机(已提供HEX)主机电路发送单字节数据到24C02C的电路,并分析 IIC一帧完整波形。

步骤:

① 阅读AT24C0X手册功能说明,理解如图A所示IIC总线读取任意地址数据的时序。

② 图B中是利用proteus仿真51单片机读取非易失存储器24C02C的电路图,将所提供hex文件装入单片机中,启动仿真,掌握读写操作。

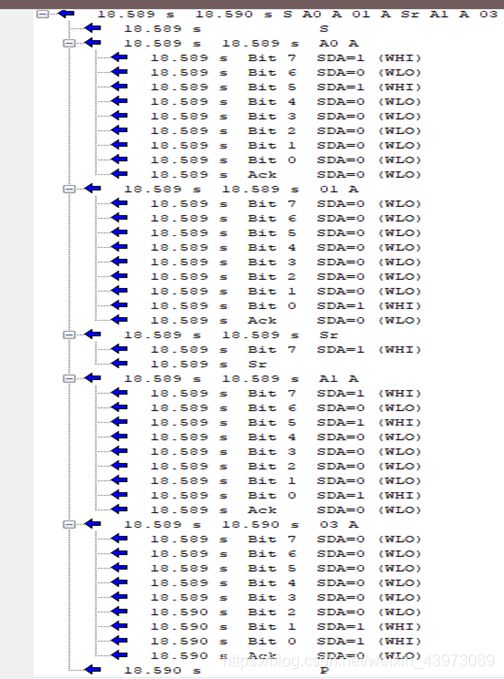

③ 参考IIC debugger中的数据如图C所示,抓取此时示波器中对应波形,逐条记录说明执行操作的过程。

④ 参考图D中的时序,以100KHz为时钟频率,VHDL设计一个基于IIC总线的读取非易失存储器24C02C任意地址数据的接口电路,以ep2c5t144c8为平台设计电路并完成仿真验证。

3. 提交

本次任务作业报告请于5月17日晚23:59分提交(PDF文件),文档正文不超过3页,大小不超过5MB,工程文件不超过5MB,要求如下:

数字系统实验——硬件语言描述训练3

实验日期:2020.5.4-2020.5.17

实验目标:理解IP核和LPM库开发流程、数据存储HM62256、RAM和FIFO的IP核、分层次编写VHDL完成FPGA片内外数据存储验证。

一、C级任务

1、 设计HM62256测试电路并对其仿真验证

1) 详细阅读HM62256资料,了解74HCT244的功能;

2) 根据参考图设计电路并将缺失的4位数据输入输出显示电路补充完整,电路图:

步骤:新建Proteus工程,添加器件HM62256、开关、电阻、LED_YELLOW、电源、地线、三态门74HCT244,并设计好HM62256的功能验证电路,连接好连线;

3) 仿真验证实现HM62256的读写功能

验证步骤如下:

①首先将控制地址开关打到3(可变),将控制输入数据的开关打到01010101(可变),闭合控制四个74HCT244使能OE的开关,将62256的状态置为等待状态(OE、WE均无效);

②开始运行,将62256的WE置为有效状态(此时写入62256),接着将WE置为无效,再将74HCT244的OE信号置为无效状态后使62256的OE信号有效(此时从62256的3地址处读处刚存入的数据);

③此时可以看到LED显示01010101的信号:

结果正确;

4) 实验结果分析

数据经过74HCT244写入62256的3地址内,接着关闭74HCT244,将62256内的数据读出并经另外的74HCT244用LED显示,显示结果正确,整个过程运行正确。

2、 依据上述HM62256的功能,定制开发一个1-port RAM的IP核

1) html文件波形分析(波形图):

图一仅显示了读操作,将memory文件的前三个地址的值读出;

图二显示了写操作,主要是上升沿处地址1从F1写为00,地址2从F2写为02,

2) 波形仿真:(mif文件中3、4位置初始为10、15)

150ns:上升沿读出3地址处的数据10;

100-200ns:we有效,150ns上升沿写入03到地址3处,之后250ns上升沿读出03;

300-500ns:对4地址进行同样的操作,450ns读入04,550ns上升沿读出04;

650-850ns:读出3地址处的数据03;

850-1000ns:读出4地址处的数据04;

读写验证正确;

二、B级任务

按照要求定制异步FIFO;异步FIFO读写时钟不同;宽16位,输出宽64位,深度512字;

输入低4位,高12位全固定为0;

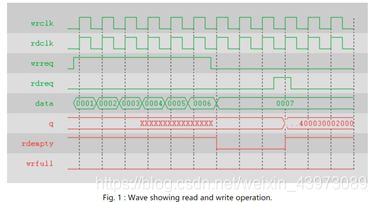

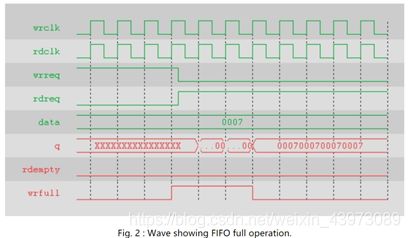

1、 html文件波形分析(html波形图)

两图为正常读写FIFO的波形,和FIFO达到满状态的读写波形;

首先分析正常读写的波形:在前6个上升沿,wrreg为有效状态,读入6个周期的data(0001->0006)到FIFO中(这6个信号最后才输出),接着在第10个上升沿,rd信号为有效,先入先出的输出输入的六个数据(0006->0001);

对于rdempty波形,我的理解是在读时非空rdempty置低位,读出数据;

而对于满状态wrfull读写波形:第四个上升沿,数据被写入FIFO直到满,wrfull信号置为有效,阻止FIFO继续读入数据,rdreg有效后数据被读出,wrfull满标志延后两个周期变为0;

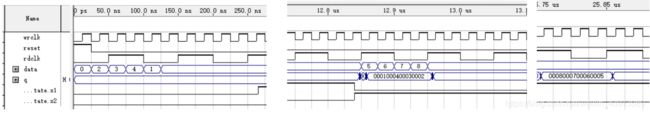

2、 仿真验证

分析:上图为最开始的几个周期,首先令wr有效512个周期,前8个周期输入为12345678(低四位),接着全是0;输入512个周期的输入到FIFO后,FIFO满(512word深),因此512周期后令wr无效、rd有效,读出先入先出FIFO数据;

下图即为输出情况,512个周期处显示wrfull为1,即FIFO满状态;此时令rd有效后延时一个周期开始输出数据,最先输入的4321(64位)、8765数据输出后一直输出后面输入的0;因此FIFO波形验证正确;

三、A级任务

在B级任务的基础上,VHDL编程设计专门状态机与2片异步FIFO来实现乒乓操作。

仿真时设置写时钟频率为40MHz(25ns),读时钟频率为10MHz(100ns);

两个FIFO交替进行读写操作,一个FIFO读时另一个进行写,写满后交替;

关键在于状态机的设计,根据两个FIFO的wrfull、rdempty空、满标志的变化进行读写信号的改变;

我的状态机共有三个状态,状态图如下:

其中,beg状态为初始时两块FIFO都为空,接下来x1、x2分别为写两片FIFO时的状态,beg状态在第一片FIFO的rdempty为0时直接进入写第一片的x1状态;

根据条件与状态图写的VHDL状态机见工程文件;

波形分析:首先,开始写1号FIFO,先输入0x2341后输入全0,延时几个周期后rdempty_1为0,进入X1状态;

接下来第二幅图为x1状态转变为x2状态,此时开始读1号FIFO,读出1432(低四位值)后读0,读操作正确;且此时开始写第二片FIFO,写入数据先写0x5678后写0;

第三幅图为x2状态转x1状态,此时开始读2号FIFO,读出8765(低四位)后读0,读操作正确;且此时开始写第一片FIFO;

这后两张波形图可以看出两个FIFO按照一定节拍在读写之间的正确转换;

四、S级任务

1、阅读AT24C02并理解图A IIC总线读取任意地址数据的时序

第一个start部分控制字节的R/W信号为低位(写操作),通过确认位确认后,发送字节地址给24C02来完成地址字节设置;字节地址发送完毕后,主器件接受确认信号产生起始条件(地址计数器设置完成写操作结束),再次发送控制字节(R/W位为1),24C02发出确认信号并开始发送数据字节,主器件不会再对数据传输确认但会产生终止条件。

2、利用proteus仿真51单片机读取非易失存储器24C02C,掌握读写操作

读写过程: 首先长按改变地址按钮使地址为02,此时如上左图所示显示初始值FF,接着长按数据输入按钮到02,接着长按存入数据按钮,此时如上右图所示显示存入的数据02;

3、对应示波器波形如下:

首先,SCL为高电平时SDA从高电平变为低电平表示起始条件产生;

接下来的9个SCL周期,数据在高电平时稳定,低电平时才改变数据,因此数据有效,9个周期输入的数据为1010000000,此时第8个周期R/W为0,说明此时为写操作,第9个周期也为0,ACK确认位确认;(控制写操作)

接下来的9个周期数据为000000010,ACK为0确认;(地址字节设置为1)

又产生一个起始条件;后9周期数据为1010000110,R/W为1,读操作,ACK为0确认;

再往后9个周期为000000110,此时读出地址1中的数据3,ACK不需确认;

最后SCL为高电平时SDA从低到高变化,终止条件;(整体实现了读取任意地址数据时序)

4、VHDL设计基于IIC总线的读取非易失存储器24C02C任意地址数据的接口电路

尝试着使用计数的方法参考网上普通iic的VHDL去实现去实现接口电路,但是却一直未能仿真出结果,代码附在源码包中;