Xilinx IP解析之Processor System Reset

一. IP概述

可参考Xilinx官网Processor System Reset Module概述,

以下翻译自官网此IP的概述。

产品描述:

Xilinx处理器系统复位模块允许客户通过设置某些参数来启用/禁用功能,从而根据自己的应用来定制设计。

主要功能和优势:

- 使异步外部复位(External Reset)信号与时钟同步

- 使异步辅助复位(Auxillary Reset)信号与时钟同步

- 可选外部/辅助复位信号是低电平有效还是高电平有效

- 可选复位信号需持续的最小脉宽

- 可选负载均衡

- DCM锁定输入

- 生成上电复位信号

二. IP产品手册

可参考Xilinx官网Processor System Reset Module文档

下载PG164 - Processor System Reset Module v5.0 Product Guide (v5.0)。

三. IP框图与信号端口

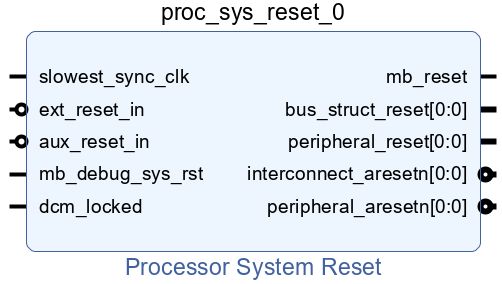

IP模块框图:

| 名称 | 方向 | 位宽 | 有效电平 | 说明 |

|---|---|---|---|---|

| slowest_sync_clk | I | 1 | - | 最慢同步时钟 |

| ext_reset_in | I | 1 | 可配置, 默认低电平有效 |

外部复位 |

| aux_reset_in | I | 1 | 可配置, 默认低电平有效 |

辅助复位 |

| mb_debug_sys_rst | I | 1 | 高 | 总线调试复位 |

| dcm_locked | I | 1 | 高 | dcm的locked信号 |

| mb_reset | O | 1 | 高 | 总线复位 |

| bus_struct_reset | O | 1 ~ 8, 默认1 |

高 | 总线高电平复位 |

| peripheral_reset | O | 1 ~ 16, 默认1 |

高 | 外设高电平复位 |

| interconnect_aresetn | O | 1 ~ 8, 默认1 |

低 | 互联低电平复位 |

| peripheral_aresetn | O | 1 ~ 16, 默认1 |

低 | 外设低电平复位 |

四. IP配置

部分配置选项解释:

外部/辅助复位有效宽度:配置外部复位信号有效电平需要持续几个时钟周期才被视为有效信号,才会有复位输出。

五. IP仿真

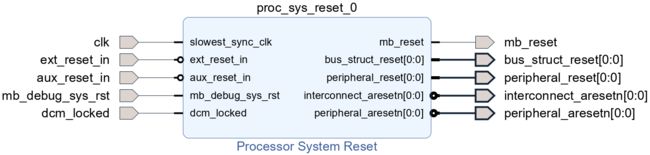

5.1 仿真框图

将proc_sys_reset IP核的端口信号引出,在testbench中进行赋值。

5.2 testbench

/*

* @Author : Xu Dakang

* @Email : [email protected]

* @Date : 2021-05-11 22:12:28

* @LastEditors : Xu Dakang

* @LastEditTime : 2021-05-15 14:38:12

* @Filename : procSysReset_tb.sv

* @Description : 测试proc_sys_reset IP核的特性

*/

module procSysReset_tb();

timeunit 1ns;

timeprecision 10ps;

logic clk;

logic ext_reset_in;

logic aux_reset_in;

logic mb_debug_sys_rst;

logic dcm_locked;

logic mb_reset;

logic [0:0]bus_struct_reset;

logic [0:0]peripheral_reset;

logic [0:0]interconnect_aresetn;

logic [0:0]peripheral_aresetn;

PrcoSysReset_system_wrapper PrcoSysReset_system_wrapper_inst(.*);

// 生成时钟

localparam CLKT = 4;

initial begin

clk = 0;

forever #(CLKT / 2) clk = ~clk;

end

localparam EXT_RESET_WIDTH = 4;

localparam N = 37;

initial begin

#(CLKT * N)

ext_reset_in = 0;

aux_reset_in = 1;

mb_debug_sys_rst = 0;

dcm_locked = 1;

#(CLKT * EXT_RESET_WIDTH) ext_reset_in = 1;

#(CLKT * 100) $stop;

end

endmodule

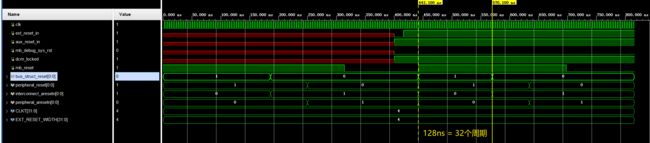

5.3 仿真波形

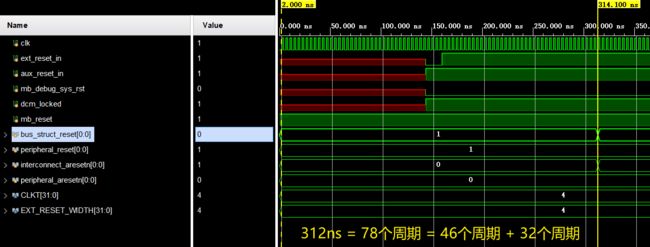

仿真条件1:N = 100,再使得ext_reset_in = 0(持续4个周期),dcm_locked = 1。波形如下图所示。

在初始阶段,输入为不定态X,此时所有复位输出均有效。

46个时钟周期后,bus_struct_rst和interconnect_areset最先失效。

再过16个时钟周期,peripheral_reset与peripheral_areset接着失效。

再过16个时钟周期,mb_reset最后失效。

然后,等到ext_reset_in = 0(持续4个周期),此时IP应检测到外部输入复位有效,

经过6个时钟周期后,各复位输出开始有效。

32个时钟周期后,bus_struct_rst和interconnect_areset最先失效。

再过16个时钟周期,peripheral_reset与peripheral_areset接着失效。

再过16个时钟周期,mb_reset最后失效。

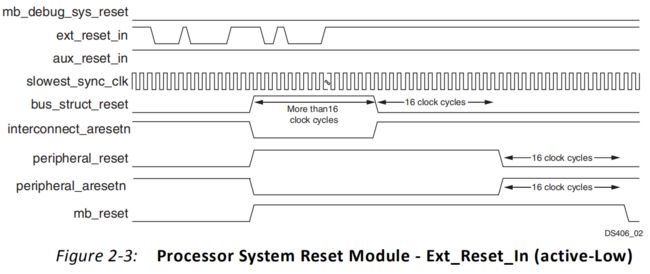

可见,5个输出信号的相对关系是确定的,如下:

bus_struct_rst与interconnect_areset持续32个周期有效后同时最先失效 -> 过16周期,peripheral_reset与peripheral_areset失效 -> 再过16周期,mb_reset最后失效

这正如IP产品手册第9页(下图)所说明的。

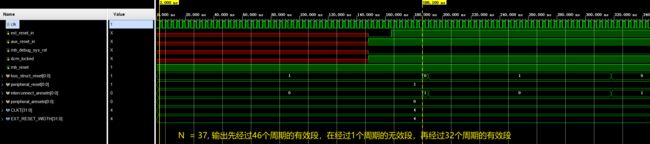

仿真条件2:N = 36,再使得ext_reset_in = 0(持续4个周期),dcm_locked = 1。波形如下图所示。

从仿真条件1,我们知道初始此IP有46个周期输出有效的复位信号,但这46个周期不是固定的,经过多次仿真发现,前4个时钟周期,此IP不检测复位信号,到第5个时钟周期,IP开始检测复位信号。所以在这里,初始经过N=36个周期后,外部复位开始低电平有效,此时初始复位输出将持续(46 + N - 4 = 78)个时钟周期。当N = 5 时,初始复位输出将持续(46 + 5 - 1 = 47)个时钟周期,以此类推。

仿真条件3:N = 37,再使得ext_reset_in = 0(持续4个周期),dcm_locked = 1。波形如下图所示。

可见,N = 37 时,bus和interconnect这个两个输出会出现(37 - 36 = 1)个时钟周期的无效段,另外三个输出则没有。以此类推 N = 100,bus和interconnect输出无效段会持续 100 - 36 = 64个时钟周期的无效段,此特性在仿真条件1中也可以得到印证。

仿真条件4:N = 37 + 16 + 16,再使得ext_reset_in = 0(持续4个周期),dcm_locked = 1。波形如下图所示。

此条件下,5个输出均出现无效段,其中,bus_struct_reset无效段持续一个时钟周期。

总结一下:此IP在初始阶段默认输出复位信号,信号宽度默认为46个时钟周期,如果在N(范围4~36)个时钟周期内,输入的复位有效,则输出复位信号宽度会延长N-4个时钟周期。超过36个时钟周期还没有有效的复位输入,输出复位信号会部分失效,超过36+16+16 = 68个周期没有有效复位输入,输出复位信号会全部失效。此时初始阶段结束,IP进入等待输入复位信号有效的阶段。

此后,IP检测到外部输入复位有效,经过6个时钟周期后,各复位输出开始有效。

32+X(这一段不确定,与输入复位信号有效宽度和有效次数有关)个时钟周期后,bus_struct_rst和interconnect_areset最先失效。

再过16个时钟周期,peripheral_reset与peripheral_areset接着失效。

再过16个时钟周期,mb_reset最后失效。

手册中,展示了ext_reset_in作为输入时,各输出的时序图,如下图所示。

另外,特别注意dcm_locked信号,此信号为低时表示时钟还未稳定,此时reset IP的复位输出全部有效,只有当dcm_locked信号为高时,reset IP的输出才受外部复位输入与辅助复位输入的控制。

5.4 仿真工程分享

ProcSysResetV5.0 Xilinx IP解析 Vivado 2020.2工程.7z

链接:https://pan.baidu.com/s/1Z-bNBqHFauf7kPDd1ysS3A

提取码:ttfy

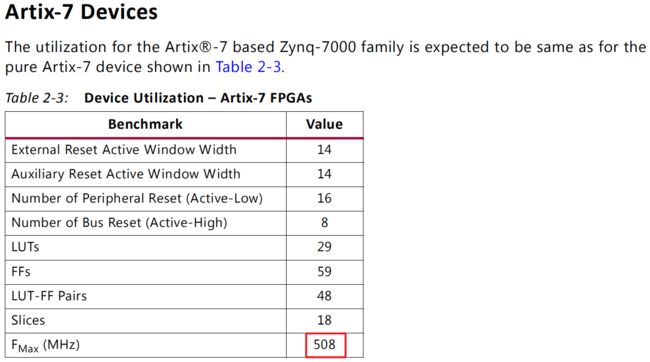

六. IP性能

对于7系列FPGA,性能最低的A7此IP核频率也可到508MHz。K7和V7可到704MHz。

七. IP使用示例

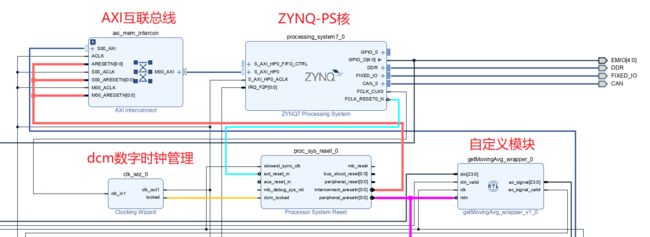

通常在Block Design中使用此复位IP,输出作为自定义模块,AXI总线等的复位信号。外部输入可自行给定,特别的对于ZYNQ,外部输入通常为PS侧提供的FCLK_RESET_N信号。如下图所示。

八. 总结

此IP使用简单,用作复位时,在不提供外部复位输入时,还是可以提供初始复位输出信号。使用时需要注意的是ext_reset_in和aux_reset_in的有效宽度必须大于设定的宽度才能被识别为有效复位输入,另外,各输出之间有固定的时序关系,此时序关系的目的是让不同功能模块开始工作的时间不同,使用时需要合理使用各输出。