一、IP核端口说明

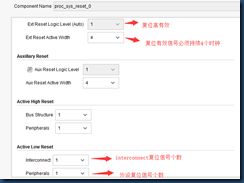

输入端口:

1、slowest_sync_clk:连接到系统中最慢的时钟

2、ext_reset_in:FPGA外部输入的复位信号

3、aux_reset_in:辅助复位信号,配置如ext_reset_in

4、mb_debug_sys_rst:microblaze核debug的reset输入信号

5、dcm_locked:PLL的locked信号,如果系统有PLL则连接其locked信号到这个端口,如果无,此端口置1或者悬空。

输出端口:

1、mb_reset:输出到microblaze的复位信号

2、Peripherals_aresetn:外设复位信号,低有效

3、Peripherals_areset:外设复位信号,高有效

4、Bus Structure Reset:一些桥接器的复位信号,暂时不理解,很少使用

5、Interconnect_aresetn:内部互联复位信号

二、IP核连接

三、IP核关键参数配置

四、IP核时序说明

上图说明只有一定长度的复位低信号才能触发IP核

上图高亮处是否表示在IP输出复位时,如果此时输入

再次有效,则又会产生一次复位,不是很理解

上图说明复位释放的顺序是桥接器、互联,然后到外设、

然后到CPU(micorblaze)

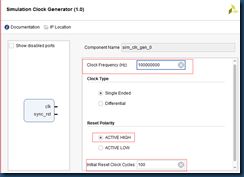

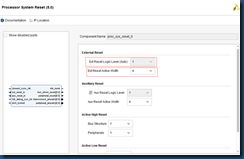

四、仿真工程

1、工程框图

2、IP配置

3、仿真结果

五、参考资料

1、PG164-Processor System Reset Module v5.0

2、https://china.xilinx.com/