- 2020-04-12每天三百字之连接与替代

冷眼看潮

不知道是不是好为人师,有时候还真想和别人分享一下我对某些现象的看法或者解释。人类社会不断发展进步的过程,就是不断连接与替代的过程。人类发现了火并应用火以后,告别了茹毛饮血的野兽般的原始生活(火烧、烹饪替代了生食)人类用石器代替了完全手工,工具的使用使人类进步一大步。类似这样的替代还有很多,随着科技的发展,有更多的原始的事物被替代,代之以更高效、更先进的技术。在近现代,汽车替代了马车,高速公路和铁路

- 2019-11-04复盘——飞来山上千寻塔,闻说鸡鸣见日升。

那一叶秋

1、大盘篇先上老图,看习惯了,也就知道走势了图1上证指数日线图还是那张老图,自己可以在自己的相关软件上画出来,快变盘了。2、个股篇未加仓、未减仓。分析量能的时候,突然发现这么一个东西:“放量突破年线,缩量回调。”合众科技日线图其实,最近的N只个股,在技术分析上,都到了变盘的临界时候。结合这么久的走势,特别是ZJH不断放开IPO的申请,本质上说是融资难度变大,或者说是为企业的融资开创便利。但现在市场

- 福袋生活邀请码在哪里填写,福袋生活app邀请码使用教程

小小编007

很多人下载福袋生活后,注册使用时需要填写邀请码。因为福袋生活是注册邀请制,所以首次使用填写邀请码才可以正常登录使用。福袋生活是广州市福袋生活信息科技有限公司旗下一家多元化社交电商导购平台,以APP为载体,社群为媒介,汇集衣食住行、吃喝玩乐生活服务板块,使用福袋生活可以领到淘宝,拼多多等电商平台的商品优惠券和返利,还可以兼职去分享赚钱。我为什么从福袋生活转到果冻宝盒呢?当然是因为福袋生活返利更高,注

- 如何选择最适合你的项目研发管理软件?TAPD卓越版全面解析

北京云巴巴信息技术有限公司

产品经理需求分析

在当今快速发展的科技时代,项目研发管理软件已成为企业不可或缺的重要工具。面对市场上琳琅满目的产品,如何选择一款适合自己团队的项目研发管理软件呢?本文将围绕项目研发管理软件的选择标准,重点介绍TAPD卓越版的特点、优势以及使用体验,让你更好地理解和选择适合自己的项目研发管理软件。项目研发管理软件的选择标准在选择项目研发管理软件时,我们需要考虑以下几个方面的因素:功能全面性:软件是否覆盖了从需求管理、

- OPENAIGC开发者大赛企业组AI黑马奖 | AIGC数智传媒解决方案

RPA中国

人工智能AIGC传媒

在第二届拯救者杯OPENAIGC开发者大赛中,涌现出一批技术突出、创意卓越的作品。为了让这些优秀项目被更多人看到,我们特意开设了优秀作品报道专栏,旨在展示其独特之处和开发者的精彩故事。无论您是技术专家还是爱好者,希望能带给您不一样的知识和启发。让我们一起探索AIGC的无限可能,见证科技与创意的完美融合!创未来AI应用赛-企业组AI黑马奖作品名称:AIGC数智传媒解决方案参赛团队:深圳市三象智能技术

- 《度五行》生活报报甲午62:不通痛苦,太通也痛苦,要健康快乐,需要通体舒畅。

YangduSam2021

220809壬寅戊申甲午,《度.生活五行》:天干土克水,水生木,木克土。地支寅申冲,寅午合。20220809,周二,兴大上海六班2512天,西交大2013上海班3212天,后TA15332天,度生活619天,今天拜访了一家有趣且当红产业的新创公司AK。AK一开始从事深海新能源储存与供电设备的研发生产制造,2年前开始做移动与家庭储能设备的研发生产制造。觉得有趣是因为这是笔者认知里用科技做降维打击的公

- “元宇宙”带不动Meta?基本业务已“后院起火”!小扎举步维艰!

链科天下

由于宏观经济疲软、市场动荡,“放缓”已经成为美国科技股的主线逻辑,曾风光无限的科技巨头Meta也开始一路下行、举步维艰。据彭博社报道,Meta已宣布计划裁员并重组团队以削减预算,这是该公司2004年成立以来首次大幅削减预算。此次裁员或受到业绩低迷的影响,Q2财报显示Meta业绩远不及预期,上市以来营收同比出现首次下滑,净利连续三季度下降。扎克伯格表示,“希望经济能够稳定下来,但从目前的情况来看并非

- 效率神器来了:AI工具手把手教你快速提升工作效能

kkai人工智能

人工智能学习媒体aichatgpt

随着科技的进步,AI工具已经成为提升工作效率的关键手段。本文将介绍一些实用的AI工具和方法,帮助你自动化繁琐的重复性任务、优化数据管理、促进团队协作与沟通,并提升决策质量。背景:OOPAI-免费问答学习交流-GPT自动化重复性任务Zapier:Zapier可以自动化多个应用程序之间的工作流程。例如,它能自动将Gmail中的附件保存至GoogleDrive,或在你发布新文章时,自动分享至社交媒体平台

- 助力新能源汽车产业发展,2025第五届广州国际新能源汽车产业智能制造技术展览会将于11月在广州召开

ws201907

制造汽车

助力新能源汽车产业发展,2025第五届广州国际新能源汽车产业智能制造技术展览会将于11月在广州召开伴随着全球新一轮科技革命和产业变革,汽车与能源、半导体、物联网等领域有关技术加速融合,新能源汽车已成为全球汽车产业转型升级的主要方向。近年来,在相关政策的影响下,新能源汽车市场呈现出快速增长的态势,市场规模不断扩大。截至2020年,中国新能源汽车保有量已超过500万辆,成为全球最大的新能源汽车市场。随

- 广东麻将开发

红匣子实力推荐

在中国,麻将作为一种深受人们喜爱的传统娱乐活动,已经有着数百年的历史。随着互联网和移动设备的普及,麻将游戏也从实体桌面转移到了数字平台,其中广东麻将因其独特的地方特色和玩法而备受青睐。本文将介绍广东麻将的开发过程,包括其设计理念、技术实现以及用户体验优化等方面。一、设计理念:广东麻将开发的核心理念是保留传统麻将的精髓,同时融入现代科技元素,使游戏既具有亲切感又不失趣味性。开发者通常会深入研究广东地

- 以研发创新为驱动力,黄山谷捷助力新能源汽车产业高质量发展

L913197600

黄山谷捷制造科技

在新能源汽车产业蓬勃发展的浪潮中,车规级功率半导体作为驱动电机控制系统的核心部件,其性能与稳定性直接关系到汽车的动力输出、能效转化及安全性能。在这一关键领域,黄山谷捷股份有限公司(以下简称“黄山谷捷”或“公司”)以卓越的研发实力、精湛的生产工艺和严格的质量控制体系,成为行业内的佼佼者,特别是在功率半导体散热基板领域,更是树立了新的标杆。自2012年成立以来,黄山谷捷便深谙“科技是第一生产力”的真谛

- 电子技术引领汽车智能新浪潮,尽在AUTO TECH 2025广州国际汽车电子技术盛会

JSZNZZ

汽车

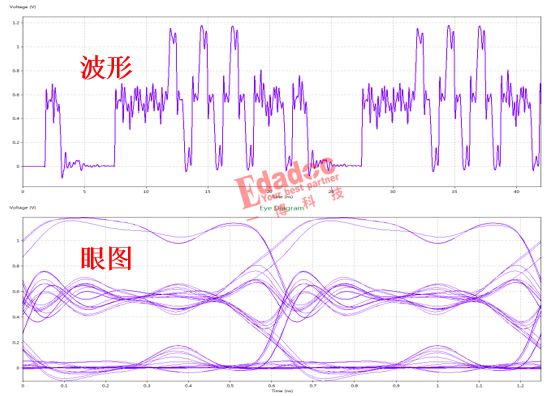

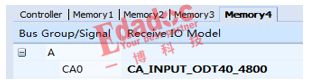

随着科技的持续进步,汽车电子行业正迎来深刻的转型。这一变革的显著特征是从传统的机械控制方式逐渐过渡到智能化和网联化的管理系统。这种转变不仅提升了汽车电子产品的技术复杂性,还极大地丰富了其创新性和功能性。在这个过程中,产品开发的质量和效率变得尤为关键,它们直接决定了企业在激烈竞争环境中的市场地位和商业成功。面对快速变化的市场需求,汽车电子行业在产品开发过程中遇到了多方面的挑战。其中,信息孤岛是一个显

- 一文让你彻底搞懂什么是VR、AR、AV、MR

码上飞扬

vrarmrav

随着科技的飞速发展,现实世界与虚拟世界的界限变得越来越模糊。各种与现实增强相关的技术如雨后春笋般涌现,令人眼花缭乱。本文将为你详细解读四种常见的现实增强技术:虚拟现实(VR)、增强现实(AR)、混合现实(MR)和增强虚拟(AV),让你彻底搞懂它们之间的区别与联系。一、虚拟现实(VR)1.什么是VR?虚拟现实(VirtualReality,简称VR)是一种通过计算机模拟生成的三维环境,使用户能够沉浸

- h5小游戏定制开发

红匣子实力推荐

随着科技的不断发展,移动互联网已经成为人们生活中不可或缺的一部分。在这个背景下,H5小游戏应运而生,为人们带来了丰富的娱乐体验。H5小游戏定制开发作为一种新兴的游戏开发方式,正逐渐受到市场的关注和青睐。那么,什么是H5小游戏定制开发呢?它又具有哪些特点和优势呢?让我们一起来深入了解一下。首先,我们来了解一下H5小游戏的基本概念。H5小游戏是一种基于HTML5技术的游戏,可以在移动端、PC端等多平台

- 40岁的java程序员,还有出路吗?

cesske

java开发语言

目录前言一、现状与挑战二、出路与机遇三、案例分析与启示四、结语前言40岁Java程序员的出路:挑战与机遇并存在科技日新月异的今天,IT行业始终保持着高速的发展态势,而Java作为其中的重要一员,其地位依然稳固且充满挑战。对于一位40岁的Java程序员而言,面对职业生涯的“中年危机”,是否还有出路?本文将从多个维度探讨这一问题,旨在为这一群体提供思考和启示。一、现状与挑战职场竞争加剧随着技术的不断发

- 2019-07-21

珊珊正常奋斗中

姓名:方珊梅公司:深圳市雅诺讯科技有限公司【日精进打卡第49天】(知学)大学通编【经营12条:【口号】让世界信号无线连接(冶企)持续的改善现在的状态,持续的引进新的产品,持续创新,持续引领公司所有上下一条心,为自己为公司为目标而奋斗,持续的持续,就能改良现在的企业经营。【感悟】1:2:天塌下来,手上都要有一样产品是可以赚钱的3:相信团队的力量【感恩】1:感恩父母养育之恩2:感恩上天伺我一个这么优秀

- 【人生感悟】真正厉害的人,抽象思维都很强大

加百力

生活工作感悟大数据科技数据分析

我们都身处信息爆炸的时代,各种资讯蜂拥而至,很难保证所接收的信息都是准确的。在这样的情况下,拥有“穿透迷雾,直击核心”的能力非常关键。虽然钻研各个领域的专业知识可以帮助我们避免信息误导,但这个过程可能超出我们想象地漫长。事实上,真正厉害的人都有一个共同点——他们善于抽象思维。这也是我在读《科技群星闪耀时:15个创新传奇》这本书是意识到的。什么是抽象思维?抽象思维是一种超越细节、直指事物本质的思维方

- 冬奥会开幕式

快乐小鱼儿_9911

今天观看了冬奥会开幕式,立春,冬奥,元素的融合,精彩的设计。开幕式融合了太多的高科技,向世界展现了大国的风采。飘扬的雪花,美丽的舞蹈。雪的轻灵,花的妩媚,构成了美丽的圣火图。整个开幕式,大气,漂亮,鸟巢上方绚丽的烟花,点亮了夜空!开幕式结束了,带着我们的祝福,奥运健儿,再创佳绩。

- 一部手机就能操作的10种赚钱方式,看看哪种适合你?

氧惠全网优惠

手机已经成为了我们生活中不可或缺的一部分,拿着手机刷分享赚钱已经成为了不少人的日常。今天,我想和大家分享一下手机赚钱的10种好方法。京东密令红包:最爱领红包828红包多多148今天给大家分享我长期在做的副业,也在这里赚到人生第3桶金!氧惠APP佣金高,资质靠谱,各大应用市场均可搜索使用。【氧惠】氧惠app是杭州长孚科技有限公司旗下一款新开发电商导购应用,为用户打造一个集成电商购物优惠佣金平台,公司

- 探索创新科技: Lite-Mono - 简约高效的小型化Mono框架

杭律沛Meris

探索创新科技:Lite-Mono-简约高效的小型化Mono框架Lite-Mono[CVPR2023]Lite-Mono:ALightweightCNNandTransformerArchitectureforSelf-SupervisedMonocularDepthEstimation项目地址:https://gitcode.com/gh_mirrors/li/Lite-Mono如果你在寻找一个轻

- 陈悦 | 科学学的起源及其发展

斐夷所非

sciencehistory科学学

作者|陈悦20世纪初,随着科学技术的迅猛发展和科学社会学的兴起,科学学逐渐得到关注和研究。经过百年的发展,科学学正成为一门重要的交叉学科,对科技发展和社会进步产生了深远影响。面对百年未有之大变局加速演进,尤其是世界各国都把目光聚焦于科技,希望通过科技创新找到适应变局的出路时,科学学更凸显其必要性。因此,《世界科学》杂志开设“科学学探索”栏目。一方面,促进更多的人加入科学学的研究和讨论中,深入探讨科

- 【8月星座运势】巨蟹座金钱至上、天蝎贵人相助、双鱼座平衡万物

筝筝陪你看星星

本月重大天象8月2日星期二满月@水瓶座「集思广益、团体活动」水瓶座满月可能带来更强烈的情感和思维的挑战,存在更多的预料不及的突发事件,但同时也增加了对真理和公正的透视力。我们可能会感到更加亲近科技和革新的想法。对于自我实现,人道主义,团体活动和创新有着重要的影响。同时,满月会让我们进行反思,修改策略并将精力投入到这些领域。8月16日星期三新月@狮子座「展翅翱翔、积极自信」新月发生在狮子座是创造性,

- 移动订货小程序哪个好 批发订货系统源码哪个好

多用户商城系统

订货系统源码移动订货小程序批发订货系统订货系统源码

订货小程序就是依托微信小程序的订货系统,微信小程序订货系统相较于其他终端的订货方式,能够更快进入商城,对经销商而言更为方便。今天,我们一起盘点三个主流的移动订货小程序,看看哪个移动订货小程序好。第一、核货宝订货小程序核货宝是商淘科技旗下的订货系统,可为批发企业提供不同客户不同商品、不同客户不同价格快速订货和商家账期管理。功能介绍:客户批发订货的专属数字化订货系统,可以移动端订货。与传统手写开单相比

- IGBT模块直流参数测试系统STD6500

tianshili029

晶体管参数测试系统半导体特性曲线图示仪

陕西天士立科技有限公司IGBT模块直流参数测试系统STD6500IGBT模块直流参数测试系统ST-DC6500基础信息开发背景:大功率IGBT和Diode模块j静态参数程控式设备技术标准:IEC60747-2/GB/T4023-1997半导体器件分立器件和集成电路第2部分(整流二极管)技术标准:IEC60747-9∶2007/GB/T29332-2012半导体器件分立器件第9部分(绝缘栅双极晶体管

- SpringBoot整合ES搜索引擎 实现网站热搜词及热度计算

码踏云端

springbootElasticsearchspringbootelasticsearch后端热搜词热度计算java

博主简介:历代文学网(PC端可以访问:https://literature.sinhy.com/#/literature?__c=1000,移动端可微信小程序搜索“历代文学”)总架构师,15年工作经验,精通Java编程,高并发设计,Springboot和微服务,熟悉Linux,ESXI虚拟化以及云原生Docker和K8s,热衷于探索科技的边界,并将理论知识转化为实际应用。保持对新技术的好奇心,乐于

- 破解游戏app哪个好用 无限99999钻999999金币的游戏盒子排行榜

诸葛村夫123

2024游戏盒子网站排行榜大全随着数位科技的发展,2024年手游市场持续火爆,各种新开手游持续涌现。本文为广大手游爱好者带来巅峰推荐,总结五个最具实力的手游新服发布网站,为您提供最全面的游戏资讯以及专业的游戏攻略。▶无限99999钻999999金币的游戏盒子排行榜TOP1:游戏豹官网特点:内部特权游戏类型:多类型推荐日活跃人数:15万网址链接:www.ystt88.cn游戏介绍:游戏豹官网以快速获

- 国内SAP实施公司大盘点

哲讯智能科技

制造运维

随着企业数字化转型的加速推进,SAP作为全球有名的企业软件解决方案提供商,受到了越来越多企业的青睐。然而,要充分发挥SAP软件的潜力,企业需要依赖专业的SAP实施公司来提供技术支持和咨询服务。在国内,有许多优秀的SAP实施公司,他们拥有丰富的经验和专业知识,能够为企业提供全方位的SAP实施解决方案。在本文中,我们将盘点一些国内的SAP实施公司排名,了解他们的服务和解决方案。1.无锡哲讯智能科技有限

- 外卖会员卡项目源头?外卖会员卡项目现在还能做吗?

鲸天千流

微信小程序

大家好,我是鲸天科技的千千,大家都知道我是做开发的,做互联网很多年了,平时喜欢给大家分享一些互联网相关的创业项目,大家喜欢的可以点个关注。持续为你分享。现在外卖会员卡的这个项目就是风口项目,很多人想知道这个项目的源头,其实这个项目是2021年的时候就有,之前佣金比较少,所以做的人不是很多,现在佣金变多了,所以做的人也多了,现在市场行情也比较好。项目源头一定是做的最早人的才是源头,后面的要么是一级代

- 处理绿盟科技安全评估的系统漏洞

自我修炼的小石头

数据库运维开发工具

如下图一次扫描,中度风险39个,这个是必须要处理的.其中mysql占了36个,一看这个感觉整个人都不好了.但是最后解决的办法也很简单,就是升级.系统版本Redhat7.31.telnet因为要升级openssh,openssl,为了避免意外,首先要开启telnet服务,并把所有相关的包上传到服务器.1.1确认是否安装了telnet和xinetd(默认是没有安装)rpm-qatelnet*rpm-q

- Axure科技感大屏系统设计:智慧农场管理平台

招风的黑耳

Axureaxure科技感可视化智慧农业智慧农场

在数字化转型的浪潮中,数据可视化作为连接现实世界与数字世界的桥梁,正以前所未有的速度改变着各行各业的面貌。智慧农业作为现代农业的重要发展方向,其管理平台的数据大屏设计尤为重要,它不仅是农场运营状况的直接展示窗口,更是决策支持与分析的强有力工具。AxureRP,作为一款强大的原型设计工具,凭借其高度的自定义能力和丰富的交互设计功能,成为了设计科技感十足的智慧农场管理平台大屏的理想选择。Axure在科

- 多线程编程之存钱与取钱

周凡杨

javathread多线程存钱取钱

生活费问题是这样的:学生每月都需要生活费,家长一次预存一段时间的生活费,家长和学生使用统一的一个帐号,在学生每次取帐号中一部分钱,直到帐号中没钱时 通知家长存钱,而家长看到帐户还有钱则不存钱,直到帐户没钱时才存钱。

问题分析:首先问题中有三个实体,学生、家长、银行账户,所以设计程序时就要设计三个类。其中银行账户只有一个,学生和家长操作的是同一个银行账户,学生的行为是

- java中数组与List相互转换的方法

征客丶

JavaScriptjavajsonp

1.List转换成为数组。(这里的List是实体是ArrayList)

调用ArrayList的toArray方法。

toArray

public T[] toArray(T[] a)返回一个按照正确的顺序包含此列表中所有元素的数组;返回数组的运行时类型就是指定数组的运行时类型。如果列表能放入指定的数组,则返回放入此列表元素的数组。否则,将根据指定数组的运行时类型和此列表的大小分

- Shell 流程控制

daizj

流程控制if elsewhilecaseshell

Shell 流程控制

和Java、PHP等语言不一样,sh的流程控制不可为空,如(以下为PHP流程控制写法):

<?php

if(isset($_GET["q"])){

search(q);}else{// 不做任何事情}

在sh/bash里可不能这么写,如果else分支没有语句执行,就不要写这个else,就像这样 if else if

if 语句语

- Linux服务器新手操作之二

周凡杨

Linux 简单 操作

1.利用关键字搜寻Man Pages man -k keyword 其中-k 是选项,keyword是要搜寻的关键字 如果现在想使用whoami命令,但是只记住了前3个字符who,就可以使用 man -k who来搜寻关键字who的man命令 [haself@HA5-DZ26 ~]$ man -k

- socket聊天室之服务器搭建

朱辉辉33

socket

因为我们做的是聊天室,所以会有多个客户端,每个客户端我们用一个线程去实现,通过搭建一个服务器来实现从每个客户端来读取信息和发送信息。

我们先写客户端的线程。

public class ChatSocket extends Thread{

Socket socket;

public ChatSocket(Socket socket){

this.sock

- 利用finereport建设保险公司决策分析系统的思路和方法

老A不折腾

finereport金融保险分析系统报表系统项目开发

决策分析系统呈现的是数据页面,也就是俗称的报表,报表与报表间、数据与数据间都按照一定的逻辑设定,是业务人员查看、分析数据的平台,更是辅助领导们运营决策的平台。底层数据决定上层分析,所以建设决策分析系统一般包括数据层处理(数据仓库建设)。

项目背景介绍

通常,保险公司信息化程度很高,基本上都有业务处理系统(像集团业务处理系统、老业务处理系统、个人代理人系统等)、数据服务系统(通过

- 始终要页面在ifream的最顶层

林鹤霄

index.jsp中有ifream,但是session消失后要让login.jsp始终显示到ifream的最顶层。。。始终没搞定,后来反复琢磨之后,得到了解决办法,在这儿给大家分享下。。

index.jsp--->主要是加了颜色的那一句

<html>

<iframe name="top" ></iframe>

<ifram

- MySQL binlog恢复数据

aigo

mysql

1,先确保my.ini已经配置了binlog:

# binlog

log_bin = D:/mysql-5.6.21-winx64/log/binlog/mysql-bin.log

log_bin_index = D:/mysql-5.6.21-winx64/log/binlog/mysql-bin.index

log_error = D:/mysql-5.6.21-win

- OCX打成CBA包并实现自动安装与自动升级

alxw4616

ocxcab

近来手上有个项目,需要使用ocx控件

(ocx是什么?

http://baike.baidu.com/view/393671.htm)

在生产过程中我遇到了如下问题.

1. 如何让 ocx 自动安装?

a) 如何签名?

b) 如何打包?

c) 如何安装到指定目录?

2.

- Hashmap队列和PriorityQueue队列的应用

百合不是茶

Hashmap队列PriorityQueue队列

HashMap队列已经是学过了的,但是最近在用的时候不是很熟悉,刚刚重新看以一次,

HashMap是K,v键 ,值

put()添加元素

//下面试HashMap去掉重复的

package com.hashMapandPriorityQueue;

import java.util.H

- JDK1.5 returnvalue实例

bijian1013

javathreadjava多线程returnvalue

Callable接口:

返回结果并且可能抛出异常的任务。实现者定义了一个不带任何参数的叫做 call 的方法。

Callable 接口类似于 Runnable,两者都是为那些其实例可能被另一个线程执行的类设计的。但是 Runnable 不会返回结果,并且无法抛出经过检查的异常。

ExecutorService接口方

- angularjs指令中动态编译的方法(适用于有异步请求的情况) 内嵌指令无效

bijian1013

JavaScriptAngularJS

在directive的link中有一个$http请求,当请求完成后根据返回的值动态做element.append('......');这个操作,能显示没问题,可问题是我动态组的HTML里面有ng-click,发现显示出来的内容根本不执行ng-click绑定的方法!

- 【Java范型二】Java范型详解之extend限定范型参数的类型

bit1129

extend

在第一篇中,定义范型类时,使用如下的方式:

public class Generics<M, S, N> {

//M,S,N是范型参数

}

这种方式定义的范型类有两个基本的问题:

1. 范型参数定义的实例字段,如private M m = null;由于M的类型在运行时才能确定,那么我们在类的方法中,无法使用m,这跟定义pri

- 【HBase十三】HBase知识点总结

bit1129

hbase

1. 数据从MemStore flush到磁盘的触发条件有哪些?

a.显式调用flush,比如flush 'mytable'

b.MemStore中的数据容量超过flush的指定容量,hbase.hregion.memstore.flush.size,默认值是64M 2. Region的构成是怎么样?

1个Region由若干个Store组成

- 服务器被DDOS攻击防御的SHELL脚本

ronin47

mkdir /root/bin

vi /root/bin/dropip.sh

#!/bin/bash/bin/netstat -na|grep ESTABLISHED|awk ‘{print $5}’|awk -F:‘{print $1}’|sort|uniq -c|sort -rn|head -10|grep -v -E ’192.168|127.0′|awk ‘{if($2!=null&a

- java程序员生存手册-craps 游戏-一个简单的游戏

bylijinnan

java

import java.util.Random;

public class CrapsGame {

/**

*

*一个简单的赌*博游戏,游戏规则如下:

*玩家掷两个骰子,点数为1到6,如果第一次点数和为7或11,则玩家胜,

*如果点数和为2、3或12,则玩家输,

*如果和为其它点数,则记录第一次的点数和,然后继续掷骰,直至点数和等于第一次掷出的点

- TOMCAT启动提示NB: JAVA_HOME should point to a JDK not a JRE解决

开窍的石头

JAVA_HOME

当tomcat是解压的时候,用eclipse启动正常,点击startup.bat的时候启动报错;

报错如下:

The JAVA_HOME environment variable is not defined correctly

This environment variable is needed to run this program

NB: JAVA_HOME shou

- [操作系统内核]操作系统与互联网

comsci

操作系统

我首先申明:我这里所说的问题并不是针对哪个厂商的,仅仅是描述我对操作系统技术的一些看法

操作系统是一种与硬件层关系非常密切的系统软件,按理说,这种系统软件应该是由设计CPU和硬件板卡的厂商开发的,和软件公司没有直接的关系,也就是说,操作系统应该由做硬件的厂商来设计和开发

- 富文本框ckeditor_4.4.7 文本框的简单使用 支持IE11

cuityang

富文本框

<html xmlns="http://www.w3.org/1999/xhtml">

<head>

<meta http-equiv="Content-Type" content="text/html; charset=UTF-8" />

<title>知识库内容编辑</tit

- Property null not found

darrenzhu

datagridFlexAdvancedpropery null

When you got error message like "Property null not found ***", try to fix it by the following way:

1)if you are using AdvancedDatagrid, make sure you only update the data in the data prov

- MySQl数据库字符串替换函数使用

dcj3sjt126com

mysql函数替换

需求:需要将数据表中一个字段的值里面的所有的 . 替换成 _

原来的数据是 site.title site.keywords ....

替换后要为 site_title site_keywords

使用的SQL语句如下:

updat

- mac上终端起动MySQL的方法

dcj3sjt126com

mysqlmac

首先去官网下载: http://www.mysql.com/downloads/

我下载了5.6.11的dmg然后安装,安装完成之后..如果要用终端去玩SQL.那么一开始要输入很长的:/usr/local/mysql/bin/mysql

这不方便啊,好想像windows下的cmd里面一样输入mysql -uroot -p1这样...上网查了下..可以实现滴.

打开终端,输入:

1

- Gson使用一(Gson)

eksliang

jsongson

转载请出自出处:http://eksliang.iteye.com/blog/2175401 一.概述

从结构上看Json,所有的数据(data)最终都可以分解成三种类型:

第一种类型是标量(scalar),也就是一个单独的字符串(string)或数字(numbers),比如"ickes"这个字符串。

第二种类型是序列(sequence),又叫做数组(array)

- android点滴4

gundumw100

android

Android 47个小知识

http://www.open-open.com/lib/view/open1422676091314.html

Android实用代码七段(一)

http://www.cnblogs.com/over140/archive/2012/09/26/2611999.html

http://www.cnblogs.com/over140/arch

- JavaWeb之JSP基本语法

ihuning

javaweb

目录

JSP模版元素

JSP表达式

JSP脚本片断

EL表达式

JSP注释

特殊字符序列的转义处理

如何查找JSP页面中的错误

JSP模版元素

JSP页面中的静态HTML内容称之为JSP模版元素,在静态的HTML内容之中可以嵌套JSP

- App Extension编程指南(iOS8/OS X v10.10)中文版

啸笑天

ext

当iOS 8.0和OS X v10.10发布后,一个全新的概念出现在我们眼前,那就是应用扩展。顾名思义,应用扩展允许开发者扩展应用的自定义功能和内容,能够让用户在使用其他app时使用该项功能。你可以开发一个应用扩展来执行某些特定的任务,用户使用该扩展后就可以在多个上下文环境中执行该任务。比如说,你提供了一个能让用户把内容分

- SQLServer实现无限级树结构

macroli

oraclesqlSQL Server

表结构如下:

数据库id path titlesort 排序 1 0 首页 0 2 0,1 新闻 1 3 0,2 JAVA 2 4 0,3 JSP 3 5 0,2,3 业界动态 2 6 0,2,3 国内新闻 1

创建一个存储过程来实现,如果要在页面上使用可以设置一个返回变量将至传过去

create procedure test

as

begin

decla

- Css居中div,Css居中img,Css居中文本,Css垂直居中div

qiaolevip

众观千象学习永无止境每天进步一点点css

/**********Css居中Div**********/

div.center {

width: 100px;

margin: 0 auto;

}

/**********Css居中img**********/

img.center {

display: block;

margin-left: auto;

margin-right: auto;

}

- Oracle 常用操作(实用)

吃猫的鱼

oracle

SQL>select text from all_source where owner=user and name=upper('&plsql_name');

SQL>select * from user_ind_columns where index_name=upper('&index_name'); 将表记录恢复到指定时间段以前

- iOS中使用RSA对数据进行加密解密

witcheryne

iosrsaiPhoneobjective c

RSA算法是一种非对称加密算法,常被用于加密数据传输.如果配合上数字摘要算法, 也可以用于文件签名.

本文将讨论如何在iOS中使用RSA传输加密数据. 本文环境

mac os

openssl-1.0.1j, openssl需要使用1.x版本, 推荐使用[homebrew](http://brew.sh/)安装.

Java 8

RSA基本原理

RS