ARM内核与架构

1、ARM架构分类

ARM架构发展至今分为 ARMv1~ARMv8 ,不同架构之间指令集存在差异。根据架构类型又开发出不同内核,常用的 ARMv7 架构有三种类型的内核:

1)Cortex-A:用于高性能应用,主要支持分页内存管理单元MMU,linux需要MMU的支持才能运行。

2)Cortex-R:侧重于实时性应用,如汽车系统。

3)Cortex-M:侧重于微控制器,常用的STM32就是此内核。

2、Cortex-A7 处理器运行模式

不同模式之间可通过软件、中断和异常进行切换。大多数程序运行在用户模式。

1)用户模式(USER),运行在操作系统的用户态,没有权限访问其它硬件资源,只能通过中断或异常进入其他模式。

2)快速中断模式(FIQ),用于处理高速数据传输和通道处理。

3)一般中断模式(IRQ),通常在硬件产生中断后进入此模式。

4)超级管理员模式(SVC),CPU上电后默认模式,用于系统初始化。

5)监视模式(MON)

6)数据访问终止模式(ABT),当用户程序访问非法地址,没有权限读取的内存地址时,进入此模式,常见的 segment fault 是在此模式抛出。

7)超级监视模式(HYP)

8)未定义指令终止模式(UND),CPU在指令译码阶段不能识别该操作指令时,进入此模式。

9)系统模式(SYS),比用户模式有更高的权限,可访问所有系统资源。

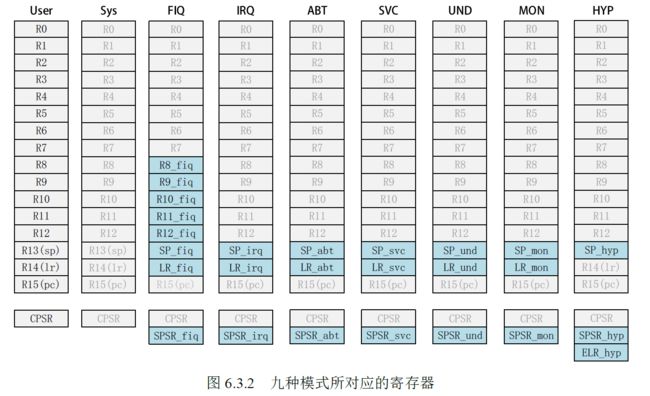

3、Cortex-A7 寄存器组

图中灰色寄存器为物理共享寄存器,蓝色寄存器为独有寄存器。总共有34个通用寄存器和8个状态寄存器,HYP模式下还有一个 ELR_hyp 寄存器。

1)通用寄存器(R0~R15)

A、未备份寄存器(R0~R7),所有模式都使用同一个物理寄存器,数据会被破坏。

B、备份寄存器(R8~R14),当运行在快速中断模式下,访问 R8~R12 时是访问此模式独有的寄存器,因此快速中断模式要比普通中断模式快,因为少了保存和恢复寄存器数据的过程。R13 存放 SP 指针,不同模式有自己独立的栈空间。R14 存放当前子程序的返回地址,在子函数中,将 LR 幅值给 PC 即可完成子函数返回。

C、程序计数器 R15,由于3级流水线:取指令——译码——执行,PC 总是指向当前执行的指令地址再加上两条指令的地址,即当前执行的指令地址 = PC - 8。

2)程序状态寄存器(CPSR),所有运行模式都共用一个 CPSR,而 SPSR 用于保存当前状态寄存器的值,在异常退出后也能够恢复 CPSR。CPSR 包含了条件标志位、中断禁止位、当前处理器模式标志位、一些控制位等。

4、哈佛架构和冯诺依曼架构

1)哈佛架构:指令和数据独立编址,使用两条独立的总线传输,读取指令和数据可同时进行。

2)冯诺依曼结构:指令和数据统一编址,使用同条总线传输,无法同时进行读取指令和数据。

嵌入式计算机主要采用哈佛结构,有较高的可靠性、较大的吞吐量和运算速度,ARM7采用的是冯诺依曼结构。

5、ARM指令集分类

大部分ARM架构同时支持 ARM 指令集和 Thumb 指令集。执行不同指令集需要切换状态。异常中断处理只能使用 ARM 指令集。

1)Thumb 指令集,指令长度为16位

2)ARM 指令集,指令长度为32位,ARMv8架构新增了64位指令

3)Thumb2 指令集,混合了16位指令和32位指令,能够处理异常中断,CM3 只用了 Thumb2指令集

6、ARM工作状态分类

1)ARM状态,执行32位字对齐的 ARM 指令,绝大部分工作在此状态。

2)Thumb状态,执行16位半字对其的 Thumb 指令。

7、ARM系统中,函数调用时参数传递方式

参数个数小于等于4个时,用 R0~R3 进行传递,大于4个时,超出部分用压栈的方式进行传递。

8、ARM协处理器指令作用

1)用于 ARM 处理器初始化,ARM 协处理器数据处理操作。

2)ARM 处理器的寄存器和协处理器的寄存器之间传送数据。

3)ARM 协处理器的寄存器和存储器之间传送数据。

初始化,ARM 协处理器数据处理操作。

2)ARM 处理器的寄存器和协处理器的寄存器之间传送数据。

3)ARM 协处理器的寄存器和存储器之间传送数据。