PCIE自学笔记硬件篇+协议浅析

1.前言

最近在学习 PCIE 总线协议,本文旨在笔记加深下自己的理解。如果你也是刚开始入门的朋友,希望能你有所帮助。水平有限,如有错误,望批评指正。

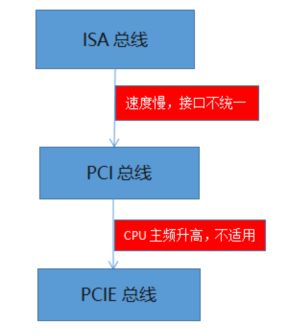

2.PCIE的演变

PCI的提出是为了解决当时的ISA/EISA,MCA,VLB等总线速度太慢,接口混乱不统一而提出的,但是随着CPU主频的不断提高,PCI总线的带宽越来越难以满足要求。关于PCIE总线的前身简单以下图示意,此处不做赘述。

PCIe是在PCI的基础上发展而来的。而PCI则是Intel在1992年提出的一套总线协议,用于高速设备之间的数据传输,以及用于CPU其他设备资源的扩展。PCIe可拓展性强,可以支持的设备有:显卡、SATA、网卡、声卡、视频采集卡、PCIe转USB、PCIe转串口等。

3.PCIE的特点

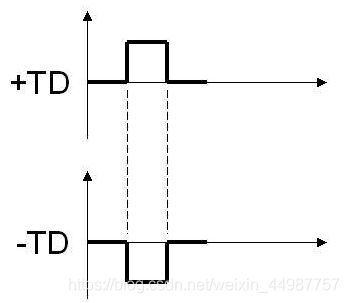

① PCIe使用了高速差分总线端到端的方式进行连接,差分信号可以匹配更高的时钟频率,且信号传输时的抗干扰能里要比单端信号强很多通过一正一反镜像传输,干扰可以很快被发现和纠正,从而可以将传输频率大幅提升。

② PCIe的每条链路可以由多条Lane组成,换句话来说它的性能可扩展,拆常见为LAN数有X1、X8、X16;可根据LANE数灵活配置PCIE设备的速率。一般X16用于扩展显卡。

③ PCIe使用了网络通信中使用的技术如基于多种数据路由方式,报文数据传送,以及Traffic class和virtual channel等;

④ PCIe还引入了嵌入式时钟的技术,即发送端不再向接收端发送时钟,接收端可以通过8b/10b,128b/130b (PCIE3.0) 的编码从数据Lane中恢复出时钟;

⑤现在X16的PCIE3.0接口带宽可以达到16000MB/S。

4.PCIE总线结构:

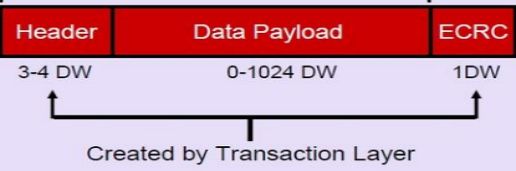

PCIE总线类似于网络中的TCP/IP模型,由上到下分别是应用层,事务层(Transaction Layer),数据链路层(Data Link Layer),物理层(Physical Layer);其中,应用层完全由用户根据自己的需求进行设计。另外三层都是PCIe Spec明确规范的,并要求设计者严格遵循的。

① 事务层

PCIe事务层定义了总线所使用的事务,规定了四种类型的请求:Memory、IO、Configuration和Messages。其中,前三种都是从PCI/PCI-X总线中继承过来的,第四种Messages是PCIe新增加的类型。事务层接收来自核心层的数据并将其封装成TLP(Transaction Layer Packet)发向数据链路层。另外事务层也可以从数据链路层接收数据报文,然后转发到核心层。

② 数据链路层

数据链路层接收来自事务层的数据报文,添加Sequence Number前缀和CRC后缀。数据链路层使用ACK/NAK协议保证报文的可靠传递。另外它还定义了多种DLLP(Data Link Layer Pakcet)层。DLLP 产生于数据链路层结束于数据链路

③ 物理层:

物理层是PCIe总线的最底层,将PCIe设备相互连接在一起。它负责接收和转发各种数据包(TLP,DLLP)。另外它还创建和解码一些专门的序列Ordered-Set Packet或者叫做PLP(Physical Layer Packet),这些序列用于同步和管理链路。物理层还实现了链路训练和初始化的功能,它通过LTSSM来完成(Link Training and Status State Machine)PCIe采用了端到端的全双工的传输设计,基于数据包的传输,设备之间通过link相连,link支持1到32个通道(lane)。每一个LANE类比RS422的物理链路。

5.PCIe体系的拓扑结构

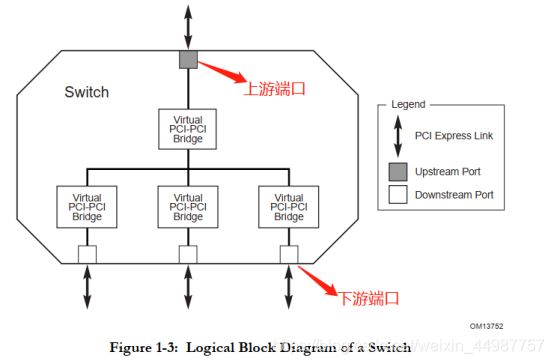

PCIe协议规定可以与RC直接或者间接相连的端口称之为上游端口,在PCIe总线中,RC的位置一般在上方,这也是上游端口的由来。除上游端口之外的其它端口就是下游端口。

① Root Complex

RC是PCIe体系结构中的一个重要的组成部件,它是CPU和PCIe总线直接的接口。它的主要功能是完成存储器域到PCIe总线域的地址转换,RC把来自CPU的request转化成PCIe的4种不同的requests(configuration, Memory, I/O, Message)并发送给接在它下面的设备。从软件的角度来看,RC像是一组虚拟的PCI-PCI桥。

② PCIe Switch

Switch提供了数据分散或者是聚合的功能,它允许更多的设备接入到 同一个PCIe Port。它扮演了数据包路由的功能。

③ PCIe Endpoint

它只有一个上游端口,位于PCIe拓扑结构的树的末端。它作为请求的发起者或者完成者。分为Legacy Endpoint和Native Endpoint,Legacy使用PCI总线的操作用于支持向后兼容。

④ PCIe的枚举

在含有PCIE设备的主板上,开机后在BOIS阶段进行的设备自检,就是PCIE枚举的过程其实是一个使用深度优先的算法不断递归发现新设备的过程。枚举过程中除了配置bus,还会通过读取bar记录所有MMIO和IO的需求情况。大致过程如下:

A. 利用深度优先算法遍历整个PCI设备树。(从Root Complex出发,寻找设备和桥。发现桥后设置Bus,会发现一个PCI设备子树,递归回到A)

B. 递归的过程中通过读取BARs,记录所有MMIO和IO的需求情况并予以满足。

C. 设置必要的Capabilities

在整个过程结束后,一颗完整的资源分配完毕的树就建立好了。

6.硬件设计时需要注意的点:

① AC 电容、校准电阻要求

关于AC耦合电容的作用请戳:基于XILINX FPGA芯片高速串行接口GTX学习笔记

输出端到接收端之间,PCIe 总线采用交流耦合的方式进行传输,不同的标准对应不同的容值,另外在layout时需要注意,耦合电容一般靠近TX发送端放置;

② 关于PCIE LANE拆分问题:

设计拆分前首先要明白PCIE设备有多少个控制端口,控制端口决定着拆分结果,这个一般手册上都会有说明,抛开BOIS软件配置不说,有些PCIE设备有“PCIE_*_PRSNTn ”这个信号有多少个就对应多少个控制端口,该信号为PCIE控制器的使能信号端,低有效,当不用时悬空即可;举个例子:某个PCIE设备有32 Lane,但是只有两个控制端口,因此拆分时最优的拆分就是两个X16 ,当然你也可以拆分成两个X1 ,那也是相当奢侈!

③ PCB走线注意问题点:

(a)PCIE总线上每个LANE 上AC耦合电容两端需要进行分段等长,芯片扇出部分走线阻抗可不做严格控制,但是尽量缩短扇出线部分的走线长度

(b) 阻抗控制100Ω,差分对PN两条布线总长度之差不能超过4mils 。

(c)信号如果需要打孔换层,建议在换层孔附近添加回流孔,回流孔尽量靠近信号孔。

(D) 走线参考GND,保证参考平面完整,不允许有跨平面分割的情况。如果设计中无法避免跨平面参考,建议在跨平面分割处用旁路电容将回流信号连接起

(E) TX和RX建议走在不同层,或者隔开尽可能远的距离。差分对P和N必须在同一层,并按照差分约束布线。

④校准电阻

PCIE控制器上的校准电阻,精度为1%,布局时需要靠近器件放置,远离干扰源。

参考文章:

https://zhuanlan.zhihu.com/p/283026221 https://zhuanlan.zhihu.com/p/26172972