Xilinx FPGA selectIO笔记

前言

内容主要来自ug471,主要记录FPGA的文档的学习笔记,参考的内容一个是csdn上的笔记和ug471文档

此外还有部分是UG571文档中的接口说明

ug471主要包含三部分,第一章是selectIO资源,第二章是selectIO 逻辑资源,第三章是高级selectIO逻辑资源,第一章的selectIO资源主要是描述接口的电气行为,主要是输出驱动和输入接收器,以及部分标准接口的例子,第二章主要描述的是输入输出的数据寄存器和DDR操作,以及可编程的输入延迟(IDELAY)和输出延迟(ODELAY);第三章主要是写serdes部分

ug571 主要是ultrascale 系列的selectIO的管脚说明文档,前面主要讲述HP和HR bank的部分功能,后面讲述新的HDbank 的属性,

文档主要结合两者,在硬件方面的描述,然后撰写该笔记,笔记包含HD和HP HRbank支持的所有的管脚电平标准描述,用来确认硬件对于不同电平标准情况下所需要的硬件条件(Vref和DCI功能,以及差分电平支持等,)至于管脚内部的资源等则留做后面的工作继续。

目录

前言

selectIO 资源

7系列 select IO简介

UltraScale架构简介

DCI

FPGA SelectIO Attributes/Constraints

7 Series

UltraScale

Supported I/O Standards and Terminations

LVTTL

LVCMOS

HSTL

SSTL

HSUL_12 (High Speed Unterminated Logic)

LVDS and LVDS_25 (Low Voltage Differential Signaling)

POD(Pseudo Open Drain)

LVPECL

SelectIO Logic Resources

UltraScale

bank简介

HD bank

参考资料

selectIO 资源

7系列 select IO简介

7系列的器件主要的bank有两种,一个是HPbank (high-performance) 一个是HRbank(high-range),HPbank可以支持更高速率的性能,但是电压最高只能到1.8V,HR能够提供更高的电压输出范围,最高能到3.3V但是性能不够。

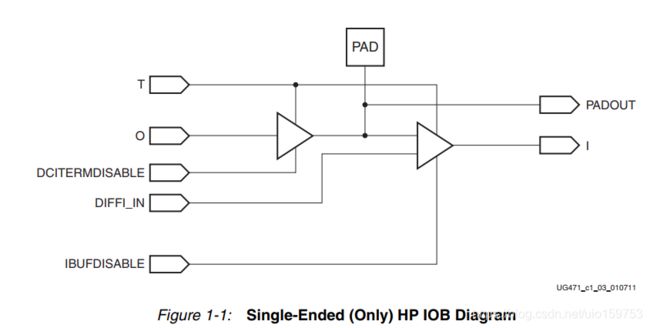

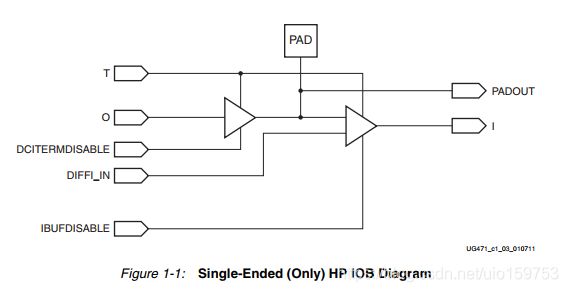

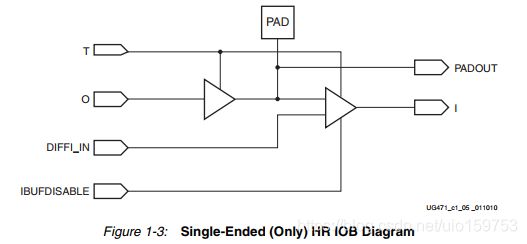

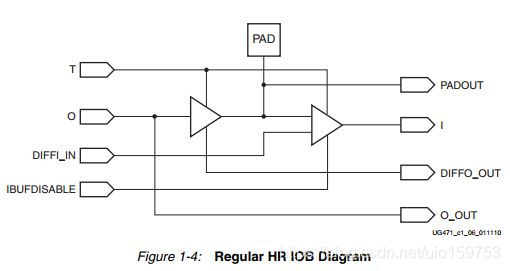

7系列的芯片支持可编程的控制输出轻度和斜率,还有DCI实现片上的端接,以及产生内部参考电压,(HRbank不能够用DCI)。一般一个bank有50个pin管脚,其中有48个可以即支持单端也支持差分。单端HP bank的 I/O block (IOB)和单端的HRbank 的IOB具有一样的结构,具体如下

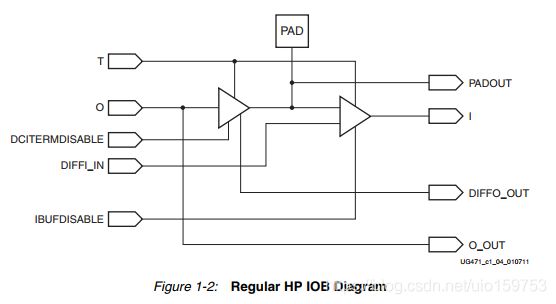

常规的HP和HRbank 的IOB也是一样的结构,具体如下所示

VCCO :bank 的供电,一般就是vcco是多少电压,整个bank 的IO都是遵循VCCO的电压来的

Vref : 如果单端接口标准用了一个差分输入的buffer ,那就需要VREF,两个管脚都需要接,当然,7系列还是提供了内部的Vref,可以通过约束来实现

VCCaux :主要给7系列内部互联逻辑进行供电,和部分IO标准的输入buffer供电用的,它包含全部的1.8V以及1.8V一下的接口和HRbank2.5V的单端接口。以及差分的输入的buffer供电,以及vref供电用,

VCCAUX_io: HPbank的辅助供电,主要是给更高的频率性能的存储器接口用的

UltraScale架构简介

ultraScale 是xilinx的首个ASIC级架构,包括下一代的布线,类ASIC时钟,3D-on-3D IC和多核处理器SoC (MPSoC)技术

基于UltraScale架构的器件可提供各种I/O产品:高性能(HP)、高密度(HD)和高量程(HR) I/O bank。

-

HP I/O bank旨在满足高速存储器和其它芯片对芯片接口 (电压上限1.8V)的性能要求。

-

HR I/O bank旨在支持更广泛的I/O标准 (电压上限3.3V)。

-

HD I/O bank旨在支持低速接口。

但是并不是所有的器件都包含了这三种类型的接口,Zynq UltraScale+、Kintex UltraScale+和Virtex UltraScale+系列包含有HD和HPbank,Kintex UltraScale和Virtex UltraScale系列包含HR和HPbank,

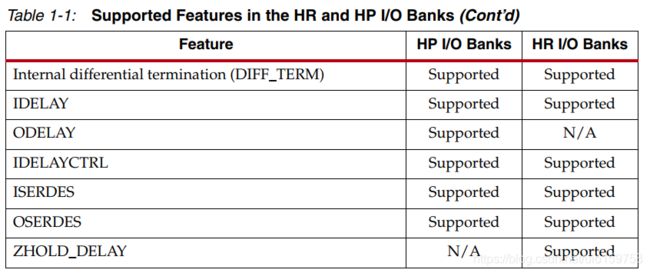

表1-1:HR和HR I/O bank中受支持的功能

| 功能 |

HP I/O bank |

HR I/O bank |

| 3.3V I/O标准(1) |

不适用 |

支持 |

| 2.5V I/O标准(1) |

不适用 |

支持 |

| 1.8V I/O标准(1) |

支持 |

支持 |

| 1.5V I/O标准(1) |

支持 |

支持 |

| 1.35V I/O标准(1) |

支持 |

支持 |

| 1.2V I/O标准(1) |

支持 |

支持 |

| 1.0V POD I/O标准 |

支持 |

不适用 |

| LVDS信号 |

支持(2) |

支持 |

| 数控阻抗(DCI)和DCI级联 |

支持 |

不适用 |

| 内部VREF |

支持 |

支持 |

| 内部差分终端(DIFF_TERM) |

支持 |

支持 |

| IDELAY |

支持 |

支持 |

| ODELAY |

支持 |

支持 |

| IDELAYCTRL |

支持 |

支持 |

| ISERDES |

支持 |

支持 |

| OSERDES |

支持 |

支持 |

| 发射器预加重 |

支持 |

支持(3) |

| 接收器均衡 |

支持 |

支持 |

| 接收器偏移控制 |

支持 |

不支持 |

| 接收器VREF扫描 |

支持 |

不支持 |

| MIPI D-PHY |

在Virtex UltraScale+、Kintex UltraScale+和Zynq UltraScale+ 器件中受支持 |

不支持 |

ultrascale 系列支持的是每个bank共有52个select IO 管脚,小型的HR bank包含26个select IO管脚,DCI功能同样只在HPbank上有,然后就是HP I/O bank中的DDR4标准和HP/HR I/O bank中的LVDS TX标准都可以使用预加重功能。

SelectIO管脚可根据各种I/O标准 (包括单端和差分)进行配置。 •单端I/O标准包括LVCMOS、LVTTL、HSTL、SSTL、HSUL和POD等。 •差分I/O标准包括LVDS、Mini_LVDS、RSDS、PPDS、BLVDS、TMDS、SLVS、LVPECL、SUB_LVDS以及差分 HSTL、POD、HSUL和SSTL等。

DCI

DCI(digitally controlled impedance)数字控制阻抗技术,DCI可以控制输出的阻抗或者添加并联端接在输入额输出端,对于7系列的芯片 DCI通过外部的放置在VRN和VRP端的管脚,甚至可以通过连续的阻抗调整来实行对于温度和电压波动的补偿。此外HPbank才有DCI功能,HRbank没有这功能。DCI 通过一个VRN 端电阻上拉到电源VCCO ,VRP端下拉电阻到地,阻值等特征电阻的阻值或者两倍。

对于UltraScale系列的芯片,使用DCI标准时,VRP管脚必须通过参考电阻端接到GND。电阻值应为240Ω。而且也是只能HPbank 才能使用。因此支持的端接的电阻主要有40Ω,48欧姆60欧姆,差分的就是双倍,具体如下RTT_40 • RTT_48 • RTT_60 • RTT_120 • RTT_240 • RTT_NONE

差分的端接一般是100欧姆,这属于内部内置的,不需要vrp来操作,

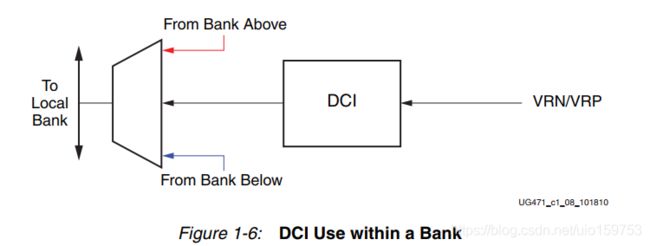

同样DCI支持DCI cascading也就是从别的bankDCI阻抗值来实现具体如下图所示,但是只能是同一列的bank才好使,而且中间不能有较大的插入边界,主从bank 之间必须要是相同的VCCO和Vref电压,

一般一列有一个了,其他的都好使,

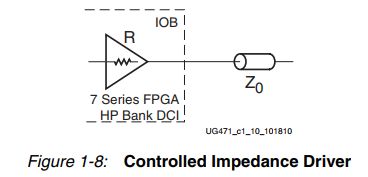

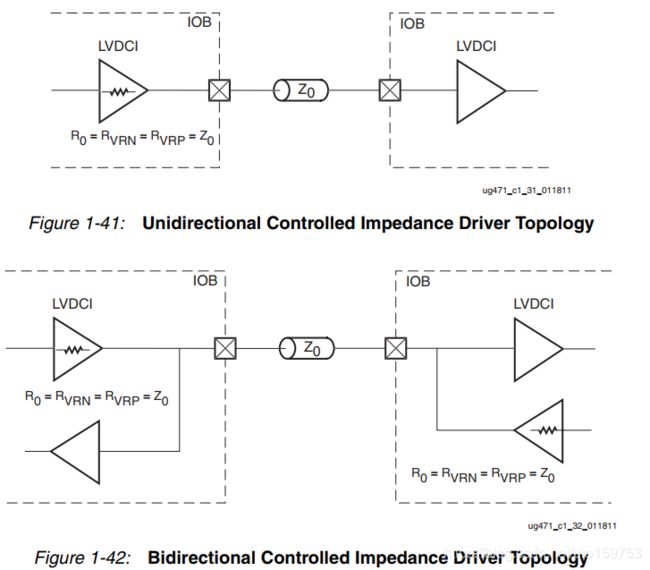

DCI同样支持源端的端接,具体支持的IO电平标准为:LVDCI_15, LVDCI_18, HSLVDCI_15, HSLVDCI_18, HSUL_12_DCI, and DIFF_HSUL_12_DCI.对于源端匹配,2倍阻抗的阻值也是可以的,

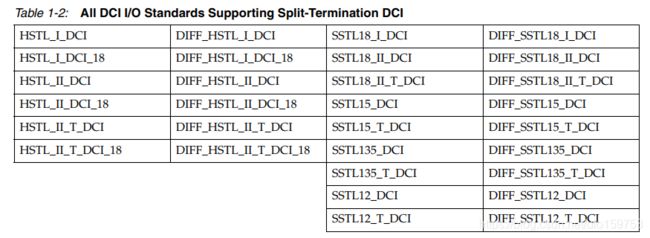

对于输入终端的端接方式,戴维南等效,所有的支持DCI功能的接口标准都支持戴维南等效

戴维南等效电路如下,外部VRP和VRN上连接的电阻都是2倍的阻抗的值,如果想要通过匹配到50欧姆,那么就需要在VRN到电源和VRP到地分别接100欧姆电阻,这个只是在7系列的操作,如果是6系列的DCI则是50欧姆,这块需要注意。

戴维南等效的端接同样在某些电平标准的输入和双向口也有,主要是class II 的SSTL和HSTL。class I的不行,只能支持输入。

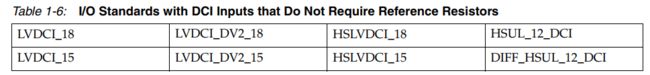

一般情况下VRN和VRP需要接电阻,才能实现DCI功能,但是如果临近的bank有一个bank进行了端接,那么也可以不用端接,还有就是如果是以下的电平标准,且该bank有且仅有这一个电平标准时候,那也可以不用VRN和VRP接电阻。

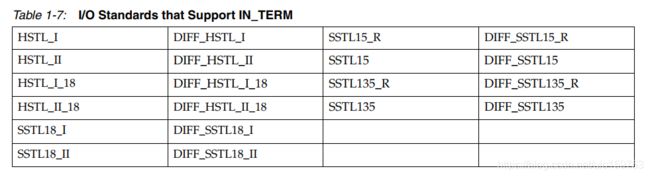

在HRbank中虽然不支持DCI,但是也支持片上端接(IN_TERM),只不过是不能够校准温度和电压波动,支持的戴维南等效的电阻值是40Ω,50Ω,60Ω。支持这种模式的有以下几种

在ultrascale系列里面,除了DCI之外还支持的未经校准的输入端接,DCI会校准VRP管脚上的参考电阻,未校准的输入终端功能会调用由ODT属性确定的内部电阻。内部的电阻没有校准例程来补偿温度、工艺或电压变化

-

拆分终端标准 (HSTL和SSTL)的可能ODT值为RTT_40、RTT_48、RTT_60或RTT_NONE。

-

单终端POD标准的可能ODT值为RTT_40、RTT_48、RTT_60或RTT_NONE。

-

对于单终端HSUL标准,可能ODT值为RTT_120、RTT_240或RTT_NONE。

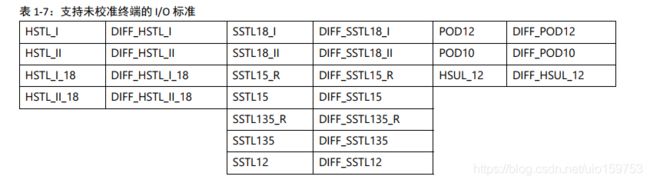

匹配主要有两种一个是源端匹配一个是终端匹配,对于支持末端匹配(输入匹配)的有如下表所示的接口标准。这种的话HP和HRbank都支持,

HPbank另外还支持未经校准的源端匹配(输出匹配),OUTPUT_IMPEDANCE的允许值为RDRV_40_40、RDRV_48_48或RDRV_60_60。

FPGA SelectIO Attributes/Constraints

7 Series

selectIO属性里面主要的几个有需要注意的,一个是IBUF_LOW_PWR attribute。这个属性并不是所有的接口标准都支持,只有如下的几个支持

• LVDS • LVDS_25 • PPDS_25 • RSDS_25 • MINI_LVDS_25 • BLVDS_25 • DIFF_HSTL (all variations) • DIFF_SSTL (all variations) • DIFF_MOBILE_DDR • DIFF_HSUL (all variations)• All VREF-based inputs such as HSLVDCI, SSTL, HSTL, and HSUL • All input and bidirectional primitives

对于内部的Vref管脚的使用可以用:INTERNAL_VREF_BANK14 = 0.75; 来表示,主要支持的内部参考电压有以下几种:0.60 • 0.675 • 0.75 • 0.90 。

还有输出强度属性,以及上拉和下拉操作

Table 1-8:Allowed Values for the DRIVE Attribute

| Standard |

HR Bank Current Drive (mA) |

HP Bank Current Drive (mA) |

| LVCMOS12 |

4, 8, or 12 |

2, 4, 6, or 8 |

| LVCMOS15 |

4, 8, 12, or 16 |

2, 4, 6, 8, 12, or 16 |

| LVCMOS18 |

4, 8, 12, 16, or 24 |

2, 4, 6, 8, 12, or 16 |

| LVCMOS25 |

4, 8, 12, or 16 |

N/A |

| LVCMOS33 |

4, 8, 12, or 16 |

N/A |

| LVTTL |

4, 8, 12, 16, or 24 |

N/ |

UltraScale

ultrascale 系列添加了7系列不一样的属性主要有片上端接ODT属性,内部vref属性,还有DQS的偏置,以及预加重和均衡等。

ODT功能,ODT属性在HSTL、SSTL、POD和HSUL标准的输入上支持拆分终端或单终端。ODT分支持DCI功能的端接和非DCI功能的端接。

支持的属性主要有以下几个:

• RTT_40 • RTT_48 • RTT_60 • RTT_120 • RTT_240 • RTT_NONE

OUTPUT_IMPEDANCE属性为HSTL、SSTL、HSUL、LVDCI、HSLVDCI和POD驱动提供选择驱动阻抗的选项,以匹配驱动线路的特性阻抗。OUTPUT_IMPEDANCE属性用于为受支持的标准DCI版本和非DCI版本定义驱动的源极终端的值。

OUTPUT_IMPEDANCE属性的允许值: • RDRV_40_40 • RDRV_48_48 • RDRV_60_60 • RDRV_NONE_NONE

内部VREF,内部的vref每一个bank一个Vref值,并且只能是额定的参考电压值,具体有如下的几个:

0.60 ,0.675 ,0.70, 0.75 ,0.84,0.90 。同一个bank内不能同时使用内部的Vref和外部的Vref,在任一bank内使用internal_Vref和Vref扫描的时候,应通过500Ω或1KΩ电阻将专用外部VREF管脚连接至GND。

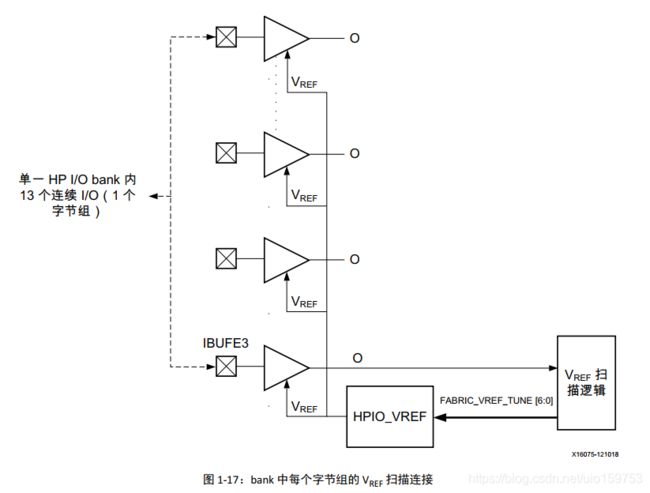

另外HPbank还支持输入的Vref扫描功能,可以通过

DQS_BIAS

DQS_BIAS通过将缓存的N侧弱拉到VCCO并将缓存的P侧接地,充当伪差分(DIFF_SSTL、DIFF_HSUL和DIFF_POD) 缓存中非驱动管脚的逻辑保持机制。对于LVDS输入,DQS_BIAS向缓存的P侧和N侧都提供值为VCCO/2的DC偏置。

预加重

使用发射器预加重(PRE_EMPHASIS)功能可以针对某些I/O标准在驱动上进行预加重。此属性必须与 ENABLE_PRE_EMPHASIS结合使用。

表1-13:在DDR4应用中使用PRE_EMPHASIS属性时的典型预加重增益

| 属性 |

值 |

估计增益(dB) |

| PRE_EMPHASIS (HP I/O bank)的OUTPUT_IMPEDANCE为40Ω. |

RDRV_240(1) |

2.5 |

使用LVDS发射器器预加重(LVDS_PRE_EMPHASIS)功能可以针对某些I/O标准在驱动上进行预加重。此属性必须与 ENABLE_PRE_EMPHASIS结合使用。

表1-14:使用LVDS_PRE_EMPHASIS属性时的典型预加重增益

| 属性 |

值 |

估计增益(dB) |

| LVDS_PRE_EMPHASIS (HP I/O bank) |

TRUE(1) |

4 |

| LVDS_PRE_EMPHASIS (HR I/O bank) |

TRUE(1) |

4 |

均衡

接收器均衡(EQUALIZATION)功能可以针对某些I/O标准在接收器上进行均衡。 EQUALIZATION属性的允许值为: HP I/O bank • EQ_LEVEL0 • EQ_LEVEL1 • EQ_LEVEL2 • EQ_LEVEL3 • EQ_LEVEL4 • EQ_NONE(默认值) HR I/O bank • EQ_LEVEL0 • EQ_LEVEL0_DC_BIAS • EQ_LEVEL1 • EQ_LEVEL1_DC_BIAS • EQ_LEVEL2 • EQ_LEVEL2_DC_BIAS • EQ_LEVEL3 • EQ_LEVEL3_DC_BIAS • EQ_LEVEL4 • EQ_LEVEL4_DC_BIAS • EQ_NONE(默认值)

Supported I/O Standards and Terminations

LVTTL

Table 1-9:Available I/O Bank Type

| HR |

HP |

| Available |

N/A |

LVTTL是3.3V的电平逻辑,只能在HRbank使用,支持的属性如下表所示:

Table 1-10:Allowed Attributes for the LVTTL I/O Standards

| Attributes |

Primitives |

|

|

|

IBUF/IBUFG |

OBUF/OBUFT/ IOBUF |

| IOSTANDARD |

LVTTL |

LVTTL |

| DRIVE |

N/A |

4, 8, 12 (default), 16, 24 |

| SLEW |

N/A |

{FAST, SLOW} |

LVCMOS

Table 1-11:Available I/O Bank Type

| HR |

HP |

| Available |

Available |

LVCMOS所有的bank都支持,主要的7系列支持的标准有:LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25, and LVCMOS33

Table 1-12:Allowed Attributes for the LVCMOS33 and LVCMOS25 I/O Standards

| IOSTANDARD |

Attributes |

Primitives |

||

| IBUF/IBUFG |

OBUF/OBUFT/ IOBUF |

|||

| HP I/O Banks |

HR I/O Banks |

|||

| LVCMOS33, LVCMOS25 |

DRIVE |

N/A |

4, 8, 12, 16 |

|

| LVCMOS33, LVCMOS25 |

SLEW |

N/A |

{FAST, SLOW} |

|

| LVCMOS18 |

DRIVE |

N/A |

2, 4, 6, 8, 12, 16 |

4, 8, 12, 16, 24 |

| LVCMOS18 |

SLEW |

N/A |

{FAST, SLOW} |

{FAST, SLOW} |

| LVCMOS15 |

DRIVE |

N/A |

2, 4, 6, 8, 12, 16 |

4, 8, 12, 16 |

| LVCMOS15 |

SLEW |

N/A |

{FAST, SLOW} |

{FAST, SLOW} |

| LVCMOS12 |

DRIVE |

N/A |

2, 4, 6, 8, 12, 16 |

4, 8, 12 |

| LVCMOS12 |

SLEW |

N/A |

{FAST, SLOW} |

{FAST, SLOW} |

LVDCI

Table 1-16:Available I/O Bank Type

| HR |

HP |

| N/A |

Available |

LVDCI的接收器和LVCMOS是一样的,但是发送器加了源端DCI阻抗匹配的功能,具体内部连接如下所示,主要支持的电平标准有LVDCI_15 and LVDCI_18.,还有一种是LVDCI_DV2电平,也是和这个一样,只不过内部的源端阻抗是1/2R_vrn,电平标准有两种,一个是LVDCI_DV2_15 and LVDCI_DV2_18.

HSLVDCI (High-Speed LVDCI)

Table 1-18:Available I/O Bank Type

| HR |

HP |

| N/A |

Available |

HSLVDCI 是双向接口,输出是LVDCI的,输入是HSTL和SSTL的,它比单纯的LVCMOS电平的标准输入更敏感,支持的io标准有HSLVDCI_15 and HSLVDCI_18.

HSTL

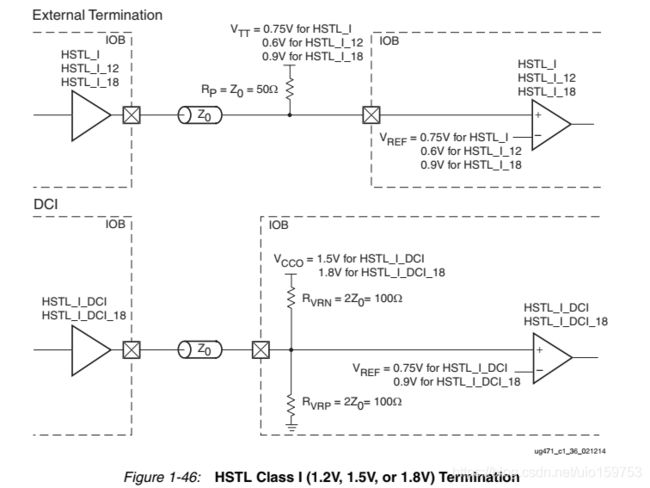

HSTL总共有4种类型,为了支持高速存储器的接口,还支持差分版本,FPGA支持的主要是第一类和第二类的接口。而且hp接口支持DCI功能。

HSTL_ I and HSTL_ I_18 : HP和HRbank都有, 采用并联端接到VTT(VTT=VCCO/2),采用的是单向链路,

HSTL_I_12 : 只能HP bank ,单向链路,也是并联端接到VTT。

HSTL_ I_DCI and HSTL_ I_DCI_18 :只能HP bank可用,能够支持戴维南等效的DCI功能,也是单一方向链路。

HSTL_ II and HSTL_ II_18 :HR和HPbank 都有,这个可以支持双向接口。也是一样的并联端接到VTT

HSTL_ II_DCI and HSTL_ II_DCI_18 :只能HPbank ,支持片内的戴维南等效,也是双向的端口

HSTL_ II_T_DCI and HSTL_ II_T_DCI_18:只能HPbank ,可以支持当发送的时候是三态的时候,接收端支持DCI的戴维南等效,但如果driver不是三态的话就不能端接。

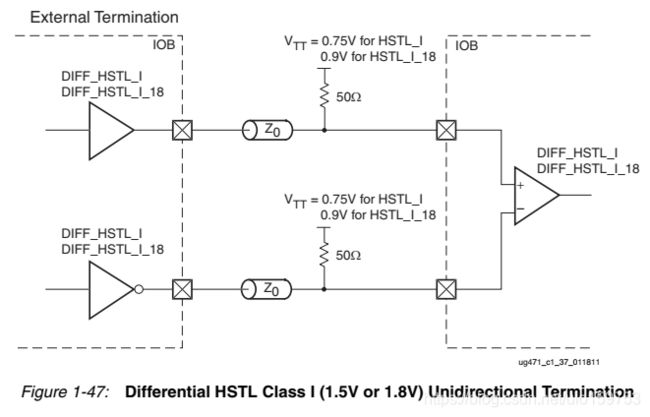

DIFF_HSTL_I and DIFF_HSTL_I_18:差分的hstl ,HR和HPbank都行,是单向的接口

DIFF_HSTL_I_DCI and DIFF_HSTL_I_DCI_18 : class I的差分的HSTL,带有片内的DCI戴维南等效。单向接口

DIFF_HSTL_ II and DIFF_HSTL_II_18 :class II的差分的HSTL,HR和HPbank都行,是双向的端口,

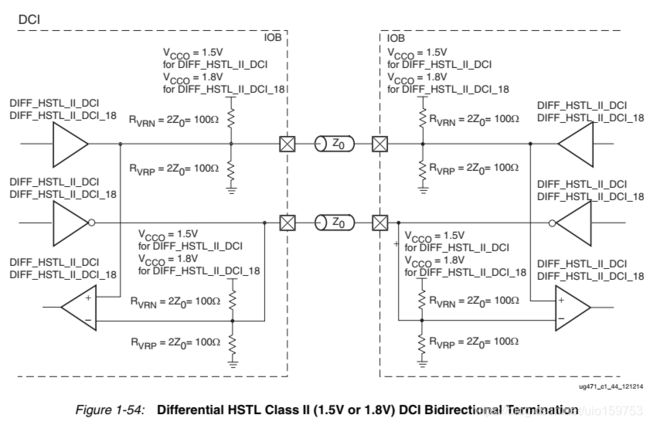

DIFF_HSTL_II_DCI and DIFF_HSTL_II_DCI_18 :HPbank 可以用,双向端口,支持DCI功能,

DIFF_HSTL_II_T_DCI and DIFF_HSTL_II_T_DCI_18 :和上面那个差不多,只不过是要想端接的话需要驱动器是三态的时候才可以

HSTL class I 是必须要收发都是相同的电平标准才行,支持的电平时1.2V,1.8V, 1.5V.连接方式的话如下所示:支持DCI功能的是HPbank 的,

差分的端接和单端的一样,没啥变化,就放一个片外的吧,片内的也是差不多和上面一样。

HSTL Class II

class II 支持单向和双向的接口,单向和双向都是只能支持1.5V和1.8V两种电压,单向的就是下面这种端接方式,输入输出都可以端接。双向的也差不多,结构是类似的。

差分的互联如下所示,这是带了DCI功能并且是双向的接口的

如果是带T的,那么驱动输出就不能端接,输入可以端接。具体如下:

SSTL

SSTL适用于1.8V,1.5V,1.35V,,主要是存储器接口用的多,class I只能用于单向拓扑,不支持双向,class II 支持双向和单向,SSTL18是DDR2的接口电平标准,SSTL15是DDR3的标准,SSTL135是DDR3L的标准,SSTL12适合DDR4的

对于SSTL接口标准用于DDR进行操作,

HPbank : SSTL18_II_T_DCI、SSTL15_T_DCI、SSTL135_T_DCI、SSTL12_T_DCI这种带三态和DCI的一般用于双向DQ管脚和DQS管脚,其他的单向接口就用SSTL18_II、SSTL15、SSTL135、SSTL12标准,内部的ODT一般给存储器的双向接口,外部的并联端接一般是给单向接口的,一般端接到VTT,(VCCO/2)

HR bank : SSTL18_II、SSTL15、SSTL135用在DQ和DQS这样的双向接口上以及单向接口上,可以结合IN_TERM 属性来在双向接口上来实现片上端接,然后外部端接电阻到VTT来实现单向接口。

SSTL15_R, SSTL135_R, DIFF_SSTL15_R, DIFF_SSTL135_R : HRbank可用,带R是降低驱动能力的版本,可以用在短距离的点对点的板卡拓扑上面,

SSTL18_I, DIFF_SSTL18_I :HR和HPbank都可以用,但是只能是单向的,class I用于短路径和点对点的板卡走线拓扑,只能采用外部端接

SSTL18_I_DCI, DIFF_SSTL18_I_DCI :HPbank可以用 ,只能是单向的,DCI可以支持片内的端接操作。

SSTL18_II, SSTL15, SSTL135, DIFF_SSTL18_II, DIFF_SSTL15, DIFF_SSTL135 :HP和HRbank都可以用,支持双向接口,不支持片内端接。

SSTL18_II_DCI, SSTL_15_DCI, SSTL135_DCI, DIFF_SSTL18_II_DCI, DIFF_SSTL_15_DCI, DIFF_ SSTL135_DCI: 只能HPbank,双向接口,支持片内戴维南等效。

SSTL18_II_T_DCI, SSTL15_T_DCI, SSTL135_T_DCI, DIFF_SSTL18_II_T_DCI, DIFF_SSTL15_T_DCI, DIFF_ SSTL135_T_DCI:只能HPbank ,双向接口支持片内戴维南等效,输入端接的时候,输出需要时三态。

SSTL12, SSTL12_DCI, SSTL12_T_DCI, DIFF_SSTL12, DIFF_SSTL12_DCI, DIFF_SSTL12_T_DCI : 只能HPbank可以用,双向,支持片内戴维南等效,输入端接的时候,输出需要时三态。

电路连接和HSTL一样,没啥变化。

HSUL_12 (High Speed Unterminated Logic)

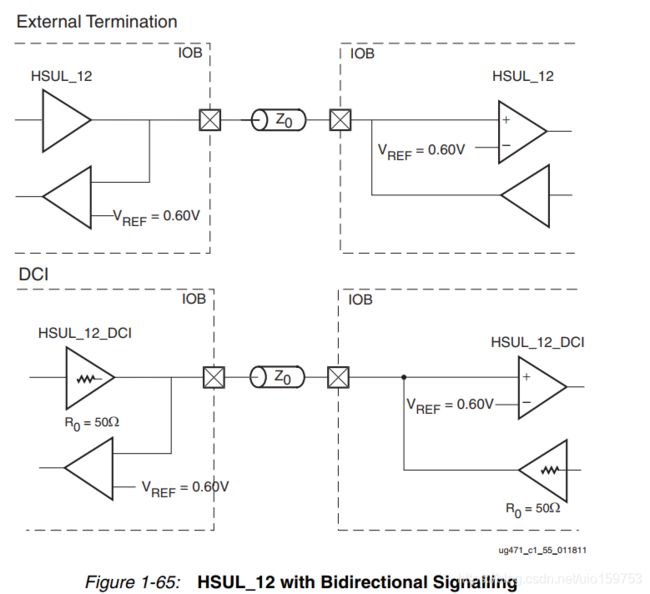

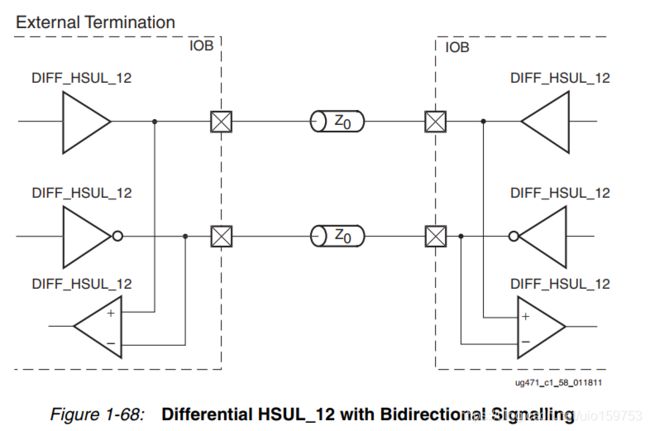

HSUL是LPDDR2的接口标准,HPbank 和HRbank都可以用,主要的规范有HSUL_12 and DIFF_HSUL_12 ,分别是差分的和单端的,连接不用端接,没有VTT端接电压,

HSUL_DCI_12 and DIFF_HSUL_12_DCI,这是带DCI端接的版本,

具体互联电路如下所示,带端接的就是普通的源端端接,不支持戴维南等效的端接。

MOBILE_DDR (Low Power DDR)

HRbank可用,主要是给LPDDR用的手机上的DDR芯片,一般是单端的,但是不需要Vref和VTT电压,有差分和单端的两种规格

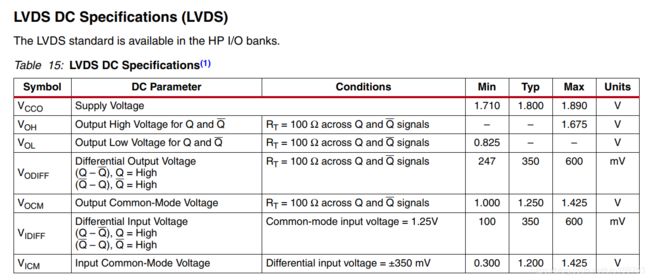

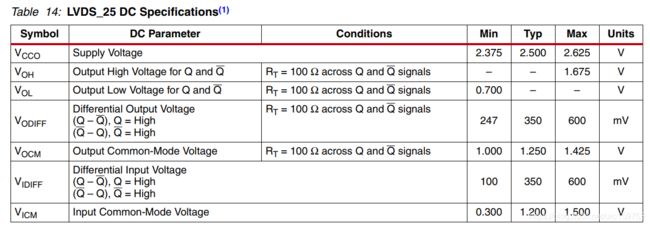

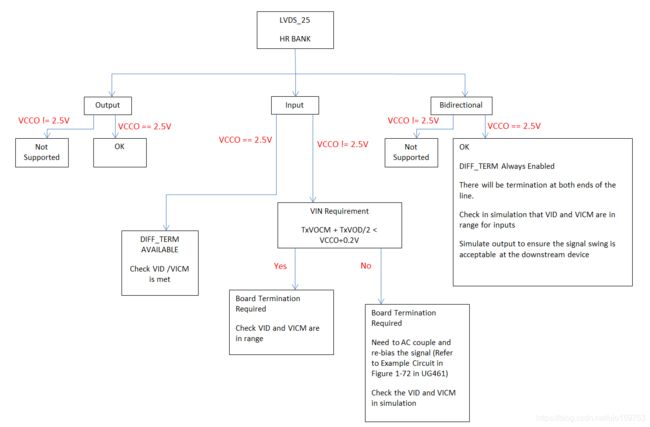

LVDS and LVDS_25 (Low Voltage Differential Signaling)

Table 1-43:Available I/O Bank Type

| HR |

HP |

| Available for LVDS_25 only |

Available for LVDS only |

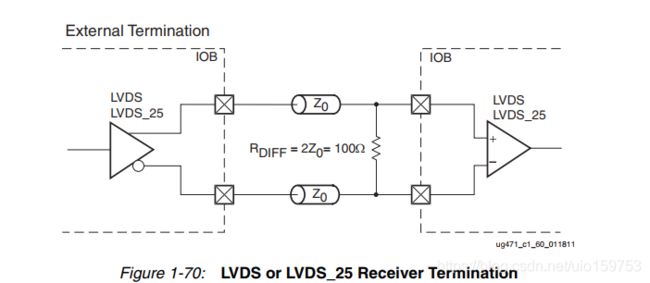

LVDS 电平分为LVDS和LVDS_25,这两个如果想要LVDS有内部端接的功能,那么就需要电源电压为1.8V和2.5V,1.8V的只能HPbank ,2.5V只能HRbank

LVDS电平有两种端接方式,具体如下,一个是采用外部的电阻进行端接,一个是内部的电阻进行端接,

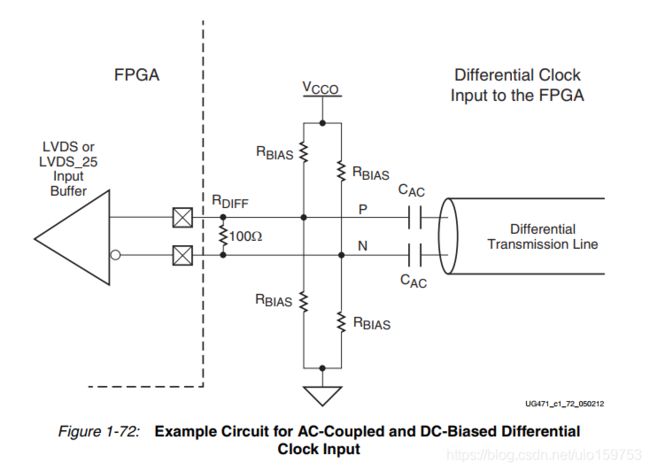

当然,其实也是支持其他的电压供电,然后LVDS电平输入的,但是它需要满足1、内部端接不能使用,另外,输入电压的范围需要满足手册里面的规范要求。

因此为了满足这个要求的话,保险的做法可以是交流耦合,然后接收端进行端接和直流偏置。偏置电阻用10K-100K的电阻

LVDS有非常强的兼容性,对于7系列的FPGA 来说已经没有了LVDS_33的电平标准,HRbank 只支持VCCO=2.5V ,HPbank 只支持1.8V,只有这两种电平的情况下才能够实现LVDS的输出,但是如果接口电平不是2.5V和1.8V的情况下,比如HRbank电平是3.3V,实际操作中,也是可以实现LVDS的约束的,只是需要有两种约束条件:

-

DIFF_TERM属性需要时FALSE,也就是说不支持片内端接,只能通过外部端接来实现

-

VOD和VOCM,也就是LVDS的共模和差模电压需要在手册的要求范围以内,具体的情况这里列出来

具体的LVDS管脚的操作逻辑如下图所示

RSDS(Reduced Swing Differential Signaling)

Table 1-45:Available I/O Bank Type

| HR |

HP |

| Available |

N/A |

RSDS 和LVDS_25实现起来比较像,只能在HRbank里面用,供电电压一定要是2.5V,支持内部差分端接

Mini-LVDS (Mini Low Voltage Differential Signaling)

Table 1-47:Available I/O Bank Type

| HR |

HP |

| Available |

N/A |

mini LVDS只能在HRbank 上用,并且只能是供电电压是2.5V,一般用作LCD的驱动和时序控制

PPDS (Point-to-Point Differential Signaling)也是和mini lvds差不多,也是LCD上用的,下一单面板的驱动,供电电压也是2.5V,能够内部端接。

TMDS (Transition Minimized Differential Signaling)

Table 1-51:Available I/O Bank Type

| HR |

HP |

| Available |

N/A |

这个是用在DVI节后和HDMI视频接口上的,TMDS需要外部用电电压是3.3V,TMDS要求输入外部50欧姆电阻上拉到3.3V

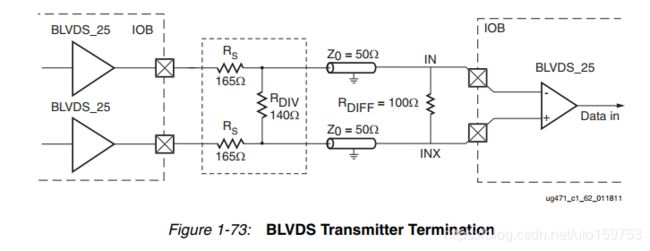

BLVDS

BLVDS可以在HRbank 上用,因为LVDS只能是点对点的通信,主要的变化还是说是可以用两个单端的管脚来驱动LVDS,需要外部供电是2.5V,而且外部端接。

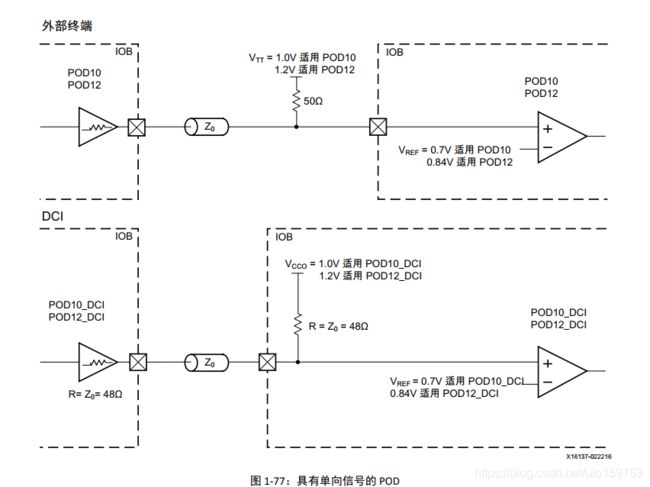

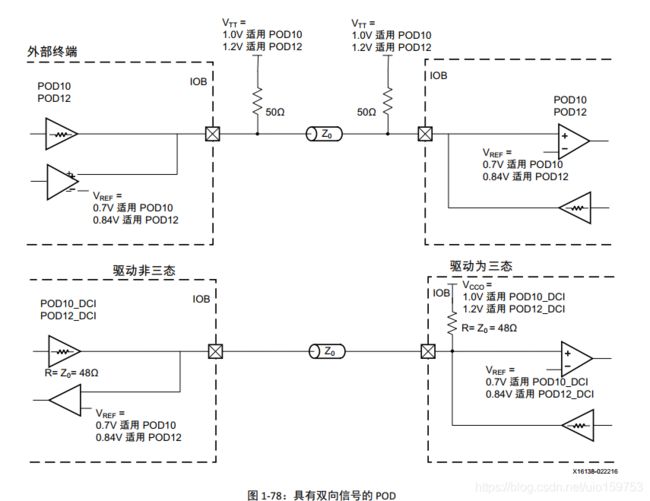

POD(Pseudo Open Drain)

伪漏极开路标准,POD12和POD10适用于DDR4和DDR4L以及LLDRAM3,D12和POD10仅在HP I/O bank中可用。都需要使用Vref

POD10、POD12、DIFF_POD10和DIFF_POD12 : 差分(DIFF_)版本 (DIFF_POD10和DIFF_POD12)使用互补单端驱动作为输出,并使用差分接收器作为输入。可选的未调整拆分输入ODT提供上拉 (连接至VCCO) 。未调整的片上源极终端功能(OUTPUT_IMPEDANCE)为HP I/O bank 中的驱动阻抗提供的选项为40Ω、48Ω,或60Ω。驱动输出阻抗设置为默认值40Ω。POD12标准在接收器中还具有可 选的EQUALIZATION和OFFSET_CNTRL功能,在驱动中具有PRE_EMPHASIS。

POD10_DCI、POD12_DCI、DIFF_POD10_DCI和DIFF_POD12_DCI: 只在HPbank可用,支持片内的DCI端接,另外POD12标准还支持均衡和预加重的功能,以及vref的偏移功能;

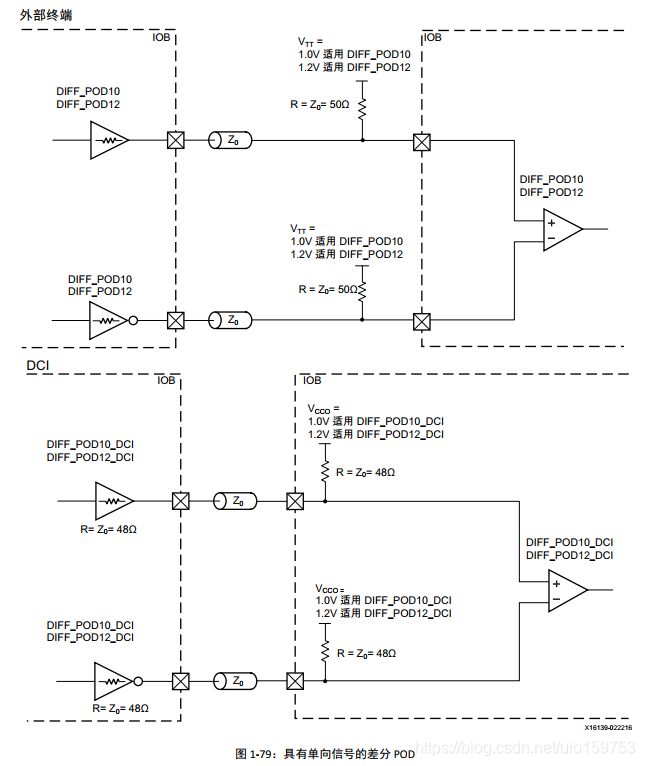

具体互联电路如下所示

双向差分的互联也差不多,我就不粘贴了。

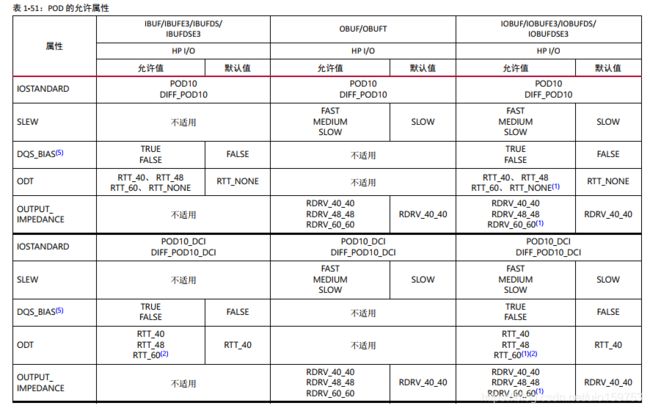

一下是几个接口支持的属性biao

表1-51:POD的允许属性

LVPECL

LVPECL仅在HR I/O bank中受支持,并且仅适用于接收器。LVPECL I/O标准的允许属性。这暗示对于表1-73中列出的原语派生的原语 (例如:_DIFF_OUT、 *_DCIEN、*_IBUFDISABLE或*_INTERMDISABLE),同样可予以支持。

表1-72:可用的I/O bank类型

| HR |

HP |

| 可用 |

不适用 |

表1-73:LVPECL I/O标准的允许属性

| 属性 |

原语 |

|

|

|

IBUFDS |

OBUFDS或OBUFTDS |

| IOSTANDARD |

LVPECL(仅限HR I/O bank) |

不适用 |

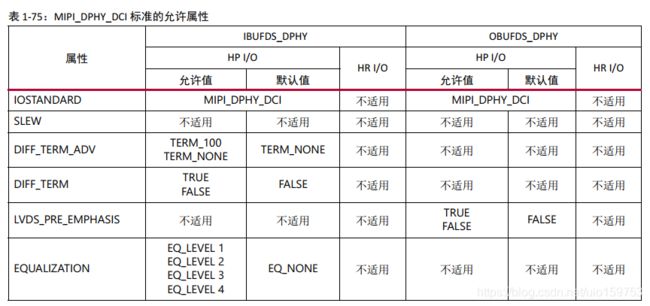

MIPI D-PHY

MIPI D-PHY标准MIPI_DPHY_DCI旨在供移动器件 (包括摄像头、显示器和统一协议接口)使用。仅限Virtex UltraScale+、Kintex UltraScale+和Zynq UltraScale+器件的HP I/O bank才支持该标准。UltraScale器件对此标准的支 持符合MIPI联盟接口规范。

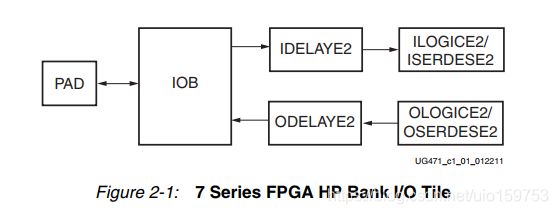

SelectIO Logic Resources

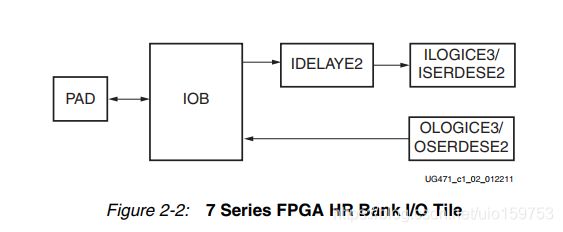

HPbank 的IO的内部资源如下所示

HRbank 相对HPbank 来说少了一个ODELAy

HRbank

UltraScale

bank简介

每个I/O bank包含52个管脚,可采用适合该bank的单端标准进行输入、输出或双向操作。I/O bank可以是高量程 (HR)或高性能(HP) I/O bank。这些管脚中最多有48个可以配置为24个差分信号管脚对,其信号标准适用于HR I/O bank或HP I/O bank。在本用户指南中,与每个单端管脚关联的逻辑称为位slice,对于_P管脚,差分管脚对称为主位 slice,对于_N管脚,称为从位slice。

有两个可用的PLL与同一I/O bank中的位slice相关联。每个PLL都具有与位slice的控制器的专用高速时钟连接,此 外还有两个额外输出,可用作为置于I/O bank覆盖的时钟区域中的逻辑的应用时钟。混合模式时钟管理器(MMCM)可 用作I/O bank中的位slice控制器和置于I/O bank所覆盖的时钟区域中的逻辑的时钟源, 但是MMCM也可以作为整个 FPGA中I/O bank和逻辑的时钟源。

每个bank被细分为4个字节组,每个组包含13个I/O管脚,如图2-1所示。每个字节组被进一步细分为2个半字节 组,两个中央字节组 (1和2)各都包含支持四字节时钟(QBC)和全局时钟(GC)功能的时钟输入管脚或管脚对。QBC管脚 可在布局到的半字节组或字节组中用作为捕获时钟输入,但它们也可以通过专用时钟基干向I/O bank中的所有其它半 字节组和字节组提供捕获时钟。GC管脚是可以驱动MMCM和/或PLL原语的时钟输入。其中一些具有时钟功能的输入 具有双重功能- QBC和GC。上字节组和下字节组各含支持专用字节时钟(DBC)功能的时钟输入管脚 (管脚对) ,这些 输入管脚或管脚对可用于字节组内部时控,但不能将捕获时钟驱动到I/O bank中的其它字节组,也不能驱动I/O bank 中的MMCM或PLL。

HD bank

高密度(HD) I/O bank属于SelectIO资源,旨在支持电压范围介于1.2V到3.3V之间的各种I/O标准。HD I/O专为单端 电压参考伪差分I/O标准而经过最优化,支持以最高250 Mb/s的数据率运行。此外还可对真差分输入 (含外部终端) 提供有限支持,以支持LVDS和LVPECL时钟输入。HD I/O还包含接口逻辑,包括寄存器和静态延迟线,用于支持异步 接口、系统同步接口和基于时钟的源同步接口。

HD bank 不支持LVDS的输出,还有SSTL和HSTL接口可选50欧姆输入终端,支持传统芯片对芯片的接口,但是不支持DRAM内存器件接

表3-1:HD I/O bank中受支持的特性

| 功能特性 |

HD I/O bank支持 |

| 3.3V I/O标准 |

LVTTL和LVCMOS |

| 2.5V I/O标准 |

LVCMOS和LVDS(1) |

| 1.8V I/O标准 |

LVCMOS、SSTL(2)(3)和HSTL(2)(3) |

| 1.5V I/O标准 |

LVCMOS、SSTL(2)(3)和HSTL(2)(3) |

| 1.35V I/O标准 |

SSTL(2)(3) |

| 1.2V I/O标准 |

LVCMOS、SSTL(2)(3)和HSTL(2)(3) |

| LVDS和LVPECL |

受支持的输入 (含外部终端) 。(1) |

| VREF |

HD I/O bank中支持的内部VREF(无外部VREF)。 |

| 最大数据速率 |

250 Mb/s |

| 输出驱动强度控制 |

支持 |

| 输出斜率控制 |

支持 |

| 上拉、下拉和保持器 |

支持 |

| 用于SDR和DDR接口的ILOGIC |

支持 |

| 用于SDR和DDR接口的OLOGIC |

支持 |

| ZHOLD(针对0保持时间的静态延迟) |

支持 |

| 内部差分终端(DIFF_TERM) |

不支持 |

| 数控阻抗(DCI)和DCI级联 |

不支持 |

| ISERDES和OSERDES |

不支持 |

| 可编程延迟 (IDELAY和ODELAY) |

不支持 |

| DQS_BIAS |

不支持 |

HD I/O支持的标准

可根据各种I/O标准来配置SelectIO管脚。 •单端I/O标准 (LVTTL和LVCMOS) •电压参考I/O标准 (SSTL、HSTL和HSUL) •伪差分I/O标准 (差分SSTL和差分HSTL) •真差分输入 (LVDS和LVPECL)

表3-2:HD I/O支持的标准

| I/O标准 |

驱动功能 |

接收器功能 |

|

| DRIVE |

SLEW |

ODT |

|

| LVCMOS12(1)(2) |

4、8和12 |

SLOW和FAST |

- |

| LVCMOS15(1)(2) |

4、8、12和16 |

SLOW和FAST |

- |

| LVCMOS18(1)(2) |

4、8、12和16 |

SLOW和FAST |

- |

| LVCMOS25(1)(2) |

4、8、12和16 |

SLOW和FAST |

- |

| LVCMOS33(1)(2) |

4、8、12和16 |

SLOW和FAST |

- |

| LVTTL(1)(2) |

4、8、12和16 |

SLOW和FAST |

- |

| HSUL_12(1) |

- |

SLOW和FAST |

- |

| HSTL_I(1) |

- |

SLOW和FAST |

RTT_48 |

| HSTL_I_18(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL18_I(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL18_II(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL15(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL15_II(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL135(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL135_II(1) |

- |

SLOW和FAST |

RTT_48 |

| SSTL12(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_HSTL_I(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_HSTL_I_18(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL18_I(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL18_II(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL15(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL15_II(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL135(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL135_II(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_SSTL12(1) |

- |

SLOW和FAST |

RTT_48 |

| DIFF_HSUL_12 |

- |

SLOW和FAST |

- |

| LVPECL(仅限接收器)(1) |

不适用 |

不适用 |

- |

| LVDS_25(仅限接收器)(1)(3) |

不适用 |

不适用 |

- |

| SUB_LVDS(仅限接收器)(1) |

不适用 |

不适用 |

- |

| SLVS_400_25(仅限接收器)(1) |

不适用 |

不适用 |

- |

1.最大运行频率为250 Mb/s。

2.对于4mA驱动强度,最大运行频率限制为125 Mb/s。

3.对于LVDS_25输入上的VCCObank电压不存在具体要求,前提是VCCO电平足够高,并可确保管脚电压与特定UltraScale+器件 数据手册[参照2]内的“推荐工作条件”表中的Vin规格相符。

参考资料

1、AR# 43989 https://china.xilinx.com/support/answers/43989.html

2、UG471 7 Series FPGAs SelectIO Resources

3、UG571 UltraScale Architecture SelectIO Resources

4、DS191 ds191-XC7Z030-XC7Z045-data-sheet