PCIE_DMA实例三:Xilinx 7系列(KC705/VC709)FPGA的EDK仿真

一:前言

好久没写博客了,前段时间有个朋友加微信请教关于PCIe的一些学习方法。本人也不是专家,只是略知一些皮毛。对于大家反馈的问题未必能一一解答,但一定知无不言。以后我会常来博客园看看,大家可以把问题直接在评论区提出来。这篇博客是应部分网友的要求写的,Xilinx升级到7系列后,原来的pcie ip核trn接口统统转换成了axis接口,这可愁坏了之前用xapp1052的朋友,一下子不好用了,该怎么办?对此我的想法是:如果您两年左右的verilog代码经验,建议您直接使用axis接口,如果您觉得使用不方便,大可在外面再包一层您自己觉得好用的接口。博主公司有这方面的技术积累,但涉及到商业利益,我不能在此出售源代码,如有私下合作,可谈。PCIe_to_RapidIO, PCIe_to_FC, PCIe_to_Enet等各类接口转换都没问题。如果您刚接触PCIe,想要更清楚得理解axis接口的PCIe IP核是如何工作的,那么这篇系统级的博客对您将会非常有用,同时博主也会给出一个用Block_design搭的带有DMA功能的简易EP,大家只要自己写个简单的控制逻辑就可以操作EP端的DMA,对于没有经验的工程师,是一个比较容易的技术迁移。

二:前期准备

1、pcie基础还是要有,尤其是协议部分。推荐一本电子书,很经典,请耐心读它(Addison.Wesley.PCI.Express.System.Architecture.eBook-LiB.chm)下载地址:http://download.csdn.net/download/yuzeren48/7723815

2、Vivado2015.4套件

3、Modelsim64_10.5

三:具体步骤

第一部分我们要生成一个PCIe的RP端,具体操作如下:

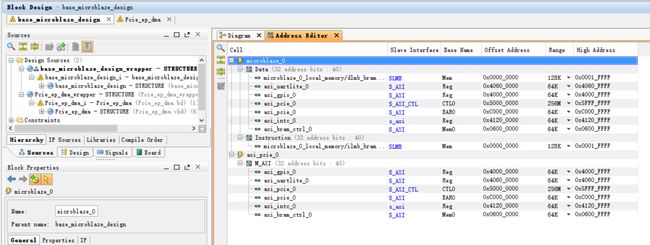

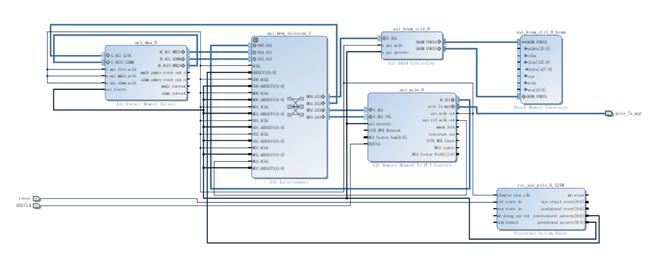

打开vivado,快速生成一个example design,选择base microblaze,按默认设置生成。手动添加axi_memory_maped_to_pcie,axi_abram_ctrl; 根据EP端的设计需求,设置RP端pcie核,本设计中链路采用4x,5G,参考时钟100M,Bar0空间64K,地址宽度32位,数据宽度128位,C_AXIBAR2PCIEBAR_0=0xFFFF0000(EP端的bar0地址),C_PCIEBAR2AXIBAR_0=0x06000000(RP端的BRAM基地址)设置gpio为output,32bit。设置bram为128位。然后自动连接,最后Generate Block Design,生成RP端系统框架如下:

2、Create HDL Wrapper 外部端口如下:

module pcie_rp_wrapper

(

output [31:0] gpio_tri_o,

input [3:0]pcie_7x_mgt_rxn,

input [3:0]pcie_7x_mgt_rxp,

output [3:0]pcie_7x_mgt_txn,

output [3:0]pcie_7x_mgt_txp,

input reset,

input rs232_uart_rxd,

output rs232_uart_txd,

input sys_diff_clock_clk_n,

input sys_diff_clock_clk_p

)

3、FILE-Export-Export hardware,生成hdf文件,File-Launch SDK;

4、进入SDK,file-new-board support packet,在该硬件平台上生成BSP。

5、在BSP的基础上搭建一个C-project,这里我们不新建工程了,而是使用pcie的example来举例,点开上图中红框import example,选择RC枚举的例子。

Build project后就可以在debug目录下看到相应的elf文件了。

6、修改rc_enmuerate_example.c文件。需要修改以下几个地方:1,去掉所有打印,使用gpio输出替代printf;2,参考xgpio_example.c ,在rc_enmuerate_example.c中增加gpio初始化,输出方向等设置;3,将PCIE_CFG_BAR_0_ADDR改为0xFFFF0000,确保在枚举的时候写入EP端配置空间的bar0基地址是PCIE_CFG_BAR_0_ADDR;4,修改PcieInitRootComplex函数中关于link_up的部分,使用do while语句来确保RP和EP能link_up;5,从SDK安装目录E:\Xilinx\SDK\2015.4\data\embeddedsw\XilinxProcessorIPLib\drivers\axidma_v9_0\src中把所有.h文件copy到SDK工程所在的bsp\microblaze_0\include下,把所有.c文件copy到src目录下,参考xaxidma_example_simple_intr.c文件配置dma,特别注意我们要根据自己ep端的设计来修xaxidma_g.c中的XAxiDma_ConfigTable。DMA这一块需要修改的东西比较多,主要是DMA收发数据时的几个Rxbuffer和Txbuffer地址要搞清楚,因为microblaze在RP端而DMA在EP端。本例中,我们一开始通过micro blaze往Txbuffer填数时,Txbuffer地址用的是RP端看过去的EP端BRAM地址。而DMA发送数据时,Txbuffer地址用的是EP端看过去的BRAM地址。如果无法准确理解,请购买附件工程。6,修改部分定义,代码里有很多for循环,次数太多影响仿真。

7、build project,在project_2.sdk\helloword_bsp_xaxipcie_rc_enumerate_example_1\Debug目录下生成elf文件。

7、打开vivado,右键board design,把elf文件关联到我们的RP端board design里,RP端的软硬件设计就算完成了。

第二部分我们要设计一个自己的PCIe EP端,具体操作如下:

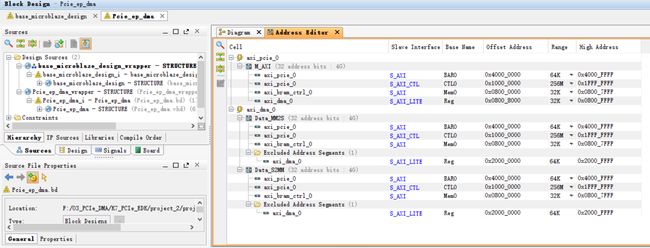

1、 在第一部分的基础上,使用ip integrator – create block design,命名为Pcie_ep_dma。添加ip核:axi_memory_maped_to_pcie,axi_abram_ctrl,axi_direct_memory_access,axi_interconnect。设置EP端pcie核,本设计中链路采用4x,5G,参考时钟100M,Bar0空间64K,地址宽度32位,数据宽度128位,C_AXIBAR2PCIEBAR_0=0xEEEE0000(RP端的bar0地址),C_PCIEBAR2AXIBAR_0=0x08000000(EP端的BRAM基地址)。设置bram数据位宽128bit。其余连线如下。

2、Create HDL Wrapper 外部端口如下:

entity Pcie_ep_dma_wrapper is

port (

REFCLK : in STD_LOGIC;

pcie_7x_mgt_rxn : in STD_LOGIC_VECTOR ( 3 downto 0 );

pcie_7x_mgt_rxp : in STD_LOGIC_VECTOR ( 3 downto 0 );

pcie_7x_mgt_txn : out STD_LOGIC_VECTOR ( 3 downto 0 );

pcie_7x_mgt_txp : out STD_LOGIC_VECTOR ( 3 downto 0 );

reset : in STD_LOGIC

);

end Pcie_ep_dma_wrapper;

完毕后,分别对EP和RP两个block design进行generate output product。选global综合。

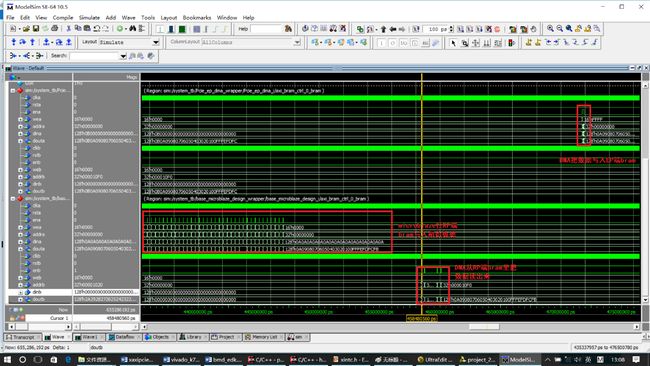

第三部分就是将EP端和RP端相连仿真了。Testbench实在太简单了这里不多说了,把EP和RP的pcie一连,接上时钟和复位就可以仿真了。仿真结果如下:

从EP->RP:

从RP到EP:

AXI_Dma上的波形:

因为发送的length设成了256字节,故一次dma的时间很短。