PCIe Architecture PHY Test Specification

本文就PCIe PHY测试的相关内容进行简要介绍,如有读者发现问题或错误,请慷慨指出,后期也会持续修正优化,谢谢!

PCIe需要进行的测试:

- PHY Test

- Configuration Space Test

- Link Layer Test

- Transaction Layer Test

- Retimer Test

PCIe Architecture PHY test测试是针对底层电气特性的测试,主要关注PCIe信号完整性测试。就整个PCIe系统而言,从PCIe的Root到Endpoint都是需要进行测试的,因此测试分为对System board的测试和对Add in Card的测试,测试项目基本相同。如下是关于System board的相关测试,参考PCIe 4.0 PHY Test Spec。

1. 发送器信号质量测试

这个测试的目的是确认系统分别运行在2.5GT/s、5.0GT/s、8.0GT/s、16.0GT/s速率时,当发送均衡设定在某些值时,PCIe信号的眼图和抖动是否满足要求。

测试需要设备运行在polling.compliance状态。

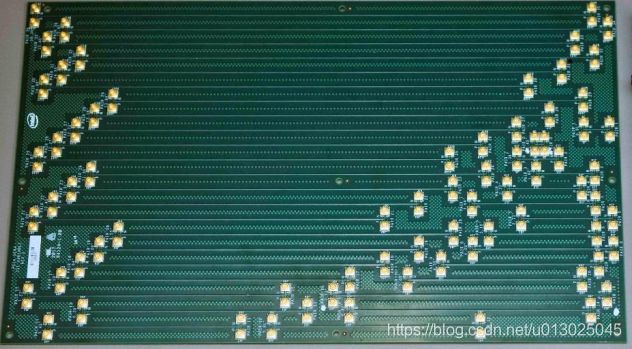

测试中需要使用到CLB(Compliance load board)板,这个板子的作用是将主板的PCIe信号转接入示波器。对于一般的系统板,其对外提供的PCIe接口一般是标准金手指插槽,这种插槽是没法直接接示波器线缆的接口的,因此这里需要一个CLB板转接,同时CLB板还提供了其他测试的辅助功能。PCIe 4.0 CLB测试板如下左图所示,测试板提供了x2、x4、x8、x16金手指,用于不同带宽情况;另,CLB板的正面和反面都装有SMP连接器,一般情况会将Tx和Rx信号分别在正面和反面连接器引出。这个测试板可以兼容测试PCIe GEN1~GEN4,测试时根据需要将不进行测试的lane进行50ohm端接。

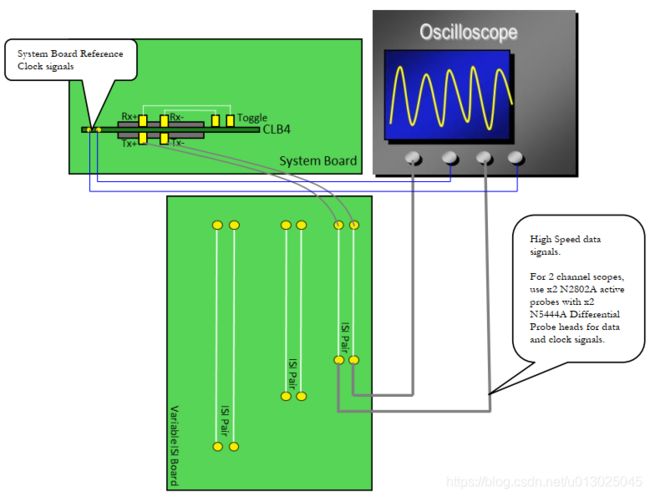

测试Tx信号质量时需要将Tx差分信号和Refclk差分时钟信号同时接入高速示波器(或均衡数据获取仪器),然后分别进行从2.5GT/s到16.0GT/s速率的电气兼容性测试。关于电气兼容性测试,需要示波器采集一定数量的数据和时钟信号,使用仪器的软件绘制出眼图,得到眼高和眼宽数据。对眼图是否满足要求的判断需要使用到一个眼图模板,这个模板会根据传输速率、发送均衡值以及测试设备变更。

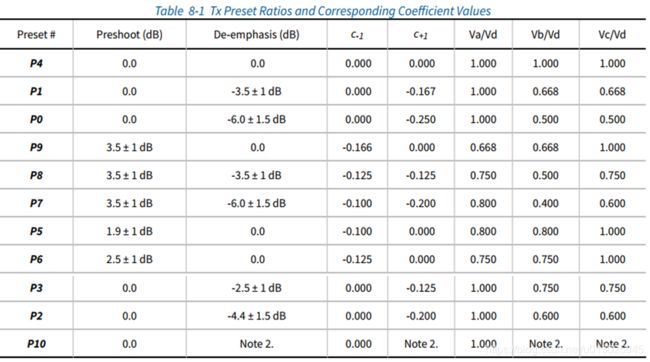

测试过程中需要操作CLB板上的按键来调整发送均衡值,使用这个按键需要将按键的SMA或SMP连接器通过线缆接到CLB Rx接口面的Rx lane0。PCIe GEN2发送均衡值只有2个,3dB和6dB的de-empahsis;GEN3/GEN4均衡值组合较多,协议给出了11组preset值用于优选。通过按键调整均衡值进行眼图测试,测试软件给出测试结果。

GEN2和GEN3的测试差异主要在按键对均衡值的调整,GEN4的测试增加了ISI板(如上右图所示)用于PCIe物理链路衰减(提供8GHz频点5dB的插损),Tx链路从CLB板先接到ISI板进行衰减,再从ISI板接到示波器;此时参考时钟并不接到ISI板,仍是直接从CLB板接到示波器。

2. 发送器preset测试

这个测试针对PCIe GEN3和GEN4进行测试(从GEN3开始使用preset),测试的目的是确认系统板端的发送器能够产生与设置的preset值相对应的均衡参数值。

测试需要设备运行在polling.compliance状态。

此测试的方法和发送器信号质量测试的方法一样,只是首先需要通过按键将系统板PCIe速率调整到需要测试的速率。波形测试完后,使用测试软件从存储的波形数据中计算出各preset值,判断是否满足对应的范围。

3. 发送器link EQ响应测试

这个测试针对PCIe GEN3、GEN4及以上速率进行测试,目的是确认系统能够正确响应通过link协议发送的均衡指令。

测试需要设备运行在polling状态。

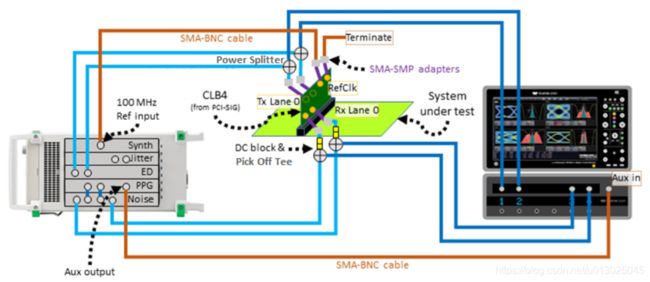

测试需要使用到具有protocal aware功能的信号发生器和接收器,例如协议测试卡(Protocal Test Card)、误码测试仪(Bit Error Rate Tester),信号发生器和接收器需要接到CLB板上,并发送指令给系统板调整发送均衡值,使系统板运行在loopback模式。

测试环境安装过程中需要将信号发生器的输出接到CLB板的Rx连接器。CLB板的Tx信号需要分成2路,1路接入protocal aware测试仪,另1路接入高速示波器。所有接入CLB的信号都必须进行phase match。

测试过程中根据测试速率要求使用测试仪器将PCIe链路速率协商到指定速率,再发送指令给系统板将preset设置为4(preset值及相对应的均衡参数如下图所示,P4表示不进行均衡调整)。

测试需要确认系统板的均衡值能够在1ms时间内调整到设置的preset。因此要求测试仪器将系统板设置到loopback模式,并发送compliance pattern码流返回个测试仪器,测试仪器从码流中提取出系统板当前的preset值。

4. Lane Margin测试

这个测试针对PCIe GEN4及以上速率进行测试,测试使用一个Gold Add-in Card进行发送信号质量的调整(例如Tx preset、电压摆幅、链路损耗、Tx抖动等),查看系统板的Time margin和voltage margin。测试的目的是确认系统板是否具有lane margin的能力,并不检查具体的margin值。

测试需要将测试卡Gold Add-in-Card插入系统板的PCIe插槽,在系统板上安装Lane margin tool(LMT),通过测试卡发送不同参数信号给系统板Rx,并运行LMT测试软件,获取不同的margin值。针对不同参数的Tx信号,系统板的Rx margin值出现明显变化,则表示Rx具有margin的能力。

5. 接收器link EQ测试(误码测试)

这个测试针对PCIe GEN3、GEN4及以上速率进行测试,目的是确认系统能够和link partner正确协商,并调整partner发送器的均衡值。

测试需要将信号发生器接到CLB的Rx连接器,将protocol aware测试仪器接到CLB的Tx连接器。系统板的100MHz参考时钟也接到测试仪器以驱动测试仪器发送信号。调整protocol aware测试仪器的发送均衡以匹配系统板的要求。测试系统上电后protocol aware测试仪器将PCIe链路协商到测试的速率,再进行链路均衡协议,同时将系统板设置到loopback状态。信号发送器发送测试码流给系统板,检查测试过程中的误码是否达到![]() 要求。

要求。

关于AIC的测试以及测试相关的波形等,后续持续更新。。。