【Xilinx JTAG to AXI】PG174 JTAG to AXI文档整理

目录

概述

功能总结

应用

端口说明

核心设计

JTAG TO AXI主内核可用于AXI系统调试和测试

时钟

重置

设计流程步骤

自定义和生成核心

参数说明

综合与实现

示例设计

创建AXI事务

AXI4 示例

AXI4‑Lite 示例

JTAG to AXI 主 IP 内核是一个可定制的内核,可以生成 AXI 事务并驱动系统中 FPGA 内部的 AXI 信号。可以使用 IP 定制 Vivado 中的参数选择 AXI 总线接口协议。

概述

JTAG to AXI Master 是一个可定制的 IP 内核,可作为 AXI Master 来驱动 AXI传输。此 IP 可在 Vivado IP 集成器中使用,也可在 Vivado 项目中以 HDL 进行实例化。

图中显示了一个AXI系统,它使用JTAG TO AXI 主内核作为AXI主内核。JTAG TO AXI 主内核没有自己的地址空间,并响应您启动的所有地址。 JTAG TO AXI Master 内核可以与所有下游从机(在本例中为 S0、S1 和 S2)通信,并且可以与系统中的其他 AXI Master共存。

功能总结

- 参数化协议选择(AXI4 AXI4-Lite)

- 参数化地址位宽为32和64

- ID宽度(最多4位),允许用户定义ID信号

- 固定AXI-Lite数据位宽为32

- 参数化AXI4数据位宽为32和64

- 支持所有内存映射AXI接口传输:1、突发类型:INCR、FIXED(这两种类型突发长度支持1-256)、WRAP(突发长度支持2、4、8、16)

- 支持高速缓存信号

- 硬件调试运行时间 Tcl 控制台控制同时读/写

应用

JTAG TO AXI主内核可用于需要调试基于AXI的IP或系统的嵌入式和非嵌入式系统。此外,这可以在测试期间用于驱动AXI事务,作为硬件上的测试向量,并且可以用作AXI流生成器。ILA IP内核可用于监控JTAG TO AXI主控器的AXI端口上的流。

不支持的功能

- 狭义传输

- 安全功能

- 地址流水线

- 乱序传输

最大频率

JTAG TO AXI主内核设计为以高达200Mhz的设计时钟频率运行,但最大时钟频率可能会受到设计中其他因素的限制,例如整体利用率或布线拥塞。

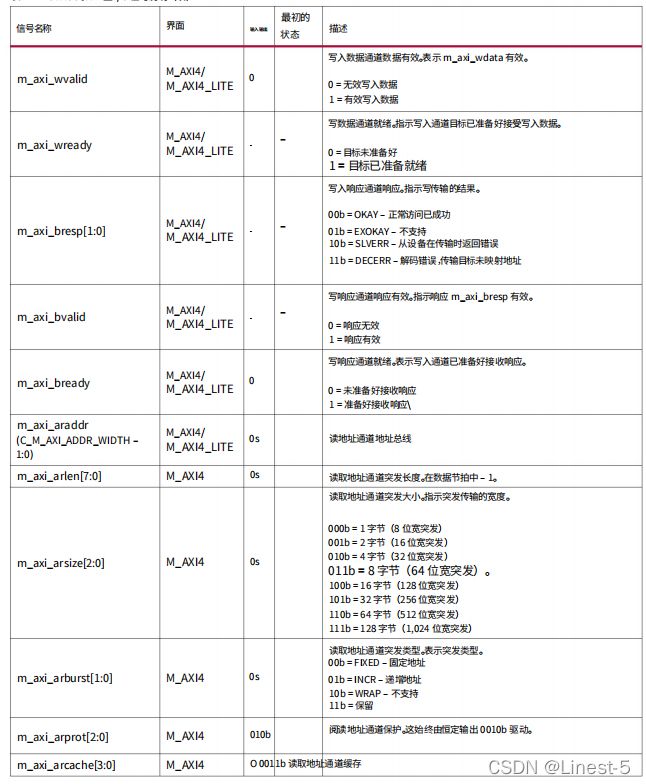

端口说明

核心设计

JTAG TO AXI主内核可用于AXI系统调试和测试

时钟

axlk输入端口被JTAG TO AXI主内核用作AXI接口上的时钟端口。所有的AXI信号都是基于aclk的上升沿生成或采样的。必须将其连接到设计中的正确时钟源。

重置

aresetn输入端口用作AXI接口上的JTAG TO AXI主内核的复位端口。这是一个低电平有效的同步信号,并根据aclk进行采样。当JTAG TO AXI主内核在aclk的上升沿将其采样为低电平时,逻辑的AXI侧被复位。

设计流程步骤

这里描述了内核的定制和生成、内核的约束以及特定于该 IP 内核的仿真、综合和实现步骤。有关标准 Vivado设计流程和 Vivado IP 集成器的更多详细信息,请参阅以下 Vivado Design Suite 用户指南:

UG994、UG896、UG910

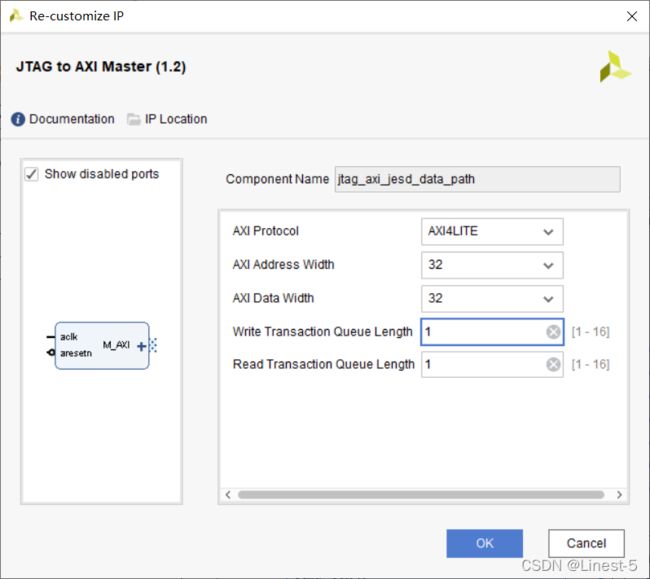

自定义和生成核心

JTAG to AXI 主内核可以在 Vivado IP 目录的 /Debug & Verification/Debug 中找到。

1. 从 IP 目录中选择 IP。

2. 双击选定的 IP 或从工具栏中选择自定义 IP 命令或右键菜单。

单击 Vivado IP 目录中的 JTAG to AXI Master 时的 Customize IP 窗口

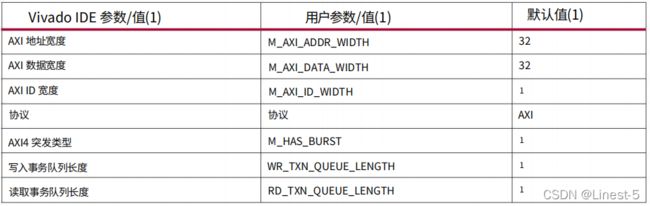

参数说明

- Component Name:使用此文本字段为 ILA 核提供唯一的模块名称

- AXI Protocol:选择AXI4接口协议

- AXI Address Width:选择AXI4地址宽度(32或64)

- AXI Data Width:选择数据宽度(32或64)

- AXI ID Width:选择ID宽度,范围为1-4

- AXI4 Burst Type Support:选择所有突发类型,例如FIXED、INCR和仅WRAP或INCR突发

- Write Transaction Queue Lengt: 选择队列中的最大写入事务数。所有排队的事务都是背靠背发出的。默认值为1,范围为1到16。

- Read Transaction Queue Length:选择队列中读取事务的最大数量。所有排队的事务都是背靠背发出的。默认值为1,范围为1到16。

Vivado IDE参数与用户参数的关系

约束核心

所需的约束

JTAG TO AXI 主内核包括一个 XDC 文件,其中包含适当的多周期路径约束,以防止时钟域交叉同步路径的过度约束。

还可能需要连接到 JTAG TO AXI 主内核的 aclk 输入端口的时钟信号在设计约束中得到适当的约束。

综合与实现

在硬件中与JTAG交互到AXI主内核

JTAG TO AXI 主内核只能使用 Tcl 控制台命令进行通信。

可以使用这些 Tcl 控制台命令创建和运行 AXI 读写事务。

这些 Tcl 控制台命令和与内核交互的方法的完整列表可在Vivado 设计中标题为“Debugging Logic Designs in Hardware”一章的

“Hardware System Communication Using the JTAG-to-AXI Master Debug Core”部分中找到套件用户指南:Programming and Debugging (UG908)。

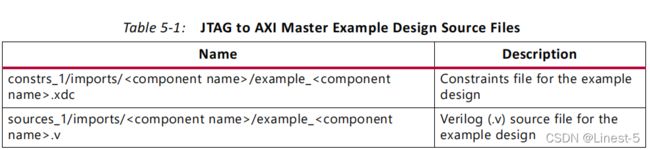

示例设计

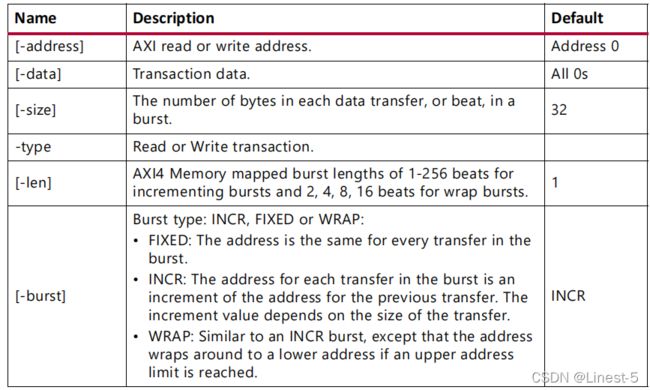

创建AXI事务

下面列出了在 AXI4 和 AXI4‑lite 中创建 AXI 事务的两个示例:

AXI4 示例

使用 8 个 32 位数据创建一个写入 AXI 突发事务:

create_hw_axi_txn wr_txn [get_hw_axis hw_axi_1] ‑address 00000000 ‑data

{11111111_22222222_33333333_44444444_55555555_66666666_77777777_88888888} ‑len 8 ‑size 32使用 8 个 32 位数据创建读取 AXI 突发事务:

create_hw_axi_txn rd_txn [get_hw_axis hw_axi_1] ‑address 00000000 ‑len 8 ‑size 32 ‑type read使用 8 个 32 位数据和 64 位地址创建一个写入 AXI 突发事务:

create_hw_axi_txn wr_txn64 [get_hw_axis hw_axi_1] ‑address 0000000000000000 ‑data {11111111_22222222_33333333_44444444_55555555_66666666_77777777_88888888‑type创建一个包含 8 个 32 位数据和 64 位地址的读取 AXI 突发事务:

create_hw_axi_txn rd_txn64 [get_hw_axis hw_axi_1] ‑address 0000000000000000 ‑len 8 ‑size 32‑type readAXI4‑Lite 示例

使用 8 个 32 位数据创建一个写入 AXI 事务:

create_hw_axi_txn wr_txn_lite [get_hw_axis hw_axi_1] ‑address 00000000 ‑data 12345678 ‑type write创建一个包含 8 个 32 位数据的读取 AXI 事务:

create_hw_axi_txn rd_txn_lite [get_hw_axis hw_axi_1] ‑address 00000000 ‑type read发起AXI传输

在此示例中,通过将队列设置为四个,连续发出四个事务。

读写事务是独立执行的。但是,如果在队列事务列表中混合了读取和写入事务,则读取事务将首先启动。

run_hw_axi txn_1 txn_2 txn_3 txn_4 -queue

create_hw_axi_txn创建一个硬件 AXI 事务对象,其中:

create_hw_axi_txn [-address ] [-data ] [-size ] -type [-len ] [-burst ] [-cache ] [-id ] [-quiet] [-verbose] 解释

run_hw_axi运行硬件AXI读/写事务并在hw_axi中更新事务状态目的。

句法

run_hw_axi [‑queue] [‑quiet] [‑verbose] ...解释

文件命名原则

component name:组件名称

以上为PG174 Jtag to Axi的详细介绍。