Moore型状态机和Mealy型状态机的区别以及各自Verilog的实现细节:为什么Moore型状态机需要多一个状态?怎么选择用哪一种状态机?

Moore型状态机和Mealy型状态机的区别

(1)Moore型状态机:输出信号只取决于当前状态。

(2)Mealy型状态机:输出信号不仅取决于当前状态,还取决于输入信号的值。

它们的区别就在于输出信号是否与输入信号有关,造成的结果是:

实现相同功能时,Moore型状态机需要比Mealy型状态机多一个状态,且Moore型状态机的输出比Mealy型延后一个时钟周期。

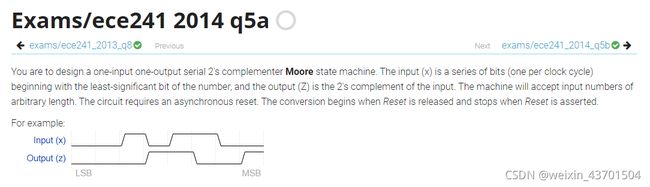

这里举一个HDLBits上的例子:

这两道题目要求分别用Moore型状态机和Mealy型状态机来实现对输入信号x的二进制补码转换。电路会对输入持续进行转换,直到复位信号到来。从两道题目给出的示例时序图可以看出,同样的输入下,Moore型状态机的输出z比Mealy型状态机延迟了一个时钟周期。

由于第二道题直接给出了状态图,我们就先从第二题的Mealy型状态机做起。

由状态图:复位信号到来,状态机进入A状态。

在A状态中,如果输入的x=0,则输出z=0,下一状态仍是A;如果输入的x=1,则输出z=1,下一个状态为状态B;

在B状态中,如果输入的x=0,则输出的z=1,下一状态仍是B;如果输入的x=1,则输出的z=0,下一个状态还是B。

由以上状态图,很容易就能写出相应的三段式状态机的Verilog代码:

module top_module (

input clk,

input areset,

input x,

output z

);

parameter A = 2'b01;

parameter B = 2'b10;

reg [1:0] state, next_state;

always @ ( posedge clk or posedge areset ) begin

if ( areset )

state <= A;

else

state <= next_state;

end

always @ ( * ) begin

case( state )

A:

next_state = x? B: A;

B:

next_state = B;

endcase

end

always @ ( * ) begin

case( state )

A:

z = x;

B:

z = !x;

endcase

end

endmodule再来考虑第一题,使用Moore状态机来解决这个问题:

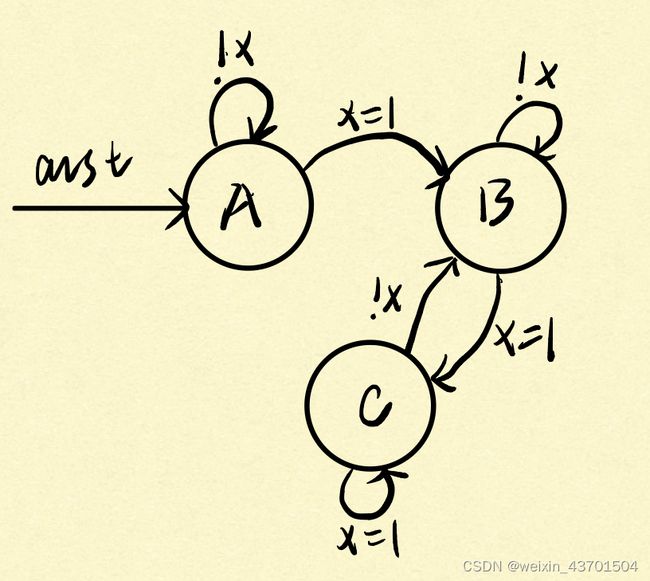

首先分析可能的状态,画出状态图:

复位信号到来,同样强制进入A状态;

A状态中,若输入的x=0,保持在A状态,x=1则进入B状态;

B状态中,若输入的x=0,保持在B状态,x=1则进入C状态;

C状态中,若输入的x=1,保持在C状态,x=0则进入B状态。

在这里,Moore型状态机比Mealy型多了一个中间状态B:因为Moore型的输出与输入无关,只与当前状态有关,所以需要多出一个状态来产生一个输出。具体而言,在Mealy型状态机中,状态A有两个输出,z=0或z=1,这两个输出的值是由输入的x来决定的(z=x)。而在Moore型状态机中,输出与输入是无关的,不能根据输入的x的值决定输出的z的值(输出的值只跟状态有关,在这里只跟状态B有关,若在状态B,输出1,不在状态B则输出0)。

相应的Verilog代码:

module top_module (

input clk,

input areset,

input x,

output z

);

parameter A = 3'b001;

parameter B = 3'b010;

parameter C = 3'b100;

reg [2:0] state, next_state;

always @ ( posedge clk )

temp <= x;

always @ ( posedge clk or posedge areset ) begin

if ( areset )

state <= A;

else

state <= next_state;

end

always @(*) begin

case ( state )

A: begin

next_state = x? B: A;

end

B: begin

next_state = x? C: B;

end

C: begin

next_state = x? C: B;

end

default: begin

next_state = A;

end

endcase

end

assign z = state==B;

endmodule由于Moore型状态机的输出与输入无关,需要多用一个状态变量产生输出。所以Moore型状态机的输出由此多了一个时钟周期的延迟。换句话说,输入输出的延迟是由于Moore状态机的输出仅仅取决于Moore状态机的当前状态。因此,在编码器使与采样或者检测到的输入相对应的输出有效之前,输入的变化必须首先使状态发生转移!

怎么选择用哪一种状态机:

通常情况下,Mealy状态机的输出容易受到输入比特流中的毛刺影响,如果系统不能承受这种影响,就必须使用Moore状态机。