计算机组成原理系统总线概念,计算机组成原理——系统总线

1、总线的基本概念

1.1什么是总线

总线是链接各个部件的信息传输线,是各个部件共享的传输介质

在任意时刻,只能有一对设备/部件使用总线异步

1.2总线上信息的传送

串行:一次传送一位数据。通常用于长距传输,如机器之间

并行:一次传送多位数据。多根线并列传输,线路过长时容易产生干扰致使接收方所得信号变形,所以通常用于短距传输,如机箱内部;可采用特殊措施实现长距传输分布式

1.3总线结构的计算机举例

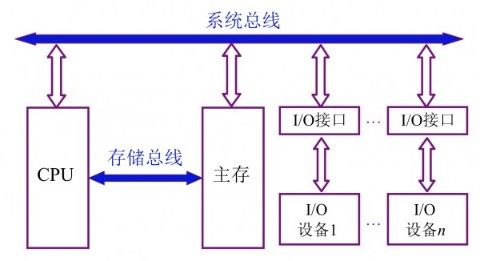

一、单总线结构框图

缺点:主存与 I/O接口链接时,CPU会中止工做,极大地下降了工做效率

二、面向 CPU的双总线结构框图

优势:CPU的指令和数据都来自主存,单独一根总线链接可提升效率

缺点:主存和 I/O设备间没有直接通路,经过 CPU中转时会致使 CPU中止工做从而下降工做效率

三、以存储器为中心的双总线结构框图

缺点:两条总线没法同时进行工做性能

2、总线的分类

2.1片内总线

芯片内部的总线设计

2.2系统总线

一、数据总线:双向;与机器字长、存储字长有关,总线宽度通常小于等于机器字长或存储字长

二、地址总线:单向:与存储地址、I/O地址有关

三、控制总线:有出(CPU发出的;存储器读/写,总线容许,中断确认),有入(发给 CPU的;中断请求,总线请求)3d

2.3通讯总线

用于计算机系统之间或计算机系统与其它系统(如控制仪表,移动通讯等)之间的通讯

传输方式:串行通讯总线,并行通讯总线blog

3、总线特性及性能指标

3.1总线特性

一、机械特性:尺寸、形状、管脚数、排列顺序

二、电气特性:传输方向、有效的电平范围

三、功能特性:每根传输线的功能:地址、数据、控制

四、时间特性:信号的时序关系(数字逻辑课程)接口

3.2总线的性能指标

一、总线宽度:数据线的根数

二、标准传输率:每秒传输的最大字节数(MBps)

三、时钟同步/异步:同步、不一样步

四、总线复用:地址线与数据线复用(就是共用)——8086的例子 "复用的目的是减小芯片的管脚数,从而减少芯片的体积"

五、信号线数:地址线、数据线、控制线的总和

六、总线的控制方式:突发、自动、仲裁、逻辑、计数

七、其余指标:负载能力(能链接几个 I/O设备)同步

3.3总线标准

4、总线控制

4.1总线判优控制

4.1.1基本概念

一、主设备/模块:对总线有控制权

二、从设备/模块:相应从主设备发来的总线命令

有的总线只容许有一个主设备,有的容许多个

三、总线仲裁决定

分为集中式和分布式,集中式下分链式查询、计数器定时查询、独立请求方式it

4.1.2链式查询方式

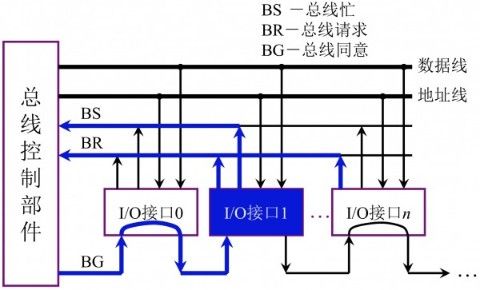

BS-总线忙,BR-总线请求,BG-总线赞成

假设接口1和 n同时发送总线占用请求,两个请求经过 BR线传入总线控制部件。控制部件肯定赞成后,从 BG线发出响应。响应先到接口0,发现它没有发送请求,因而向下查询,到接口1发现是它发送的请求,因而把控制权交给接口1,接口1获得控制权后后经过 BS线发送总线忙的消息

特色:优先级与 BG线的查询顺序有直接关系,即各个 I/O设备占用总线的优先权的前后顺序。优先权由链接方式事先肯定(若某设备优先级过低,发出的请求可能永远得不到回答)

缺点:对电路故障特别敏感。尤为是 BG线,若是某接口电路出现线路故障,该信号没法向下传,后面的设备永远没法得到总线使用权

优势:结构简单,增删设备容易,进行可靠性设计容易实现(好比 BS、BG设置成2根线,避免一根线断了没法继续工做)

4.1.3计数器定时查询

BS-总线忙,BR-总线请求

请求方式和链式查询方式差很少,可是少了条 BG线,多了条设备地址线

假设计数器初值设为0,接口1和 n同时发送总线占用请求,两个请求经过 BR线传入总线控制部件。控制部件肯定赞成后,从设备地址线发出响应。计数器目前是0,所以先检查接口0是否发送请求,发现没有,计数器加1变成1,因而检查接口1发现是它发送的请求,因而把控制权交给接口1,接口1获得控制权后后经过 BS线发送总线忙的消息

特色:优先级的设置取决于控制部件内的计数器;计数器的初值可自行设定,从而肯定优先级

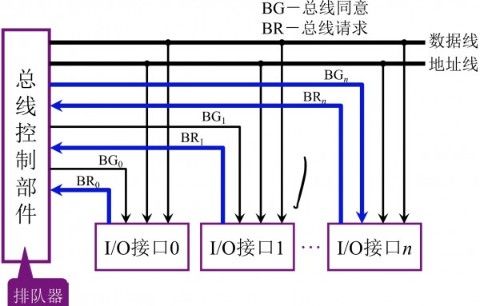

4.1.4独立请求方式

前两种都是按顺序查找,速度较慢

BR-总线请求,BG-总线赞成

特色:优先级的设置取决于控制部件内的排队器;能够事先肯定优先级,也能够经过自适应算法创建

4.2总线通讯控制

4.2.1目的

解决通讯双方协调配合问题

4.2.2总线传输周期

主设备和从设备之间完成一次完整且可靠的通讯所需时间

一、申请分配阶段:主模块申请,总线仲裁决定

二、寻址阶段:主模块向从模块给出地址和命令

三、传输阶段:主模块和从模块交换数据

四、结束阶段:主模块撤销有关信息

4.2.3总线通讯的四种方式

一、同步通讯:由统一时标控制数据传送

二、异步通讯:采用应答方式,没有公共时钟标准

三、半同步通讯:同步、异步结合

四、分离式通讯:充分挖掘系统总线每一个瞬间的潜力

详细讲解

假设 CPU从某一外部设备进行数据输入

同步通讯

特征

有一个定宽、定距的时标控制整个数据的传输过程

在固定的时间点上要给出固定的操做

全部从模块用同一个时标控制

主从模块强制同步;对速度不一样的从模块,选择最慢的做为统一的时标

一般应用在总线长度较短,各个模块存取时间比较一致的状况

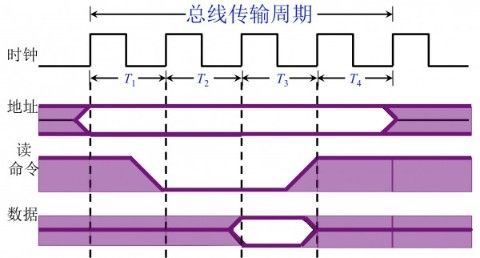

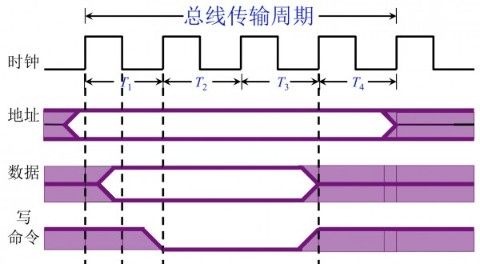

总线传输周期由四个时钟周期组成

除了时钟信号,CPU要完成数据输入(输出)的话,还须要地址信号、读(写)信号

从模块在给定时间点上给出数据的输出(输入),对 CPU来讲是数据的输入(输出)

1)同步式数据输入

过程

在第一个时钟周期的上升沿,给出地址信号,该地址信号是主模块给出的(该例中是 CPU给出的)

在第二个时钟周期的上升沿,给出读信号,告诉从模块 CPU要从从模块读入数据

在第三个时钟周期的上升沿,从模块必须给出数据信号,并经过数据总线传输

在第四个时钟周期的上升沿,数据信号和控制信号撤销

在第四个时钟周期结束的时候,地址信号撤销

2)同步式数据输出

过程

在第一个时钟周期的上升沿,给出地址信号

在第一个时钟周期的降低沿,给出数据信号

在第二个时钟周期的上升沿,给出写信号,向从模块进行数据写入

在第三个时钟周期的上升沿,做写入操做

在第四个时钟周期的上升沿,数据信号和控制信号撤销

在第四个时钟周期结束的时候,地址信号撤销

异步通讯

特征

没有定宽、定距的时钟周期,但增长了两条线:请求线(主模块发出请求信号),应答线(从模块回应主设备发送的请求)

经过请求、回答两个控制信号完成联络

不互锁

主模块发出通讯请求,从模块接收后进行应答。以后主模块撤销请求信号,从模块也撤销应答信号

主模块不论是否收到应答信号,通过必定的时延后都会撤销请求信号

从模块无论主模块是否收到应答信号,通过必定的时延后都会撤销应答信号

半互锁

主模块发出通讯请求,从模块接收后进行应答,主模块接收应答信号后撤销请求信号;若是接收不到,请求会一直保持

后果:可能形成请求信号一直高电平

全互锁

主模块发出通讯请求,从模块接收后进行应答,主模块接收应答信号后撤销请求信号,只有主模块撤销请求后,从模块才会撤销应答信号

若是传输过程当中发现数据出错,半互锁、全互锁能够请求从模块从新发送和接收数据