灭霸打个响指的功夫,看懂Verilog多维数组【Verilog高级教程】

Verilog多维数组

-

- 一、写在前面

- 二、数组的引出和要求

- 三、wire型数组

- 四、reg型数组

- 五、其他类型数组

- 六、往期【Verilog】高级教程文章

一、写在前面

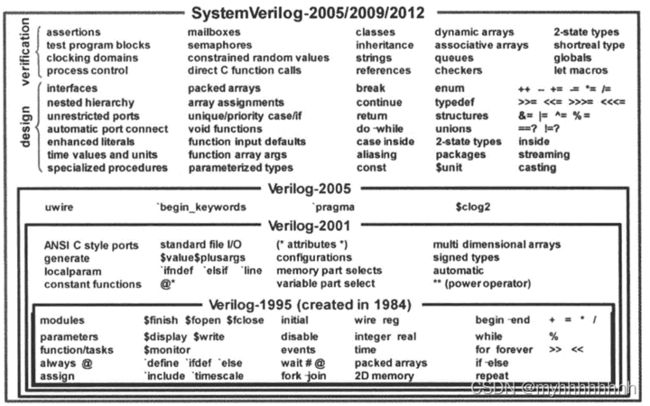

本专栏为作者在 【数字IC手撕代码】 【数字IC笔试面经分享】 【数字IC工具解析】 以外开设的第四个独立专栏,旨在学习并提供有关Verilog硬件描述语言中非基础性的高阶语法特性知识,因本身专栏的独特定位,因此作者并不会涉及基础Verilog语言如阻塞式非阻塞赋值,过程块,数据类型等内容;同时受限于作者知识有限,本专栏也不会涉及System Verilog的相关内容,若按照IEEE的相关标准来看,本专栏将会聚焦Verilog-2005,即“IEEE Std 1364™-2005”以及之前的有关内容,提供相关的IC设计领域语法特性。以下为Verilog的进阶框图,有更多学习需求的读者可以检索相关英文标准进行学习。

二、数组的引出和要求

通常情况下,我们在进行verilog设计时,端口的声明为一维的,比如

input [31:0] data_in ;

这里我们就声明了一个一维的变量,一个32位的输入端口data_in

- 那么假如我们需要二维或者更多维的变量时,是否有相对应的方式来帮助我们进行声明呢?

答案是肯定的,而这也并非毫无意义,我们可以用如下的方式进行声明,设置多维数组。

input [31:0] data_in [0:127];

需要注意的是,声明多维数组时需要使用“常量整数表达式”,这意味着,我们不可以使用小数分数,也不可以使用非固定量,比如函数来声明多维数组,同时,与大多数人想象不同之处,我们可以使用负数来声明多维数组,比如

input [31:0] data_in [-1:127];

虽然这种方法不会报错,但很显然,笔者并不提倡这种方法,欢迎读者在评论区讨论原因。

同时需要注意的一点是多维数组的赋值,“IEEE Std 1364™-2005”中规定:我们可以为数组的单个元素赋值,但却不可以一次性的部分或完全的赋值数组,因此,以下的想要批量赋值方法,都是错误的

reg arrayb[7:0][0:255];

arrayb[1] = 0;

// Illegal Syntax - Attempt to write to elements

// [1][0]..[1][255]

arrayb[1][12:31] = 0;

// Illegal Syntax - Attempt to write to

// elements [1][12]..[1][31]

正确的赋值方法如下

reg arrayb[7:0][0:255];

arrayb [7][1] = 0;

reg [31:0] data_in [0:127]

data_in[1] = 32'h010x;

- 为什么对于arrayb[1]=0的赋值是错误的,但是对于data_in[1]的赋值是正确的呢?也同样欢迎读者在评论区发表你的看法

三、wire型数组

线网型的数组,对于在generate语句中连接端口有很强烈的现实意义,如下的例子就可以说明问题,这里定义的多维数组“t”,在generate语句的例化过程中,以门电路的形式进行连接。

module addergen1 (co, sum, a, b, ci);

parameter SIZE = 4;

output [SIZE-1:0] sum;

output co;

input [SIZE-1:0] a, b;

input ci;

wire [SIZE :0] c;

wire [SIZE-1:0] t [1:3];

genvar i;

assign c[0] = ci;

// Hierarchical gate instance names are:

// xor gates: bit[0].g1 bit[1].g1 bit[2].g1 bit[3].g1

// bit[0].g2 bit[1].g2 bit[2].g2 bit[3].g2

// and gates: bit[0].g3 bit[1].g3 bit[2].g3 bit[3].g3

// bit[0].g4 bit[1].g4 bit[2].g4 bit[3].g4

// or gates: bit[0].g5 bit[1].g5 bit[2].g5 bit[3].g5

// Generated instances are connected with

// multidimensional nets t[1][3:0] t[2][3:0] t[3][3:0]

// (12 nets total)

generate

for(i=0; i<SIZE; i=i+1)

begin:bit

xor g1 ( t[1][i], a[i], b[i]);

xor g2 ( sum[i], t[1][i], c[i]);

and g3 ( t[2][i], a[i], b[i]);

and g4 ( t[3][i], t[1][i], c[i]);

or g5 ( c[i+1], t[2][i], t[3][i]);

end

endgenerate

assign co = c[SIZE];

endmodule

四、reg型数组

reg型的数组,在电路设计中也存在很强的意义,以RISC-V CPU的寄存器描述为例,其中就会应用到reg型的多维数组,其中的一部分寄存器用来暂存计算数据,另一部分用来配置CPU、描述错误状态或保存地址和指针。

同时,在这里我们进行如下区分,以下的两个数组代表的含义不同,第一个表示n bit的寄存器,但只有一维,而第二个描述1 bit的寄存器,但有n维,这种不同形式的描述会对我们的赋值产生影响,希望读者们好好区分。

reg [n:1] rega; // An n-bit register is not the same

reg mema [1:n]; // as a memory of n 1-bit registers

五、其他类型数组

除了具有综合意义的reg型与wire型数组,“IEEE Std 1364™-2005”还提供了其他类型的数组声明,“integer, time, real, realtime”也都可以用数组的形式进行声明

integer inta[1:64]; // an array of 64 integer values

time chng_hist[1:1000] // an array of 1000 time values

六、往期【Verilog】高级教程文章

- 多维数组:灭霸打个响指的功夫,看懂Verilog多维数组

- clog2系统函数: 关于Verilog自动计算位宽的系统函数$clog2,这些是你不得不知道的

- UDP用户原语:玩转UDP用户原语,这篇文章就够了

- $monitor系统函数:放学前的最后几分钟,看懂Verilog中的monitor系统函数

- generate语句:一把王者的时间,学会Verilog中的generate语句

- parameter常量:玩转parameter与localparameter,这篇文章就够了

- inout双向端口:通俗易懂的带你解读inout双向端口

- task与function区别:芯片人必会的task与function区别详解