AD2428W手册解读之概述

汽车音频总线(A2B®)在节点之间连接多通道I2S同步PCM数据,距离可达15米。它还将I2S的同步、时分多路复用(TDM)特性扩展到一个连接多个节点的系统,其中每个节点可以使用数据、提供数据,或两者兼有。

收发器支持这些A2B功能,通过多通道I2S/TDM接口与通用数字信号处理器(dsp)、现场可编程门阵列(fpga)、专用集成电路(asic)、麦克风、模数转换器(adc)、数字模拟转换器(dac)和编解码器直接接口。它们还提供了一个PDM接口,可直接连接多达4个PDM数字麦克风。启用A2B总线供电(假象供电)功能,通过通信链路使用的相同的雏菊链双绞线向从节点供电电压和电流。该收发器还完全支持通过A2B链路进行I2C通信。

收发器具有以下特点:

1、线路拓扑:

1.1、单主多从。

1.2、节点间非屏蔽单绞线(UTP)线缆连接(线缆长度以产品数据表为准)。

2、远距离通信:

2.1、数据同步:

多通道I2S/TDM到I2S/TDM接口。

同步,所有节点同步时钟。

低延迟从机到从机通信。

2.2、I2C到I2C控制和状态信息。

2.3、远距离GPIO。

3、可使用SigmaStudioTM图形开发工具进行配置。

4、适合汽车应用。

5、可配置为A2B总线主、从接口。

6、I2C接口。

7、8位~ 32位多通道I2S/TDM接口。

7.1、I2S/TDM/PDM可编程数据速率。

7.2、最大32路(1 × TDM32或2 × TDM16),最多可映射32个上下行A2B总线槽位。

8、PDM输入支持多达4个高动态范围的麦克风。

9、每个收发器的唯一ID寄存器•支持交叉或直通布线。

10、可编程设置,以优化EMC性能。

1、A2B术语

为了更好地利用A2B系统,理解以下术语是有帮助的。

A-Side or A-Port:A2B收发器接口,朝向master(紧邻上游节点)。

B-Side or B-Port:A2B收发器接口,面向最后一个直列从属机(即下游的下一个直列从属机)。

Bus Link:A2B总线可以由多个雏菊链式的从节点连接到单个主节点。主节点和从节点0之间的物理连接,以及从节点之间的所有物理A2B连接,称为总线链路。每条母线通常使用一对非屏蔽的双绞线。

Data Channel:数据通道为单个传感器/执行器(如ADC、麦克风、扬声器等)传输I2S/TDM同步数据。I2S/TDM接口使用相同大小的数据通道,其中数据字的宽度通常小于I2S/TDM数据通道的宽度。收发器的I2S/TDM接口支持16或32位可编程数据通道长度。

Data Slot:映射到A2B总线上的单个传感器/执行器(例如ADC、麦克风或扬声器)的同步数据字。

Downstream:通信流从主节点流向从节点,终止于最后一个联机从节点。

Host:为主收发器编程的处理器。主机也是A2B总线上的同步时钟源。时钟信号(BCLK)是主机与主机之间I2S/TDM接口的一部分。

I2S/TDM:I2S (inter IC sound)总线在PCB上的音频芯片之间传输脉冲编码调制(PCM)信息。I2S/TDM接口使用时分复用(TDM)将I2S立体声(2通道)内容扩展到多个通道。

Local Power:不使用A2B总线电源的从节点使用由额外导线提供的本地电源。

LVDS:低电压差信号。

Master Node:时钟的发起者(源自I2S输入)、下游数据、网络控制和电源。主节点由主机处理器和A2B主收发器组成,A2B主收发器接收来自主机的有效载荷并将有效载荷发送给主机。

PDM:脉冲密度调制(PDM)用于sigma变换器。PDM格式表示抽取前的过采样1位σ δ ADC信号,常用于数字麦克风的输出格式。

Phantom Power:从节点可以接入到A2B总线链路上的偏置电压,并将其作为唯一的电源。这样的A2B总线供电的从节点被认为是“虚供电”。

PRBS:伪随机二进序列。

Preamble:表示控制帧或响应帧开始的同步位。对于每个超级帧,主控端都发送下游控制帧的序言。从收发器与下游控制前导同步,并从中产生一个本地的、相位一致的主时钟。

Response Time:指定最后一个节点在超帧启动后等待的时间,该节点在响应同步响应帧(SRF)之前。响应时间在主节点和离主节点最近的所有从节点中编程,以便这些节点知道何时期望从下游切换到上游。

Slave Node:可寻址网络连接点。从节点可以是下游和上游数据槽的源和/或目的地。每个A2B从节点都有一个A2B从收发器。

Synchronization Control and Response Frames (SCF/SRF):节点的控制帧(控制报头)和节点的响应帧(响应报头)。头包括一个用于同步的前文,并允许对所有节点进行读写访问。

Synchronous Data:数据以固定的时间间隔(可在44.1 kHz或48 kHz之间选择)连续传输到同一个节点,并从同一个节点传输数据(例如音频信号)。

Superframe:整体框架结构为A2B。它以SCF开始,包括可选的数据槽,并以SRF结束。超级帧每1024个总线时钟周期重复一次。

Upstream:通信流从最后一列的从节点到主节点。

2、A2B总线细节

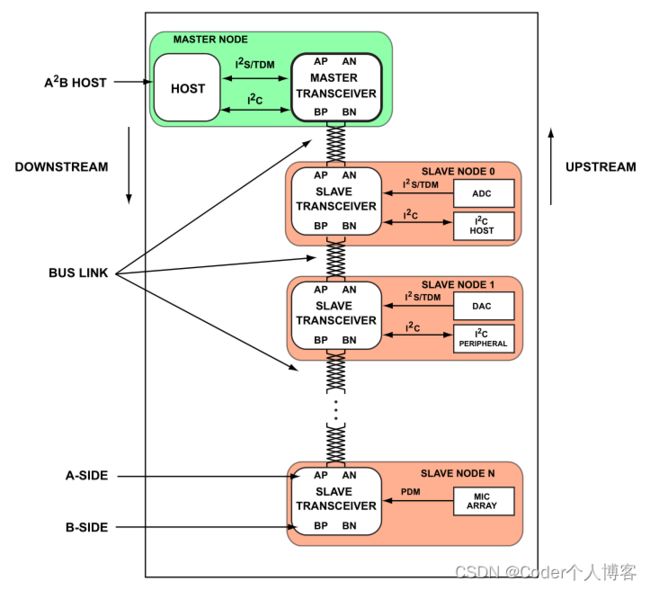

通信系统框图显示的是一个A2B通信系统,它是一个单主多从的系统,主收发器由主机控制。I2S/TDM接口上的主机定时同步的同步信号(SYNC),频率为44.1 kHz ~ 48khz,所有A2B节点同步至该频率。在A2B总线上的通信以这个速率在周期性的超级帧中发生。数据传输采用的是A2B系统比特时钟(SYSBCLK)速率,比超帧速率(48khz时49.152 MHz, 44.1 kHz时45.158 MHz)快1024倍。每个超帧被分为下游传输、上游传输和无传输(总线未被驱动)阶段。

Communication System Block Diagram

A2B超帧图显示的是一个起始阶段为下游传输,后期为上游传输的超帧。

A2B Superframe

A2B总线上的所有信号都是行编码的,主节点以同步序言的形式将同步信号下行转发给最后一个从节点。这个序言后面是控制帧(SCF)。在下游,TDM同步数据直接添加在控制框之后。每个从属节点都可以使用或消费一些下游数据,并为下游节点添加数据。最后一个从节点在响应时间之后以响应帧(SRF)进行响应。上游同步数据由每个节点在响应帧之后直接添加。每个节点还可以使用或消费上游数据。所有同步数据都被组织成等宽的数据槽,尽管上游和下游槽的宽度可以不同。详细信息请参见A2B槽位格式。

嵌入式控制和响应帧允许主机在A2B总线上单独寻址每个从节点。以类似的方式,主机还可以访问远程外围设备,这些设备使用I2C- to-I2C远距离通信连接到任何已发现的从收发器。

A2B系统中的所有节点在同一个A2B超帧中同步采样。主站的同步I2S/TDM下行数据在同一A2B超帧中到达所有从站,各节点的上行音频数据在主站的同一I2S/TDM帧中同步到达。奴隶之间的剩余音频相位差可以通过使用A2B_SYNCOFFSET寄存器的同步引脚信号延迟的寄存器可编程精细调整来补偿。

由于每个采样周期都通过I2S/TDM接口接收和传输数据,因此数据在A2B总线和I2S/TDM接口之间移动会有延迟。A2B总线上样本之间的时序关系如图A2B总线同步数据交换图所示。

A2B总线同步数据交换图

注意在A2B总线同步数据交换图中,上下游样品都以进入A2B系统的超帧命名,如下所示:

1、超级帧M中主节点收发器传输的数据产生下游数据M。

2、超级帧N中从节点收发器传输的数据产生上游数据N。

3、A2B收发芯片通过I2S/TDM接口接收到的数据在以下超帧中通过A2B总线传输。

4、A2B总线上的数据通过以下超帧中的A2B芯片收发器的I2S/TDM接口进行传输。

5、通过A2B总线(主从或从主)传输的数据有两个超级帧的延迟,加上收发芯片中积累的任何内部延迟,以及由于导线长度造成的延迟。因此,从一个A2B收发芯片的I2S/TDM接口到另一个A2B收发芯片的I2S/TDM接口,总时延略高于两个超级帧。

3、功能描述

A2B收发机用于连接多路PCM (inter-IC声音)同步PCM (multi - channel I2S)数据,节点间距离传输(线缆长度以产品数据说明书为准)。它还将I2S的同步、时分多路复用特性扩展到一个连接多个节点的系统,其中每个节点可以使用数据、提供数据,或两者兼有。

A2B收发器支持A2B的这些功能,通过多路I2S/TDM接口与通用的dsp、fpga、asic、麦克风、adc、dac、编解码器等接口相连。通过A2B总线链路的数据是曼彻斯特编码的。该收发器还完全支持通过A2B链路进行I2C通信。A2B收发器既可以用于从节点,也可以用于主节点。默认情况下,收发器启动时为从收发器,但如果主机设置了A2B_CONTROL.MSTR,则可以配置为主收发器。

简化的四节点A2B系统图展示了一个简单的A2B系统示例。主机程序在每个节点注册,以控制A2B总线上的数据流量。从节点0和2的麦克风数据下发到主机,从节点1和2的扬声器数据从主机下发到dac。

简化的四节点A2B系统框图

4、架构概念

以下部分提供了描述硬件块、接口和互连的信息。

4.1、I2C接口

I2C接口用于从本地连接的主机直接访问收发器寄存器空间,并通过A2B总线在主收发器和系统中任何发现的从节点之间远程交换I2C数据。这个协议被称为I2C over distance,其中交换的I2C数据被嵌入在同步控制帧(下游,从主到目标从)和同步响应帧(上游,从目标从到主)中。

模块中的I2C接口支持最多5v逻辑电平,具有以下特点:

1、A2B主节点上的Slave only操作。

2、A2B从节点上的主、多主或从操作。

3、由A2B_I2CCFG.DATARATE配置的100k或400k位/s速率的操作。

4、7位寻址。

5、时钟延展。

注意:主节点上的A2B主机必须支持I2C时钟延展,以便与主收发器接口。

被配置为master的收发器可以识别两个I2C设备地址:

1、BASE_ADDR:用于通过I2C端口直接访问它的寄存器空间。

2、BUS_ADDR:用于通过A2B总线使用I2C over distance协议远程访问从节点寄存器

和从节点I2C外设。

I2C BASE_ADDR由ADR2/IO2和ADR1/IO1引脚在上电复位时的逻辑级别设置,从而支持最多4个主设备连接到同一条I2C总线。7位设备地址的LSB决定I2C数据交换是使用BASE_ADDR(位1 = 0)访问收发器,还是使用BUS_ADDR(位1 = 1)通过master-enabled的收发器访问总线节点,如I2C地址表所示:

I2C设备地址表

被配置为slave的收发器不能识别BUS_ADDR。在从收发器上,I2C接口允许I2C主从行为。当收发器通过A2B总线接收到来自主机的远程I2C外设访问请求时,它就是I2C的主人。从收发器作为I2C主机,然后将I2C交易转发给在其A2B_CHIP寄存器中编程的I2C从地址。当本地外部控制器通过I2C端口访问收发寄存器(BASE_ADDR)时,它是I2C slave。

注意:当本地外部控制器可以对从收发器的寄存器空间进行编程时,A2B_SWCTL、A2B_RESPCYCS、A2B_SLOTFMT、A2B_DATCTL、A2B_RAISE和A2B_GENERR寄存器必须由远端主机通过A2B总线写入。从本地I2C端口写入这些寄存器对寄存器没有影响。

收发器上的I2C接口允许在锁相环锁定前进行寄存器编程。写1表示动作(W1A)位(例如,A2B_CONTROL.ENDDSC和A2B_CONTROL.NEWSTRCT)在锁相锁之前无效,因为协议引擎仍在重置中。

注意:A2B_SWCTL, A2B_SLOTFMT, A2B_DATCTL和a2b_discry寄存器不能在锁锁之前写入主收发器。在锁锁建立之前,对这些寄存器的写操作是无效的。

注意:系统软件的设计必须避免同时从A2B主机(通过A2B总线)和本地处理器(通过I2C端口)写入同一从寄存器。当发生写争用时,两个写操作都完成了,但是它们完成的顺序是不可预测的。

4.1.1、I2C时钟延展:

收发器采用I2C时钟拉伸特性,保证I2C接入有足够的时间处理。主要应用于主机I2C通过A2B总线接入从节点收发器和从节点I2C外设。时钟拉伸由主机在以下时间响应主机I2C访问发起:

1、在写访问期间 - - 在每个数据字节之后的确认位之前。

2、在读访问期间 - - 在读请求后面的确认位之前。

3、在对一个以上字节的突发读/写访问期间 - - 在后续数据字节的第一个比特之前。

将SCL信号拉低向主机表明收发器需要更多的时间来处理请求。一旦收发器准备好应答请求,它就会让SCL信号升高,这样主机就可以重新获得对SCL的控制,并继续应答(ACK)和下一个字节。

注意:在A2B系统设计中,主机(I2C主机)必须支持I2C时钟延展。

当从节点中的外围设备拉长I2C时钟时,SCL信号也在主收发器和主机之间拉长。如果SCL信号在32个超级帧的时间内没有被外围设备释放,则主机注册一个超时(A2B_INTPND2。I2CERR = 1),释放SCL,并停止对主机时钟的拉伸。这个超时确保从外围设备不能使主机的I2C接口永久停止。

4.1.2、访问I2C收发器

7位设备地址的LSB决定I2C数据交换是使用BASE_ADDR(位1 = 0)访问收发器还是使用BUS_ADDR(位1 = 1)通过主配置的收发器访问总线节点,如下表所示。

I2C设备地址

A2B收发器支持以下读写操作:

1、单字写操作——A2B主(I2C从)在第九个时钟脉冲期间拉低SDA发出确认,从而完成

访问。

2、突发模式写入序列——收发器在每个数据字节之后自动增加寄存器地址指针,因此可

以在不重新编程地址的情况下写入顺序数据寄存器。

3、单字读操作—第一个读写位为0,表示写操作。这是因为必须写入寄存器地址来设置

内部地址。在I2C从端确认收到寄存器地址后,I2C主端必须发出一个重复的启动命令,随后

是R/W位设为1(读)的芯片地址字节。这导致I2C数据线SDA反向,并开始将数据驱动回I2C主

机。然后I2C主控器每隔9个脉冲就向从属器发出一个确认脉冲。

4、突发模式读取序列——收发器在每次读取数据字节后自动增加寄存器地址指针,因此

无需对地址重新编程就可以读取连续的数据寄存器。

通过I2C接口传输数据需要以下步骤:

1、数据传输由连接到A2B收发器的微控制器发起。

2、微控制器建立一个启动条件(SDA上从高到低的转换,而SCL保持高),这表明一个地

址/数据流随后。

3、在接下来的8个SCL周期中,A2B收发器从主机(首先是MSB)接收到一个7位地址和

R/W位。

4、A2B收发器识别传输地址,并在第九个时钟脉冲(确认位)期间拉低数据线进行响应。

R/W位决定了数据的方向。当第一个字节的LSB被清除(=0)时,主机向主机写入信息。当第一个字节的LSB被设置(=1)时,主机从主机读取信息。直到遇到停止条件(当SCL处于高位时,SDA从低电平转换到高电平)数据传输才会发生。寄存器地址指针自动递增,以支持对主和从突发模式I2C写和突发模式I2C读。

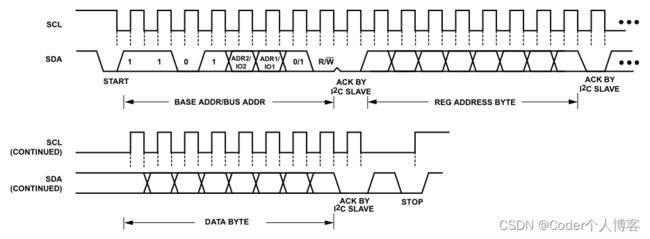

I2C操作格式如下图所示:

1、写入BASE_ADDR/BUS_ADDR可以包含一个或多个字节的数据。设备地址后的第一

个字节设置设备中的寄存器地址。随后的字节被写入到寻址寄存器。由于地址指针在每次写

入后递增,因此可以在单个事务中写入顺序寄存器。

2、从BASE_ADDR/BUS_ADDR读取的数据可以包含一个或多个字节的数据。带有写指

示的设备地址后面跟着该设备中的寄存器地址和带有读访问指示的重复设备地址。

I2C数据格式

重复的设备地址后的第一个字节包含被寻址的寄存器的值。设备地址后的第一个字节设置设备中的寄存器地址。它后面是重复的设备地址,但带有读访问指示。随后的字节包含自动增加的寄存器地址的值。

I2C的写时序图

I2C的读时序图

4.1.3、Transceiver I2C Access Latencies

当I2C通过A2B总线远距离访问远程收发器时,会产生延迟。“I2C总线时延”表中给出了不同类型I2C接入的A2B总线时延。

I2C总线延迟(48khz超帧率)

| I2C Access Type(Conditions) | Estimated A2B Bus Latency (µs) |

|---|---|

| I2C向从属收发器寄存器写入N个数据字节 (时钟延展通过主A2B_I2C.CFGEACK = 0启用。) |

N × 22 |

| I2C从从属收发器寄存器读取N个数据字节 (时钟拉伸通过主A2B_I2CCFG.EACK = 0启用。) |

N × 22 |

| I2C向从收发器寄存器写入N个>1个数据字节 (通过主控A2B_I2CCFG禁用时钟拉伸。EACK = 1,主机I2C使用400khz的数据速率。) |

2 |

| I2C向从属收发器寄存器写入N个数据字节 (时钟拉伸通过主A2B_I2CCFG启用。EACK= 1,主机I2C使用100khz的数据速率) |

0 |

| I2C向远端I2C外设写入N个数据字节 (从A2B_I2CCFG.DATARATE = 0 = 100 kHz) |

((N – 1) × 113) + 213 |

| I2C向远端I2C外设写入N个数据字节 (从A2B_I2CCFG.DATARATE = 1 = 400 kHz) |

((N – 1) × 45) + 70 |

例如,考虑这样一种情况:正在写入一个远程外围设备(连接到从节点)寄存器。“I2C接入时延”界面中I2C接入时延以绿色箭头表示

Note:I2C访问总线延迟表中描述的延迟是针对没有冲突的访问。如果I2C消息没有立即得到

确认,或者由于GPIO中断、线路故障中断、I2C问题(NACK)等高优先级事件而被延迟,则在

尝试执行消息交换之前产生的延迟不包括在表中提供的值中。

4.2、脉冲密度调制接口(PDM)

脉冲密度调制用于sigma变换器。PDM格式表示抽取前的过采样1位σ δ ADC信号,通常用作数字麦克风的输出格式。

PDM模块支持高动态范围的麦克风,具有高信噪比(SNR)和扩展的最大声压级(SPL)。

该收发器的增强PDM模块支持比AD241x收发器更低的噪声底层。提供大于120db的信噪比。收发器上的PDM模块支持24 kHz和12 kHz采样率,此外,使用相同的PDM时钟速率(在48 kHz帧速率下为3.072 MHz),还支持48 kHz采样率。收发器PDM模块中的高通滤波器截止频率固定为1hz,不可编程。高通滤波器是一阶IIR滤波器。

收发器可编程1x, 1/2x或1/4倍PDM采样(48 kHz, 24 kHz或12 kHz典型)相对于超帧速率(48 kHz典型)。对于1/2x或1/4x PDM采样,A2B插槽中的同步数据被复制,以匹配超帧速率。当将收发器的降低速率特性与此结合使用时,甚至更低的PDM采样速率是可能的(例如,降低到375赫兹)。

收发器的PDM位时钟输出频率比PDM音频采样率(通常为3.072 MHz,用于48 kHz的PDM音频采样)快64倍。

每个PDM启用的接收针可以接收多达两个通道的音频数据(立体声)。其中一个通道与时钟上升沿有关,另一个与时钟下降沿有关。

PDM块使用PDM控制(A2B_PDMCTL)寄存器配置:

1、当A2B_PDMCTL.PDM0EN = 1, DRX0/IO5引脚启用接收PDM数据,BCLK引脚是一

个输出,通常为TDM2设置产生3.072 MHz的时钟。该模式下DRX0/IO5引脚数据不传递到I2S

/TDM接口。同样,A2B_PDMCTL>PDM1EN位控制DRX1/IO6引脚上的PDM数据接收。

2、A2B_PDMCTL.PDMxSLOTS位选择DRX引脚上的PDM信号是使用一个(单声道)还是

两个(立体声)通道。

4.2.1、连接麦克风的PDM采样边缘

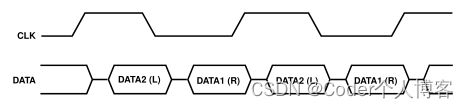

脉冲密度调制(PDM)接口允许来自两个麦克风的PDM输入使用单个时钟在单个数据线上进行时间多路复用。

PDM麦克风对数据进行编码,使左通道在时钟(CLK)信号的下降沿有效,而右通道在CLK信号的上升沿有效。在CLK信号的适当半相驱动DATA信号后,麦克风输出被三态化。因此,两个麦克风(一个设置在左边通道和另一个设置在右边通道)可以共享一个数据线(见立体声PDM格式图)。

立体PDM格式

在收发器中,PDM模块对所有64个时钟边缘上的麦克风数据进行采样。收发器必须被编程为每帧产生64个BCLKs的TDM模式(默认的TDM2/32或TDM4/16模式)。TDM设置不影响PDM块。

在收发器中,在BCLK上升沿采集的数据总是第一信道。如果A2B_PDMCTL.PDM0SLOTS=1或A2B_PDMCTL.PDM1SLOTS = 1,第一个槽位与BCLK上升边相关,第二个槽位与BCLK下降边相关。

例如,从节点的DRX0/IO5和DRX1/IO6引脚分别连接两个麦克风,PDM0和PDM1槽位配置为2槽位。在这种情况下,PDM块对每帧64位的数据进行采样,将其转换为24位的PCM数据,并驱动转换后的输出,如下所示:

1、右侧麦克风数据在上升时钟边缘的DRX0引脚上采样,并驱动到A2B总线上的第一*传输插槽。

2、左侧麦克风数据在下降时钟边缘的DRX0引脚上采样,并驱动到A2B总线的第二*传输槽中。

3、右侧麦克风数据在上升时钟边缘的drx1引脚上采样,并驱动到A2B总线的第三*传输插槽。

4、左侧麦克风数据在下降时钟边缘的DRX1引脚上采样,并驱动到A2B总线的第四*传输槽中。

注意:其中*为实际槽位号,请根据系统槽位配置填写。

当使用默认的A2B_PDMCTL2设置时,PDM引脚总是先用上升边数据进行采样;因此,A2B_I2SCFG.RXBCLKINV和A2B_I2SCFG.PDM模式下配置TXBCLKINV时钟反转设置时忽略TXBCLKINV时钟反转设置。

如果使用默认的A2B_PDMCTL2设置和A2B_PDMCTL.PDM0SLOTS = 0或A2B_PDMCTL。当PDM1SLOTS = 0时,只有正确的通道数据在PDM引脚上采样。如果只希望对左侧通道数据进行采样,可以通过设置A2B_PDMCTL来支持。PDM0EN = A2B_PDMCTL.PDM0SLOTS = A2B_UPFFSET = 1。

4.2.2、PDM增强

默认的PDM功能完全向后兼容以前的收发器代;但是,还有几个附加特性使PDM接口更加灵活。

4.2.3、PDM时钟选项

DRX0和DRX1输入引脚可以单独配置为PDM输入。当在一个或两个DRX引脚的A2B从节点上启用PDM接口时,需要运行64 × fSYNCM(在48 kHz fSYNCM下3.072 MHz)的PDMCLK信号来时钟PDM设备。收发器允许PDMCLK/IO7或BCLK引脚生产所需的PDMCLK。IO7上的PDMCLK可以通过设置A2B_PDMCTL2.PDMALTCLK来启用。

如果使用PDMCLK/IO7而不是BCLK,则TDM2/32或TDM4/16的限制将被删除。BCLK频率可以通过I2S/TDM寄存器设置为不同的频率。在本例中,PDMCLK/IO7用于捕获DRX0/DRX1上的PDM输入。

BCLK和PDMCLK/IO7也可以同时使用,以相同的频率和相位对齐,但极性相反的PDM麦克风时钟。这是通过设置A2B_PDMCTL2来完成的。PDMALTCLK。另外,寄存器控制是先采样上升边数据还是下降边数据:

1、当A2B_PDMCTL2.PDM0FFRST = 0(默认),DRX0上的PDM0数据首先从上升边缘

采样。当A2B_PDMCTL2.PDM0FFRST = 1时,先对下降沿进行采样。

2、当A2B_PDMCTL2.PDM1FFRST = 0(默认),DRX1上的PDM1数据先从上升边缘采

样。当A2B_PDMCTL2.PDM1FFRST = 1时,先对下降沿进行采样。

注意:在主节点中,BCLK始终是一个输入;因此,连接到主收发器的PDM麦克风的时钟输出通常来自PDMCLK/IO7。

4.2.4、PDM数据路由选项:

PDM接口可用于主收发器或从收发器。收发器接收到的PDM数据可以发送到A2B总线上的任何节点,也可以发送到本地的I2S端口,或者同时发送到A2B总线上的任何节点。这是使用A2B_PDMCTL2.PDMDEST字段完成的。

4.2.5、全双工I2S与四个PDM麦克风:

如果同时使用两个引脚(DRX0和DRX1)接收PDM数据,则可以改变DTX1的功能,使其作为备用DRX1,实现最多4个PDM麦克风的并发使用和全双工I2S通信。这是通过设置A2B_I2SGCFG.RXONDTX1完成的。

4.3、I2S/TDM接口

I2S/TDM串口工作在全双工模式下,发送端和接收端使用相同的关键定时位时钟(BCLK)和帧同步(SYNC)信号同时工作。A2B从端收发器根据I2S全局配置寄存器(A2B_I2SGCFG)、I2S速率寄存器(A2B_I2SRATE)和I2S降速寄存器(A2B_I2SRRATE)的设置在BCLK和SYNC输出管脚上产生频率定时信号。A2B主收发器使用相同的BCLK和SYNC引脚作为输入,由主机驱动,从而提供了完整的A2B总线拓扑的时基。

4.3.1、时分多路复用协议

TDM模式将I2S接口扩展到不止一个立体声2通道(TDM2)信号。当在A2B_I2SCFG寄存器中对收发器编程以支持一定数量的TDM通道时,该数量的TDM通道在每个启用的I2S/TDM数据引脚(DTX0和DTX1或DRX0和DRX1)上是可用的。支持TDM2、TDM4、TDM8、TDM12、TDM16、TDM20、TDM24、TDM32模式。

例如,选择TDM4,使能一个传输pin (DTX0),则有4个传输数据通道。如果选择TDM4,同时使能DTX1和DTX0,则共有8个传输数据通道,如图“TDM4设置数据通道结构”所示

TDM4设置的数据通道结构(TDMMODE == 001)

I2S/TDM串口支持16位或32位数据通道宽度,可承载变字长信号。数据字总是以MSB第一格式表示。不同时分复用模式的BCLK信号频率在I2S/时分复用时钟频率设置48khz超帧率表中显示。

I2S/TDM时钟频率设置为48khz超级帧率

DRX0和DRX1输入引脚可以单独配置为PDM输入。当在一个或两个DRX引脚的A2B从节点上启用PDM时,PDM设备需要运行64 × fSYNCM(在48 kHz fSYNCM下3.072 MHz)的PDM时钟。PDMCLK/IO7引脚或BCLK引脚都可以生产所需的PDM时钟。收发器可以在接收PDM流的同时,通过DTX0或DTX1引脚传输TDM数据。而使用BCLK作为PDM时钟时,仅支持I2S/TDM2和32位通道宽度或16位通道宽度的TDM4。使用PDMCLK/IO7而不是BCLK时钟PDM设备I2S/TDM接口允许BCLK用于各种TDM模式。如果同时使用DRX0和DRX1接收PDM数据,则可以改变DTX1的功能,使其充当备用DRX1。这使得最多可以同时使用4个PDM麦克风和全双工I2S通信。

如果PDM只使用一个引脚(DRX0或DRX1),另一个引脚可同时用于I2S/TDM传输。

4.4、Mailboxes

有两个虚拟邮箱MBOX0和MBOX1,它们允许主机和从节点控制处理器之间的处理器间通信。

注意:在本节中,对MBOX0的所有特定引用也应用于MBOX1实例。从节点中的处理器可以通过I2C向A2B从收发器中的寄存器发送消息。在主节点中,主收发器的IRQ/IO0引脚上的中断通知主机处理器新消息,并可以使用BUS_ADDR从I2C上的A2B从收发器寄存器读出消息。如果邮箱消息交换是从A2B主节点到A2B从节点,主机使用BUS_ADDR在I2C上的A2B从收发器寄存器中放置消息。在从属节点中,处理器通过从属收发器的IRQ/IO0引脚的中断得到这条新消息,并可以在检查A2B_LINTTYPE寄存器后,直接通过I2C从A2B从属收发器寄存器读出这条消息。

4.4.1、邮箱编程与操作

A2B_MBOX0CTL寄存器提供位字段来启用邮箱和控制方向、消息长度和中断功能。

默认情况下,邮箱0被配置为接收邮箱(由主机写入,从节点处理器读取),邮箱1被配置为传输邮箱(由从节点处理器写入,主机读取)。操纵A2B_MBOX0CTL。MB0DIR位控制邮箱的方向。

每个邮箱可以容纳8、16、24或32位消息,如在A2B_MBOX0CTL中配置的那样。MB0LEN字段。该字段中的值决定使用四个字节范围的A2B_MBOX0B0到A2B_MBOX0B3寄存器中的哪个寄存器来存储数据,其中第一个字节总是在A2B_MBOX0B0寄存器中,最后一个字节位于容纳编程数据长度所需的最高数据寄存器中,如下表所示。

对于已启用的接收邮箱(A2B_MBOX0CTL。MB0EN = 1和A2B_MBOX0CTL.MB0DIR = 0),如果设置了A2B_MBOX0CTL.MB0FIEN位,则在主机写入邮箱的最后一个字节并被A2B从收发器接收后,从节点发生中断。如果设置了A2B_MBOX0CTL.MB0EIEN位,中断会在主机读取邮箱的最后一个字节后,通过A2B总线向上游传播回主机从节点中的本地处理器。

对于已启用的传输邮箱(A2B_MBOX0CTL.MB0EN = 1和A2B_MBOX0CTL.MB0DIR = 1),如果设置了A2B_MBOX0CTL.MB0FIEN位,那么在从节点中的本地处理器写入邮箱的最后一个字节之后,就会发生对主机的中断。如果设置了A2B_MBOX0CTL.MB0EIEN位,则在主机读取邮箱的最后一个字节后,中断通过A2B总线向下传播到从属节点。

注意:动态重新配置已启用的邮箱(A2B_MBOX0CTL.MB0EN = 1)被禁止。主机必须首先禁用邮箱(A2B_MBOX0CTL.MB0EN = 0),如果需要重新配置,则在两个单独的访问中重新启用它。

当邮箱被填满时,A2B_MBOX0STAT寄存器提供邮箱的状态信息:

1、设置了MB0FULL位和清除A2B_MBOX0STAT.MB0EMPTY位。

2、当一个邮箱被清空,A2B_MBOX0STAT。设置了MB0EMPTY位和清除

A2B_MBOX0STAT.MB0FULL位。

3、当邮箱向主机或本地处理器发出中断信号时设置A2B_MBOX0STAT.MB0EIRQ和

A2B_MBOX0STAT.MB0FIRQ位。当主机或本地处理器处理中断时清除这些位。

多个从节点可以通过它们的TX邮箱与主节点通信。在主节点中,A2B_INTTYPE寄存器包含任何从节点产生的暂挂中断的信息,从节点在A2B_INTSRC寄存器中表示。

当两个从属服务器同时向它们的邮箱写邮件时,主服务器从离它更近的从属服务器那里得到中断指示。在检测到中断后,主机通过读取A2B主收发器的中断类型(A2B_INTTYPE)和中断源寄存器(A2B_INTSRC)来提取中断信息,分别确定哪个中断发生了,哪个从节点产生了中断。在读取A2B_INTTYPE寄存器时,从节点上的A2B_INTSRC寄存器中的中断请求被清除。IRQ/IO0引脚切换到去断言状态,然后由于来自另一个从节点的仍然活跃的中断而立即回到断言状态,并且主机可以再次读取主收发器的A2B_INTTYPE和A2B_INTSRC寄存器来确认另一个从节点的邮箱中断。

4.4.2、邮箱延迟

邮箱事务由I2C总线上的寄存器读写组成。从服务器到主服务器的中断请求是SRF包的一部分,因此从服务器到主邮箱的延迟可能包括一个额外的超帧在等待这个时间。

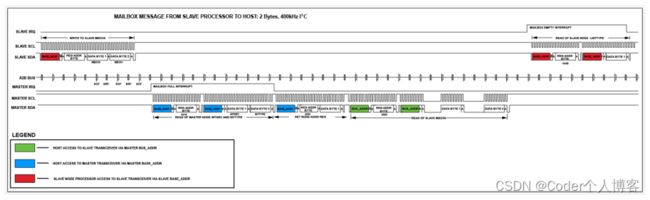

下图显示了邮箱事务在两个方向上的系统计时。浅灰色槽位表示SCF场,深灰色槽位表示SRF场。

如邮箱延迟(从主机到从属)图所示,当邮箱消息从主机发送到从属处理器时,主机处理器使用对主收发器BUS_ADDR设备地址的2字节突发写访问,通过SCF字段将邮箱数据写入A2B从属节点。当写入完成时,从收发器立即向其本地节点处理器生成中断。因此,在IRQ/IO0上断言的slave中断请求(slave IRQ)与SCF字段对齐。一旦这个中断被断言,本地连接的处理器可以使用从收发器BASE_ADDR设备地址来询问A2B_LINTTYPE寄存器,以确定它是邮箱完全中断,然后它可以使用一个2字节的突发读取从邮箱数据寄存器提取数据。一旦这些事务完成,在主节点(master IRQ)上生成邮箱空中断,并与SRF字段对齐,然后主机继续读取主收发器的A2B_INTSRC和A2B_INTTYPE寄存器(使用主收发器BASE_ADDR设备地址),以确定它是由指定的从机发起的邮箱空中断

邮箱延迟(从主机到Slave)

类似地,如邮箱延迟(从Slave到Host)图所示,当邮箱消息从从处理器发送到主机时,从节点处理器随时通过使用从收发器BASE_ADDR设备地址向寄存器发出写操作来填充邮箱数据寄存器,向主A2B节点发出的中断指示通过SRF字段。因此,在IRQ/IO0上断言的主邮箱完全中断请求(master IRQ)与SRF字段对齐。一旦这个中断被断言,主机(使用主收发器BASE_ADDR设备地址)询问A2B_INTSRC和A2B_INTTYPE寄存器,以确定它是由指定的从机发起的邮箱全中断。

邮箱延迟(从Slave到Host)

随后要从从属收发器的邮箱中提取数据,主机必须首先将A2B_NODEADR寄存器设置为产生中断的从属节点(使用主收发器BASE_ADDR写访问),然后发出BUS_ADDR访问来读取从属收发器的邮箱数据字节寄存器(注意发生这些读操作所需的超帧间距)。一旦主机读取了最后一个字节,从属节点(slave IRQ)的邮箱空中断请求将在下一个SCF中断言。然后,从节点处理器可以使用从收发器BASE_ADDR访问来读取A2B_LINTTYPE寄存器,并在确定发生的是邮箱空中断之后采取行动(例如,再次加载邮箱数据寄存器以重新启动进程)。