Daily Paper(2) Minitaur, an Event-Driven FPGA-Based Spiking Network Accelerator

Minitaur, an Event-Driven FPGA-Based Spiking Network Accelerator

Neil D , Liu S C . Minitaur, an Event-Driven FPGA-Based Spiking Network Accelerator[J]. IEEE Transactions on Very Large Scale Integration Systems, 2014, 22(12):2621-2628.

Minitaur,一种基于FPGA的事件驱动型脉冲神经网络加速器

摘要:当前的神经网络正在获得越来越多的荣誉,因为在传统计算机任务上的优秀表现,包括识别、分类、回归以及预测。然而,很少有可扩展的架构出现来解决它们的计算带来的挑战。本文章介绍了Minitaur,一种事件驱动的神经网络加速器,设计它是为了实现低功耗和高性能。作为一个FPGA系统,它可以被集成到一个外部的机器人,或者它可以脱离CPU这类计算昂贵的硬件系统运行。这里提出的版本实现了一个脉冲深度网络,每秒能产生1900万个突触后电流1.5 W功率,每块板支持多达65 K神经元。该系统达到92%的准确率在MNIST手写数据集上,并且拥有71%的准确率在20种分类的数据集上。由于它的事件驱动型,它允许在准确率和延迟之间进行折衷处理。

1.绪论

最近先进的神经网络和机器学习已经证明了它们在现实任务中的显著有用性。然而,神经网络计算下滑了,因为现代的计算机架构不是非常理想的适合网络计算。在标准的前向神经网络中,基础的运算可以看成一个在权重层与激活层之间矩阵的乘法。这个运算可以有效的被实现在GPUs上,但是矩阵乘法的扩展性很差(计算要求大于O(n2)),最终需要非常多的计算。理想的替代方法是,它的功耗明显较低(对于机器人和移动计算),并且可以支持比完整矩阵乘法所允许的更大的网络规模。

最小化浪费的计算是显著减少计算负载的必要条件,而事件驱动的计算是实现这一目标的一种方法。计算视觉通常在一个完整的帧中呈现一个静态图像,但如果视觉信息以无帧的方式处理,可以实现显著的加速,能够进行极其快速的计算。如果每一帧都要处理,那么大量的计算就会在计算静态背景或无趣的特性时重复(和浪费)。这种计算方式对于神经形态事件驱动的传感器非常有效,如文献[1]和文献[3]-文献[5]所示。这些事件驱动设备发出峰值,显示需要处理的事件,从而提高计算效率。

关键的是,基于事件的系统中的系统性能与网络活动而不是网络大小成比例。这允许使用更大的参数空间来获得更准确的结果,同时可以加速运行时执行,并需要更少的计算(因此需要更低的功耗)。此外,减少的计算负载允许处理在实时领域,使一个理想的平台,为现实世界的应用和平台实时交互。

目前的计算体系结构并不十分适合神经网络等网络体系结构,神经元固有的大量并行性,即每个神经元同时执行类似的计算,这意味着一个比GPUs目前提供的更并行的架构。GPUs可以利用网络的并行性,但它们不适合事件驱动的计算。当前的GPUs编程范式使用的是一种内核启动方法,在这种方法中,大量的计算以一批数据的形式载到GPUs上,而不是连续运行。此外,gpu的功耗排除了大多数嵌入式机器人应用程序。由于上述原因,这些平台都不适合网络架构,例如spiking deep belief networks (DBNs),特别是事件驱动的dDBNs,将取得的巨大进步与DBNs[6]具有基于事件的处理[7]的性能。

FPGA架构,然而,可以很好解决这些问题。FPGA是低损耗器件,可现场进行编程,并且可以重配置即如果需要的话,允许更新和源设计。它们固有的支持并行处理和包含足够的本地内存去存储一些权重在提出的典型的深度网络。FPGAs比CPU和GPU有更小的能量损耗。并且是一个成功的设计在未来实现低功耗、特殊应用的高性能集成电路。此外,此外,设计代码可以通过电子方式共享,允许研究人员进行合作并升级他们的物理硬件,而无需额外的成本或物理调整。

这篇文章介绍了Minitaur,一种基于FPGA的时间驱动型的脉冲神经网络加速器。该加速器被使用去研究一款FPGA平台去实现一个实时,时间驱动的深度脉冲网络。第二部分介绍了相关工作在FPGAs和基于脉冲的神经网络加速器,跟着是基于事件处理的理论在第三部分。第四部分讨论了特别的设计在Minitaur。在第五部分,Minitaur的性能特征以及在mist和新闻组分类任务上的真实世界的性能将被评估。第六部分回顾了未来的挑战,提出了有待进一步调查的问题。

2.背景

在加速人工神经网络的软件算法方面已经投入了大量的工作,事件驱动方法已经成为加速这些网络仿真时间的一种方法。在[8]中描述了一个高效的事件驱动软件实现,并在[9]中研究了扩展这些网络的时间复杂性。事件驱动的优化也被考虑用于高级神经元模型的实现,特别是包括[10]中的Hodgkin-Huxley模型。在[11]中可以找到对事件驱动和时间步长软件算法和尖峰神经网络实现性能的全面回顾。

在[12]和[13]中讨论了加速这些脉冲网络的硬件系统,包括基于FPGA的设计。这些FPGA系统主要是像[14]-[16]那样的时间步进硬件加速器,实现了高速,但性能与网络大小成正比。事件驱动的、稀疏计算的硬件实现(如[17]-[19])很少,通常侧重于使用生物学描述的神经元模型,如Izhikevich模型[20]和生物网络拓扑。

近年来,机器学习方法已经验证了替代网络拓扑结构,例如DBNs中使用的网络拓扑结构多层概率生成模型[6]。各个层由称为受限玻尔兹曼机(RBMs)的无向图形模型组成,底层是可见的 sigmoidal单元,顶层是隐藏的sigmoidal单元,通过对称权重双向连接。当RBM堆叠形成DBN时,较低RBM的隐层成为下一较高RBM的可见层。DBN在许多领域都被证明是有效的,在机器视觉[21]和机器听觉[22],[23]等领域取得了显著的成功。在[7]中,脉冲DBN是由尖峰泄漏的积分-点火(LIF)神经元取代这些sigmoidal单元构建的。

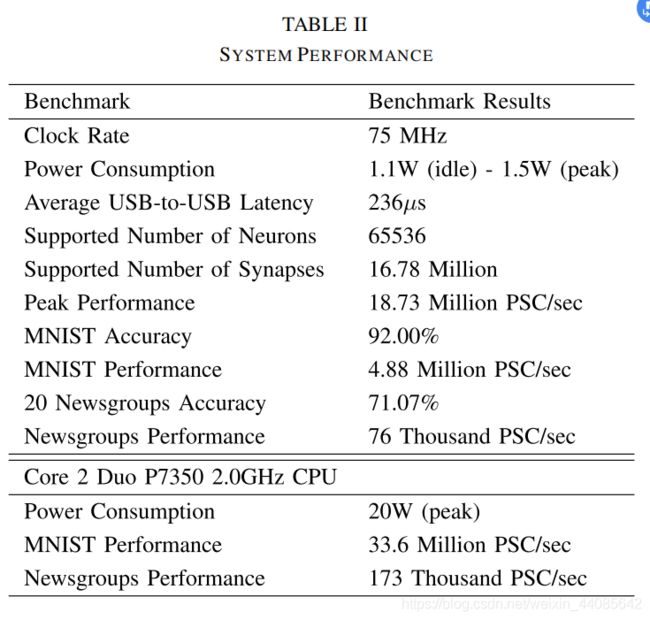

Minitaur扩展了之前在事件驱动系统上的工作,FPGA实现和DBN来加速脉冲神经网络实现。它是一种低功耗、紧凑、事件驱动的系统,其重点是将深度网络作为一个应用领域。该系统支持在多达65536个神经元和数百万个突触的运行时加载任意脉冲神经网络(表II)。其重点在于优化记忆提取和简化神经元模型,以及低功耗,避开了[15]和[18]中使用的大功率、高性能记忆元件。它的性能在两个常用的机器学习任务上得到了验证,使用一个由脉冲神经元组成的DBN,如第五节所述。

3.算法和理论

A.事件驱动神经模型

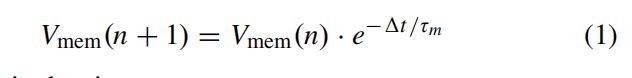

这里使用的神经模型是一个常见的spike模型,包含三个子模型:1)一个由LIF模型描述的躯体;2)输入电流的瞬时突触;3)固定延迟的轴突用于产生脉冲。LIF模型在数学上和直观上都很简单;该细胞膜被模拟成一个带有泄漏[25]的电容器。这个简单的电路形成了一个具有衰减时间常数τm的指数衰减RC系统。在时间步进模型中,第n +1步细胞膜电压Vmem可计算为:

delta t是时间步。

突触模型具有瞬时动力学特性,当i神经元收到来自输入神经元j的脉冲时,其膜电位增加Wi,j阶跃增加。该模型实现了三种不连续来更准确地模拟生物系统:1)阈值(Vthr),当Vmem > Vthr时,神经元产生一个峰值;2)脉冲后膜的复位电位(Vreset);3)一段不应期(tref),在此期间,神经元在峰值后不能再产生新的峰值。

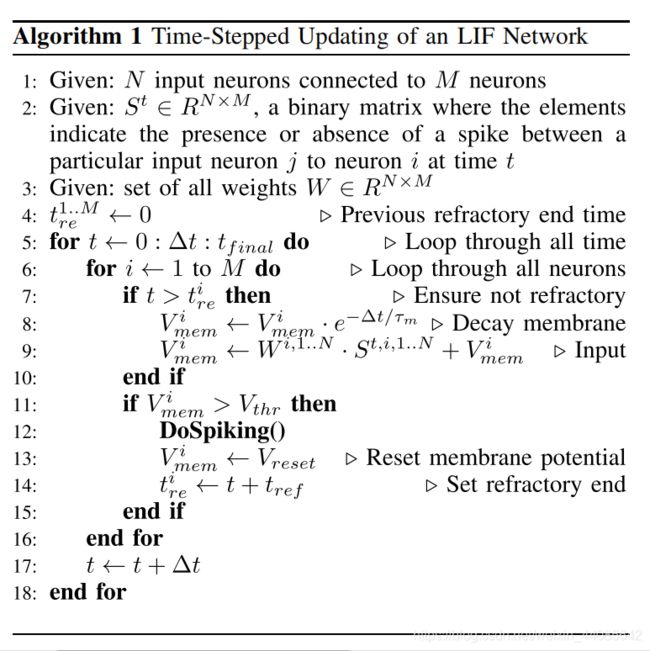

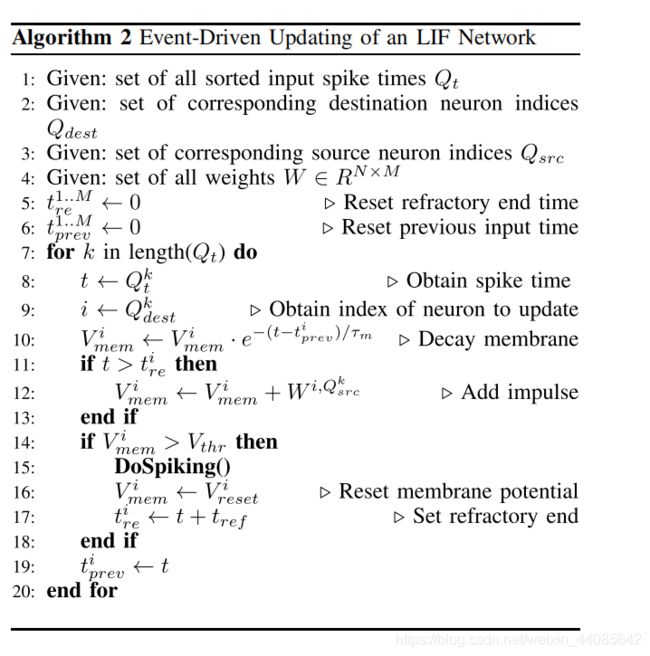

完整的时间步数模型可以被找到在算法1:

该算法可以很容易地转换为事件驱动的等效算法。由于输入电流是瞬时的,而膜电位是指数衰减的,所以当有输入尖峰时,只需要在更新膜电位后检查是否发放脉冲。存储前一次更新的时间;当下一个脉冲到达时,神经元膜根据时间差衰减,然后与瞬时输入电流相加。这就产生了Miniaur系统中使用的神经元模型。神经元只在输入峰值时进行更新,因此计算速度现在与网络活动成正比,而不是神经元的数量。完全事件驱动的执行由算法2描述:

B.仿真

在MATLAB中建立了硬件模型,以确保设计的可行性,并快速模拟参数调整的效果。这个实现主要用于创建缓存策略原型,因为内存带宽从根本上限制了硬件的性能,而不是计算时间。关于这些策略的更多细节,见第四- B节。

4.Minitaur 架构

A.Spartan-6 FPGA Architecture

Minitaur是使用低成本的Xilinx Spartan-6平台设计的。完整的实现在ZTEX上完成

usb1.15单板,包含128mb的DDR2 RAM、用于存储的microSD卡插槽、用于引导加载程序的128kb闪存和用于USB接口的FX2芯片。商业上可获得的完整板(http://www.ztex.de)是低成本和理想的现成接口和计算。 Xilinx Spartan-6 LX150包含150k逻辑单元是Spartan-6家族中最大的。

除了大量的逻辑单元,Spartan-6还包含180个DSP单元,用于低功耗并行数学处理。这些dsp支持用于定点乘法和加法的两个18位操作数。重要的是,spartan6在268个单独寻址的低延迟块ram (BRAMs)中总共有549 kB的内存。这些bram需要一个周期进行读取,也可以选择一个周期来注册读取的输出,这使得它们非常适合于特定于核心的缓存。

Xilinx支持的最大时钟速度Spartan-6是400MHz,但与所有FPGA设备一样,这个数字严重依赖于时钟负载和路由。

B.Minitaur Design Principles

基于事件的神经网络系统的性能限制步骤发生在脉冲生成过程中。当神经元激增时,它会执行两种非常强烈的记忆操作:1)确定spike的接收神经元(通常在102 到104个目的地之间)和2)确定每个连接的权重。快速完成这两项任务对于优化系统性能至关重要。

为了尽量减少连接查找的影响,存储了基于规则的连接。虽然真正的生物网络通常是循环的并且很难简化,人工神经网络倾向于遵循特定的连接模式。DBNs、自动编码器、单层RBMs和多层感知器都有一个非常模式化的结构。也就是说,有一层神经元接收来自前一层的投射,并投射到下一层的连接,通常以一种全连接的方式。通过以范围规则格式声明连接,可以非常有效地存储连接规则,例如,第一层的所有神经元项目到第二层的所有神经元,只需要存储SRC开始地址、SRC结束地址、DEST开始地址和DEST结束地址就可以映射整个层的连接。管理大量的突触后输出电流对于神经网络加速系统来说,PSC也是一个挑战,因为神经元通常有大量的输出连接。将峰值存储在峰值队列中,与存储接收峰值的神经元地址不同,存储即将产生峰值的神经元地址的效率要高得多。这样,spike队列存储的是SRC地址,而不是DEST地址,并且在评估轴突延迟后的突触后更新时,只执行规则查找以获取DEST地址。

最后,缓存位置是优化神经元权重和状态查找的关键。在与现实世界交互的事件驱动系统中,系统还可能利用输入数据中的重要模式。例如,在分布式事件驱动视网膜系统[3]中,由于空间扩展对象的移动,一个像素在看到on事件(对比度变化)后,很可能很快就会看到off事件(对比度变化)。这些固有的相关性在时间步进系统中提供了一个主要的优势,并且没有浪费计算,因为每个输入尖峰都代表着世界的变化,这需要输出的更新。对于空间相似的输入事件,可以更快地缓存和获取权值和状态值。通过在计算核上剥离神经元来确保局部性。神经元ID的最后五个比特位将每个神经元分配给一个核,允许一个核存储频繁和最近活跃的神经元的状态和权重,而不会产生竞争。

C. Minitaur Implementation

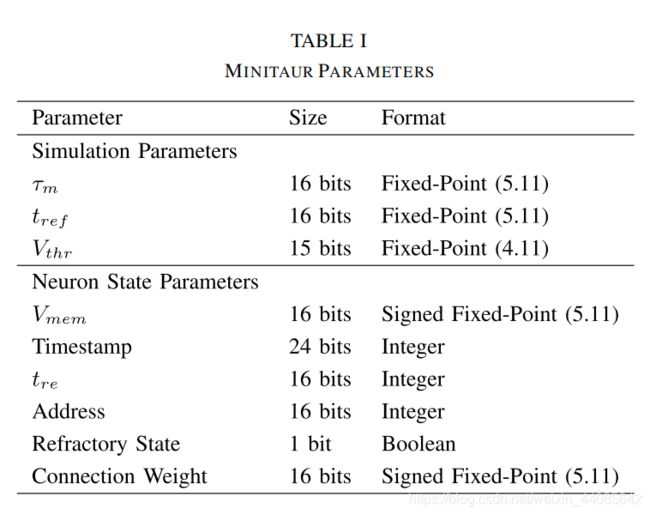

简化的架构图如图1所示,参数列表及其格式见表1。该系统旨在利用现代人工神经网络的共性,从而大大减少计算负荷。尽管Minitaur是一个基于时钟的数字系统,但除了输入事件之外,不会发生任何处理。这种混合方法利用了数字工具的易用性,以及事件驱动处理的大量计算减少。

在这个实现中,尖峰(事件)以包的形式通过USB到达,带有四个字节的时间戳、一个单字节层指示符和一个两个字节的神经元地址。在通过一个环形缓冲区以允许快速爆发峰值之后,峰值被分派到事件队列中,并按照时间戳和层对它们进行排序。时间排序仅在轴突延迟和外部源(例如,基于轴突的神经形态设备)的尖峰与Minitaur计算层混合时是必要的。

为了支持周期性的连接和轴突延迟,神经元峰值和峰值传递到接收神经元之间必须存在一个时间延迟。事件队列作为优先队列维护传入峰值的排序列表,它允许O(log(n))个插入和根节点提取操作。事件队列使用一个由四字节时间戳和一个单字节层索引组成的五字节索引键来存储神经元地址。通过这种方式,同一层的所有峰值将同时被分类,并同时与另一层的峰值分离。7个2048字节的BRAMs被用来同时存储2048个事件。标志可以确保在当时对该层的所有输入进行评估之前,不会从该层发出峰值。

同时,图1中连接所有核心的并行分配器块,检查事件队列以提取第一个可用的spike进行处理。spike是根据spike的起源而不是目的地来存储的,因此需要连接查找来确定哪些神经元将有膜电位更新。

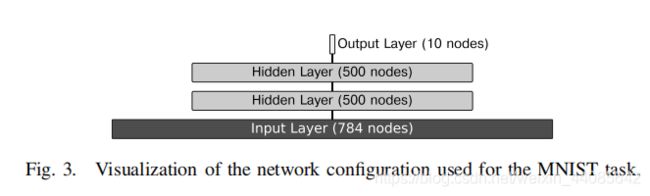

每个神经元被分配一个ID号,并且给定层的神经元被分配连续的ID号。通过这种方式,可以非常紧凑地表示连接:每个SRC和DEST地址的开始和结束都有4个字节,这产生了一个16字节范围的规则。为了支持多层扇出,所有可能的规则都被匹配。请注意,非常复杂的、非基于层的网络仍然可以使用点到点连接以这种形式表示。在描述Minitaur的一个典型DBN时,比较的次数通常很少;例如,五条规则足以描述图3所示的MNIST手写体数字识别网络(每层一条规则,将输出映射到计算机一条规则)。在查找连接时,源地址会迭代地与所有连接进行比较,并且如果找到包含输入脉冲地址的源范围的规则,则将输出范围作为要计算的范围传递。

输出范围地址的底部5位用于将特定的神经元更新分配给特定的核心:例如,一个地址ID为1025的神经元总是被分配给核心1。这允许缓存位置,并避免任何问题导致陈旧的缓存从其他核心更新一个给定的神经元,并行分配器分配一批32个神经元需要更新;等待,直到完成;然后递增,为下一批分配32。这个过程会一直持续,直到神经元的整个目标范围都被解决。

事件驱动的算法(算法2)由核心执行,一旦一个神经元被分配,状态获取和权重获取是同时进行的,以减少延迟,一旦状态被获取,它就被传递给DSP进行计算。状态存储为一个8字节的块:两个字节为难处理结束时间,三个字节为最后更新时间戳,两个字节为状态,以及一个字节为包括缓存标记、初始化位和难处理位在内的分类信息。由于DSP不支持取幂运算,因此会生成一个带有指数衰减因子的ROM查找表。获取时间增量并除以膜时间常数将在该内存中生成整数查找索引,地址j(1024个地址)的值为e−j/128,近似为16位定点精度(5位整数和11位小数)。这产生了一个精确的衰减范围,从1/128τ到8τ,步长为1/128τ。权值以相同的定点格式存储为两个字节。在神经元更新过程中,膜衰减,然后根据输入神经元的权重产生脉冲,并将电位与阈值进行比较。如果超过阈值,则内核将引发一个标志。仲裁后,根据系统参数,该spike要么被组装并发送到计算机,要么被添加到具有轴突延迟的spike队列中,并根据其时间和层次对其进行排序。快速的本地存储是通过最小化权值查找的影响来优化神经网络计算的关键。该缓存使用直接映射缓存算法的变体实现:每个神经元或权重查找只有一个可以映射到的位置,在每个位置,一个参考计数器跟踪连续错过的次数。DDR2交换的代价不像硬盘那么严重,所以对于快速查找来说,对特定内存位置的偶尔争用是一种可以接受的折衷。

对于神经元状态缓存查找,8位缓存地址是使用神经元地址的中间部分形成的。由于计算分区的原因,较低的5位对一个给定核上的所有神经元都是通用的;上面的三位被用作标签。核心指定的5位、缓存地址的8位和标签的3位加在一起就可以恢复整个16位神经元的地址。在缓存命中的情况下(例如,一个值成功地从缓存中检索到),一个引用位被设置为1;并且必须从主存中取出),该位将被清除,如果已经被清除,则该表项将被换出。神经元的状态存储在8个字节,包括标签,允许每核256个条目使用一个2kb的BRAM。

对于神经元权重的查找,采用了两阶段的方法。针对fanout优化后,本地权重缓存被分成16个条目的块。每个16块有一个单一的SRC神经元地址和多达15个DEST神经元地址。在高速缓存查找时,SRC地址的低7位被用来索引高速缓存;如果SRC匹配,则DEST地址的四个较低的位被用来计算从初始SRC地址的跳跃偏移量。如果DEST地址匹配,则从缓存中检索权重。这里,SRC地址的引用位是两位,因为最多15个DEST项可以被一次交换出去;因此,交换一个地址需要连续4次未命中。DEST地址只使用一个参考位,需要两个错过来交换。

5.结果

Minitaur的设计使用了22k的逻辑片,是Spartan-6 LX150 FPGA容量的23%。该FPGA的功耗为1.5 W,其中400mw支持FPGA外置电子器件。在片上的功率预算中,10.0%支持逻辑和信号,16.2%支持200(268)块内存大量使用作为缓存加速系统,73.8%是由于锁相环、时钟分发器、IOs和泄漏。该系统主要使用三个时钟:DDR2时钟为132 MHz, USB I/O时钟为48 MHz,逻辑时钟为75 MHz。Minitaur是一个早期的设备,可以做很多进一步的优化来显著提高它的性能。结果的摘要见表二。在[12]之后,每秒的连接数,或者更具体地说,PSCs/秒被选为主要的性能指标。

性能统计数据是在英特尔酷睿2上收集的Duo P7350时钟为2.00 ghz,运行Ubuntu Linux 12.04。Minitaur使用Java libusb设备包装器通过USB连接,并接收来自计算机上的基准测试软件的输入峰值,用于性能基准测试和新闻组分类任务。此外,计算CPU PSC/秒性能统计使用高性能并行MATLAB实现的LIF神经元网络,而不是块的模型Minitaur,确保公平的峰值性能比较。

A.数据集

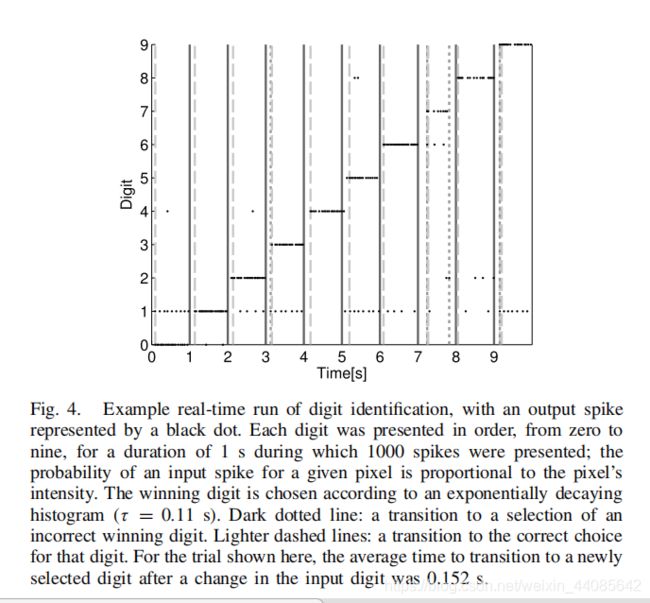

1) MNIST Handwritten Digits:该系统通过对手写数字[26]的MNIST基准进行了广泛的测试。不是另有规定,性能结果使用的全部测试集10000手写数字在通过完整的60000训练集训练后,将静态图像转化为事件,28×28图像矢量化到784个神经元地址和峰值的概率与像素的强度成正比。最终的前馈网络大小为784-500-500-10个单元(图3):

由于每一层都以标准的全对全的方式连接,在这个任务中产生了647000个突触,1785个神经元。使用以前训练过的重量来实现,在[7]软件中使用LIF神经元进行MNIST任务,如图2所示,Minitaur获得了92%的准确率,每幅图像有1000个峰值,本文稍后将讨论每幅图像不同输入体积的影响(图5)。准确性的损失可能是由于表示权重的比特数更少,因为计算机执行任务时需要加倍(8个字节),而Minitaur只使用两个字节来表示一个神经元的权重。为了改进这一点,未来的版本可以使用一个降低精度的训练范式来训练权重,使用不那么精确的表示来更准确地平衡彼此,而不是简单地截断更精确的表示。

Miniaur系统在MNIST分类任务上的实时执行示例的输出行为如图4所示。

B.系统性能

当前设计的基准usb到usb延迟为236μs(平均超过10000次试验),主要由操作系统发布的延迟决定USB读写。Minitaur以处理为基准585 kevts/s或每1.71μs有一个输入尖峰,所有内存都从本地缓存提取。每个输入峰值导致32 PSC(完全使用并行内核),Minitaur在峰值速度下处理了1873万PSC/秒。

C. 初始响应和额外的准确性

当达到足够的精度时,Minitaur可以被用来中止计算。在固定输入上操作时,基于事件的计算是一个细化过程,而不是静态计算。顺序输入事件向系统添加信息,系统随着时间的推移积累证据,以获得更准确的答案。这意味着使用Minitaur的嵌入式机器人平台可以在非常低的响应时间后使用Minitaur的初始输出来实现低质量的猜测,或者支付较小的时间成本来允许后续处理来提高猜测的准确性。在MNIST任务中,59.2%的第一次输出峰值(未显示)在图5的上半部分所示的延迟之后显示了正确答案。这将允许系统在很短的延迟后做出低准确性的猜测。图5的底部显示了随着输入事件数量的增加,系统的精度增加。早期中止和较长的细化用例在机器人领域都有明显的应用,在运行时自由选择是Minitaur系统的一个主要优势。

D.噪声鲁棒性和稳定性

由于一般传感器的不可靠性,以及现实世界数据集中意外事件的可能性,对噪声的鲁棒性是设计实时事件驱动系统的重要部分。为了测试系统对噪声的鲁棒性,采用不同噪声水平的MNIST数据集。

如前所述,从图像中提取峰值的概率与像素强度成比例。然后,随后被替换为峰值的尖刺的比例随机像素,像素空间的统一,和系统计算的准确性(图6)。如图7所示,该系统是非常健壮,只保留采取行动消除干扰输入的重要特性通过层事件传播。有趣的是,输出峰值的数量随着噪音的增加而急剧下降;当接收到90%的噪声时,系统将为1000个输入峰值平均超过两个输出峰值。峰值的减少也具有实用的优点;下游系统使用Minitaur的输出将会有更少的峰值信号,因为Minitaur对结果不太有信心。

6.总结

在本文中,作者介绍了Minitaur spike network accelerator。除了系统每秒1873万PSCs的性能,它只消耗了1.5 W的功率,可用于嵌入式机器人应用。该系统记录了MNIST手写数字分类92%的正确率和71%的正确率20新闻组分类数据集。通过适当的权重,系统对噪声具有非常强的鲁棒性。此外,关于输出峰值的知识可以用来确定任务的难度,并衡量输出的可信度。

目前使用这一系统的一个重大挑战是缺乏有效的训练方法。对于基于spike的LIF网络,特别是dbn,各种学习权值的方法正在探索中特别是当这样的网络阻止了传统的实值sigmoidal激活函数的训练方案和backpropagation。我们需要进一步研究基于事件的学习,以显著提高训练和运行时的准确性。

该系统为进一步研究现实世界中的基于事件的处理提出了问题。对于资源有限的系统来说,获取信息、处理信息以及随后对其采取行动都可以从基于事件的处理中获益。渐进细化可以允许系统收集执行操作所需的尽可能多的信息,确定其分析的可信度,并根据该可信度级别采取行动。在真实世界的闭环系统交互中,这可以极大地优化资源使用,Minitaur对噪声的鲁棒性增强了其在实时系统中使用的信心。