【混沌加解密调制解调】基于FPGA的混沌自同步混沌数字保密通信系统

1.软件版本

quartusii12.1

2.本算法理论知识

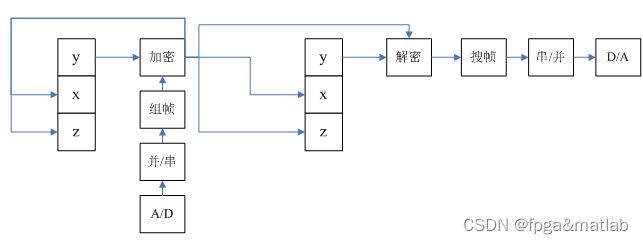

本系统的基本结构,我们遵循你所提供的结构进行,整个框图如下所示:

各个部分的功能如下:

- 加密算法模块采用异或运算,它将来自信源编码的二进制数字序列与密码序列进行异或运算产生密文序列。加密完成后,再通知驱动系统迭代一次,这样就可以保证数据的完整性。

- 驱动系统序列密码发生模块的主要功能是产生用于加密的密码序列。它是数字加密系统中加密可靠性的核心部分,包括机密序列的产生(在发送端对明文进行加密。)因为是自同步系统,所以加密后的混沌序列还要作为驱动系统的迭代值。

- 解密算法模块也采用异或运算,在接收端,将密文序列与密码序列进行异或运算还原成二进制明文序列。

- 密码同步检测模块主要是产生密码同步信号来驱动响应系统密码发生器模块,用于对接收方的密码产生器的状态进行更新。其工作原理是判断经信道传输的密文是否发生变化,如果变化了就产生一个驱动信号,一方面是驱动响应系统进行下一次迭代,另一方面是驱动解密算法模块进行解密。

- 响应系统序列发生器模块的主要功能是产生用于加密的密码序列,当他接收到密码同步检测模块生成的密码同步驱动信号后,响应系统就迭代一次。

3.核心代码

//`timescale 1 ns/ 100 ps

module Encryption_complete_system(

i_clk,

i_rst,

i_enable,//the enable of signal

i_voice, //the signal

o_enable,//the enable of p2s

o_serial_dout,//the serial data of signal

o_serial_frame,

o_T_signal//the data of Encryption

);

input i_clk;

input i_rst;

input i_enable;

input[15:0] i_voice;

output o_enable;

output o_serial_dout;

output o_serial_frame;

output signed[31:0]o_T_signal;

//change the parallel data to serial data

p2s p2s_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_enable (i_enable),

.i_voice (i_voice),

.o_enable (o_enable),

.o_serial_dout(o_serial_dout)

);

add_frame add_frame_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_serial_dout),

.i_enable (o_enable),

.o_dout (o_serial_frame),

.o_enable ()

);

wire signed[31:0]xn;

wire signed[31:0]yn;

wire signed[31:0]zn;

Lorenz Lorenz_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_yn (o_T_signal),

.o_xn (xn),

.o_yn (yn),

.o_zn (zn)

);

Encryption Encryption_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_serial_frame),

.i_yn (yn),

.o_signal (o_T_signal)

);

endmodule //`timescale 1 ns/ 100 ps

module Decryption_complete_system(

i_clk,

i_rst,

i_rec_signal,

o_dout,

o_dout_sign,

o_peak,

o_peak_enable,

o_peak_dout,

o_enable2,

o_voice_dout

);

input i_clk;

input i_rst;

input signed[31:0] i_rec_signal;

output signed[31:0]o_dout;

output o_dout_sign;

output[6:0] o_peak;

output o_peak_dout;

output o_peak_enable;

output o_enable2;

output[15:0] o_voice_dout;

wire signed[31:0]xn;

wire signed[31:0]yn;

wire signed[31:0]zn;

Lorenz2 Lorenz2_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_yn (i_rec_signal),

.o_xn (xn),

.o_yn (yn),

.o_zn (zn)

);

Decryption Decryption_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (i_rec_signal),

.i_yn (yn),

.o_signal(o_dout)

);

reg o_dout_sign;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_dout_sign <= 1'b0;

end

else begin

if(o_dout < 32'h0000_00ff)

o_dout_sign <= 1'b0;

else

o_dout_sign <= 1'b1;

end

end

find_frame find_frame_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_dout_sign),

.o_peak (o_peak),

.o_dout (o_peak_dout),

.o_enable(o_peak_enable)

);

s2p s2p_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_enable (o_peak_enable),

.i_serial_din (o_peak_dout),

.o_enable (o_enable2),

.o_voice_dout (o_voice_dout)

);

endmodule clc;

clear;

close all;

N = 50000;

x = zeros(N,1);

y = zeros(N,1);

z = zeros(N,1);

x(1) = 0.001;

y(1) = 0.002;

z(1) = 0.02;

S1 = double(rand(N,1)>=0.5);

%简化后的发送

for n = 1:N-1

n

%反馈

if n == 1

S1_T(n)= S1(n) + y(n);

y(n+1) = 0.028*x(n) - 0.001*x(n)*z(n) + 0.999*y(n);

x(n+1) = 0.99*x(n) + 0.01*y(n);

z(n+1) = 0.001*x(n)*y(n) + 0.9973333*z(n);

else

S1_T(n)= S1(n) + y(n);

y(n+1) = 0.028*x(n) - 0.001*x(n)*z(n) + 0.999*S1_T(n);

x(n+1) = 0.99*x(n) + 0.01*S1_T(n);

z(n+1) = 0.001*x(n)*S1_T(n) + 0.9973333*z(n);

end

end

%简化后的接收

for n = 1:N-1

n

%反馈

S1_R(n)= S1_T(n) - y(n);

y(n+1) = 0.028*x(n) - 0.001*x(n)*z(n) + 0.999*S1_T(n);

x(n+1) = 0.99*x(n) + 0.01*S1_T(n);

z(n+1) = 0.001*x(n)*S1_T(n) + 0.9973333*z(n);

end

figure;

subplot(311);

plot(S1);

title('原信号');

axis([1,N,-1,2]);

subplot(312);

plot(S1_T);

title('加密后的信号');

subplot(313);

plot(S1_R);

title('解密后的信号');

axis([1,N,-2,2]);

4.操作步骤与仿真结论

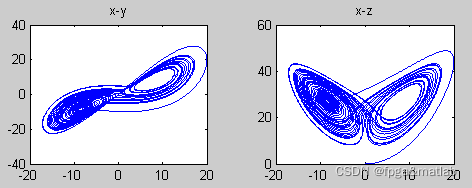

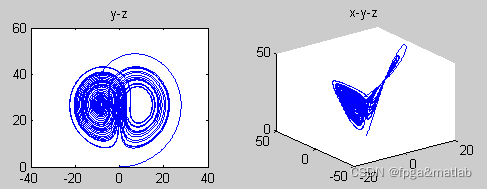

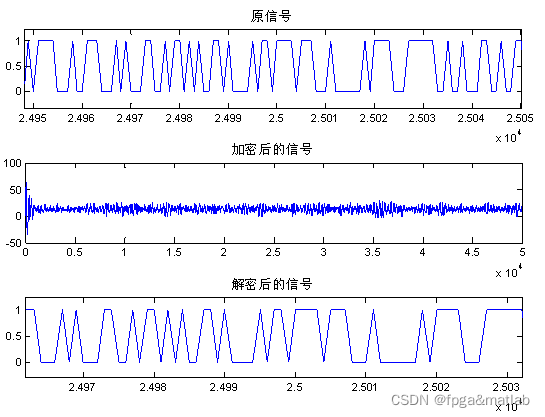

首先实现使用MATLAB进行算法的仿真,我们得到的仿真结果如下所示:

运行MATLAB程序:![]()

这个是混沌模型的基本仿真,说明公式以及初始值选取的正确性。

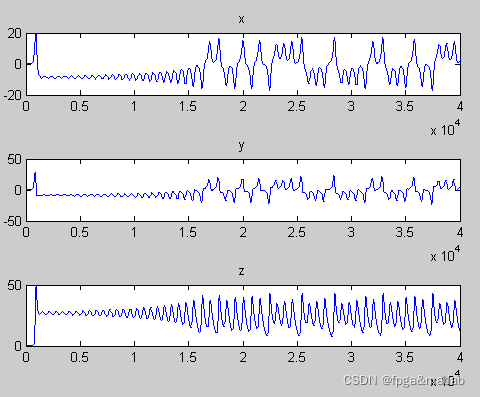

运行MATLAB程序:![]()

这个程序是混沌加密调制解调系统的MATLAB浮点仿真结果图,说明上面的结果是正确的。

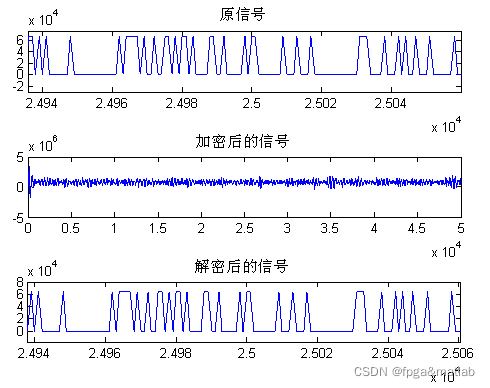

运行MATLAB程序:![]()

从上面的仿真结果可知,以定点进行仿真,只要量化宽度满足一定要求之后,其完全不影响系统的精度。

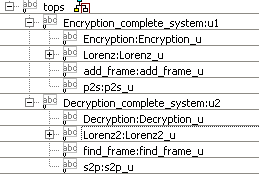

根据上面的介绍,我们可以编写了如下的程序:

自上而下,依次为:

系统顶层文件

——加密调制模块

————加密子模块,lorenz混沌序列产生模块,组帧模块,并串模块。

——解密解调模块

————解密子模块,Lorenz混沌序列产生模块,搜帧模块,串并模块。

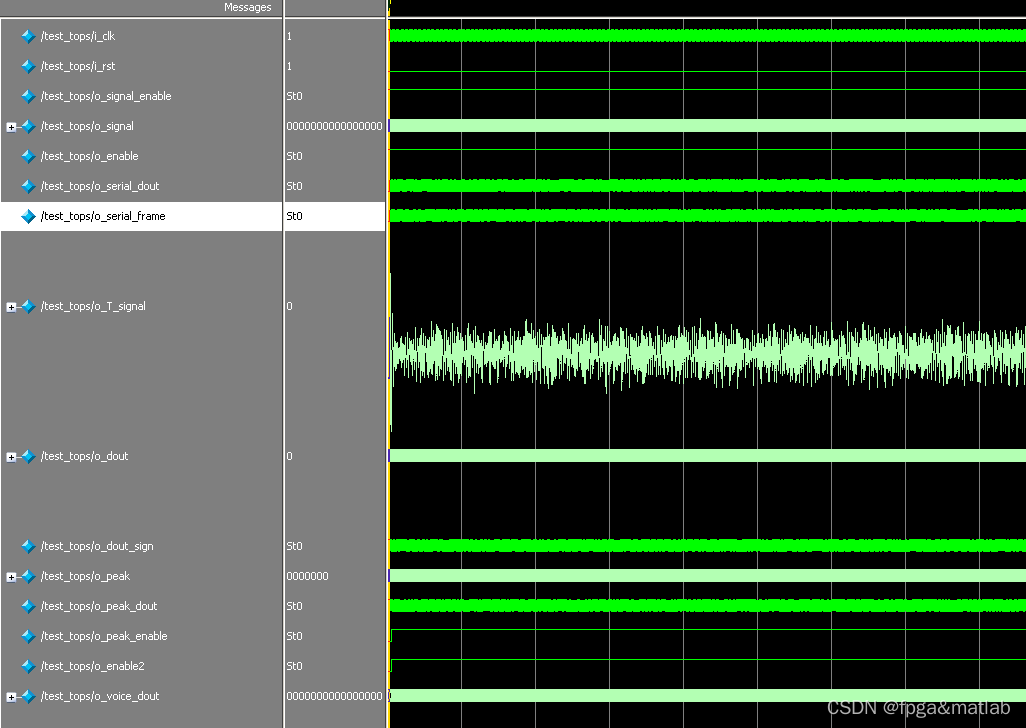

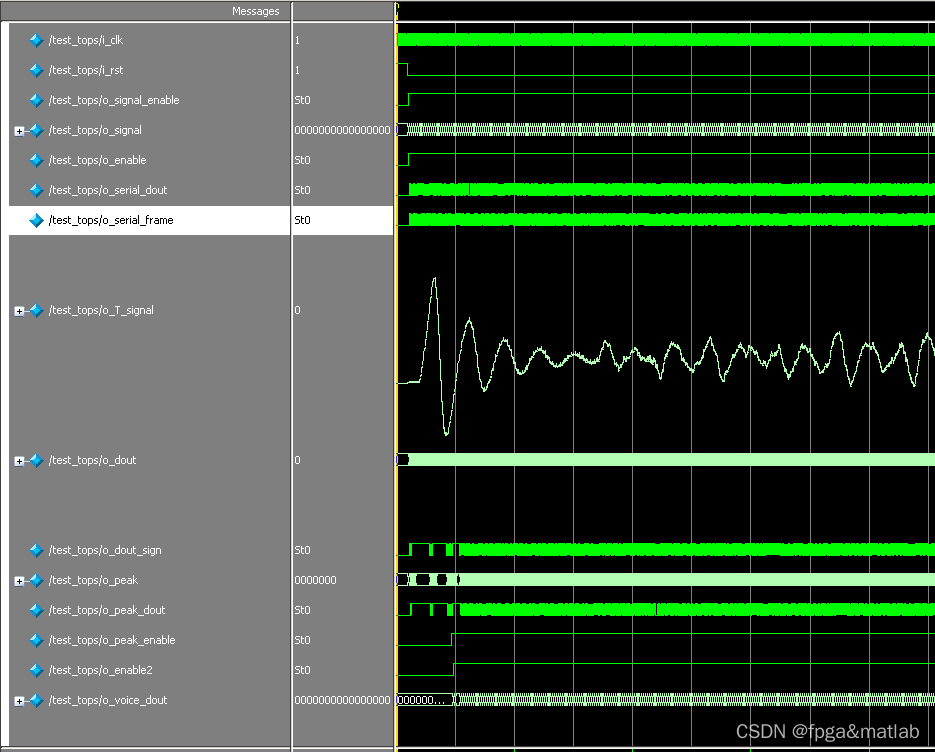

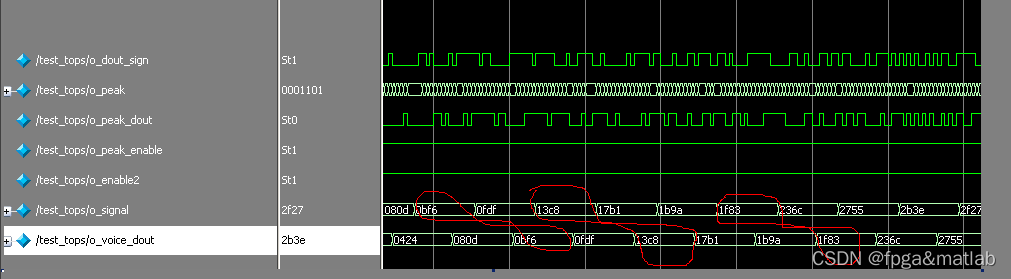

仿真结果如下所示:

其顶层的文件的管脚为:

| 1 |

i_clk |

系统时钟,就是接到硬件板子上的晶振位置。 |

| 2 |

i_rst |

系统复位,随便接到板子上的key数字按键上。 |

| 3 |

o_signal_enable |

测试并行信号的产生使能信号,不用接板子, |

| 4 |

o_signal |

测试并行信号,这个信号为了验证,你可以接signaltapII上 |

| 5 |

o_enable |

加密模块的使能信号,不用接板子 |

| 6 |

o_serial_dout |

串行输出,接板子上的测试脚或者signaltapII上 |

| 7 |

o_serial_frame |

串行信号组帧输出,接板子上的测试脚或者signaltapII上 |

| 8 |

o_T_signal |

加密输出,这个信号为了验证,你可以接signaltapII上 |

| 9 |

o_dout |

解密输出,可以接signaltapII上 |

| 10 |

o_dout_sign |

解密输出信号的符号判决,接板子上的测试脚或者signaltapII上 |

| 11 |

o_peak |

搜帧模块的相关峰输出,不用接板子 |

| 12 |

o_peak_enable, |

搜帧模块的使能输出,不用接板子 |

| 13 |

o_peak_dout |

搜帧模块的数据输出,接板子上的测试脚或者signaltapII上 |

| 14 |

o_enable2 |

最后串并转化的使能,不用接板子 |

| 15 |

o_voice_dout |

最后串并转化的数据输出,接板子上的测试脚或者signaltapII上 |

5.参考文献

[1]马在光, 吴纯英, 丘水生. 混沌同步和混沌通信研究的新进展与新尝试[J]. 电波科学学报, 2002, 17(3):8.

A01-53

6.完整源码获得方式

方式1:微信或者QQ联系博主

方式2:订阅MATLAB/FPGA教程,免费获得教程案例以及任意2份完整源码